先来看一个实例。

例4.1:

图4.1 模块的基本结构

这是我们学习的第二个Verilog HDL程序。在这个程序里,我们将学习到模块的基本结构。Verilog的每个基本设计单元都是单独的一个模块。在上面这个例子里,我们要设计一个模块,首先就要写上模块module(第1行),然后加几个回车空几行,再写下结束模块end module(第7行)。每一行代码的最前面的数字就是行号,行号是为了便于叙述而添加,在真实的编辑程序的时候,程序员不需要写入行号。module和end module是一对配对,表示在其间的部分是用来描述一个模块。

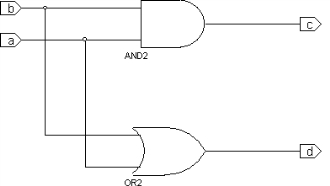

图4.2 综合的结果

在第1行module之后的block是这个模块的名字。这个名字可以随便取,一般按照器件要实现的功能来取。模块名的后面是一对括号,括号里分别把这个模块的输入输出端口列了出来。(https://www.xing528.com)

第2行,定义了a和b端口都是输入端口。不同的端口之间用逗号隔开。

第3行,定义了c和d端口都是输出端口。

图4.1就是把它看做一个黑盒子的端口示意图。

第5行,把a和b的值相与,其结果赋值给c端口。我们用assign来实现这里的赋值。大家先这么记着就好。

第6行,把a和b的值相或,其结果赋值给d端口。

对这个程序进行综合,我们得到了如上图所示的电路。

大家在上机做练习的时候,通常容易犯一些错误,导致程序的源代码语法检查未通过。比如在编写源代码的时候,所有的逗号都应该是英文的逗号,而不是中文的逗号;比如括号都应该是英文的括号;比如在每一个语句的结束时该在末尾写上分号。前面这些信息我们在之前的第一个模块已经叙述过一遍,希望大家牢记,并在编写、调试程序的过程中注意。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。