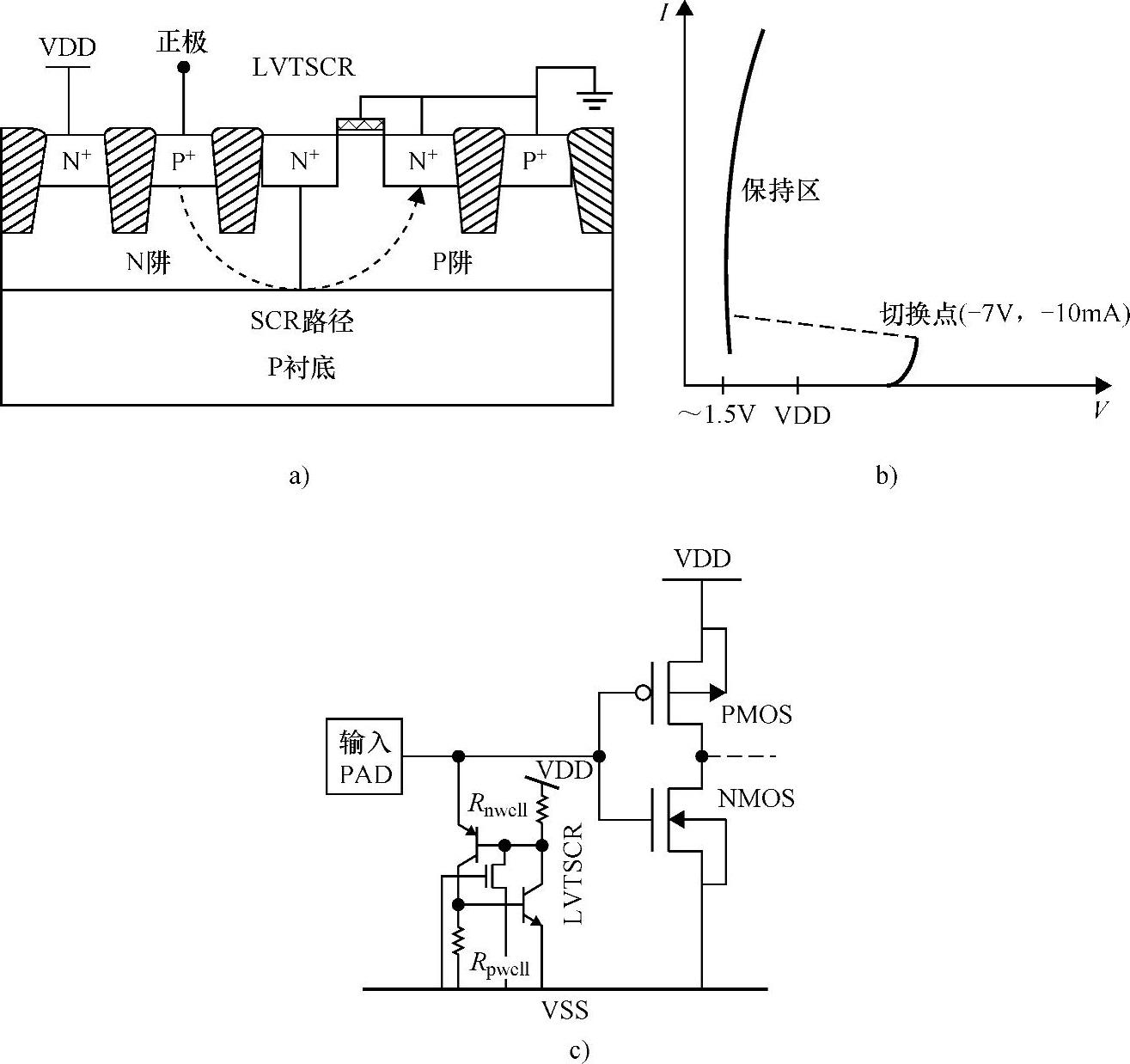

图5-26 a)CMOS工艺实现的低压触发SCR(LVTSCR)器件结构 b)0.25μmCMOS工艺LVTSCR的I-V特性 c)采用LVTSCR器件的输入ESD保护电路

低压触发SCR[82,85] 为了更有效地保护输入甚至是输出级,开发出了一种低压触发SCR(LVTSCR)。LVTSCR的器件结构如图5-26a所示,0.25μm工艺下LVTSCR的I-V特性如图5-26b所示。采用LVTSCR器件作ESD保护电路的实例如图5-26c所示。在某些应用中,LVTSCR的N阱被连接到输入压焊点。

LVTSCR的开关电压(约7V)对应于插入到LSCR结构中的短沟NMOS器件的漏击穿或穿通电压,而不是LSCR器件的开关电压(22V)。有这么低开关电压的LVTSCR就能给CMOS IC输入或输出级提供有效的ESD保护,而不需要第二级ESD保护电路。因此使用LVTSCR的ESD保护电路的总版图面积将会大大节省。此外,为了能给CMOS IC输入或输出级的PMOS和NMOS都提供保护,已发明了一个互补的LVTSCR结构[99]以提供更好的ESD保护。

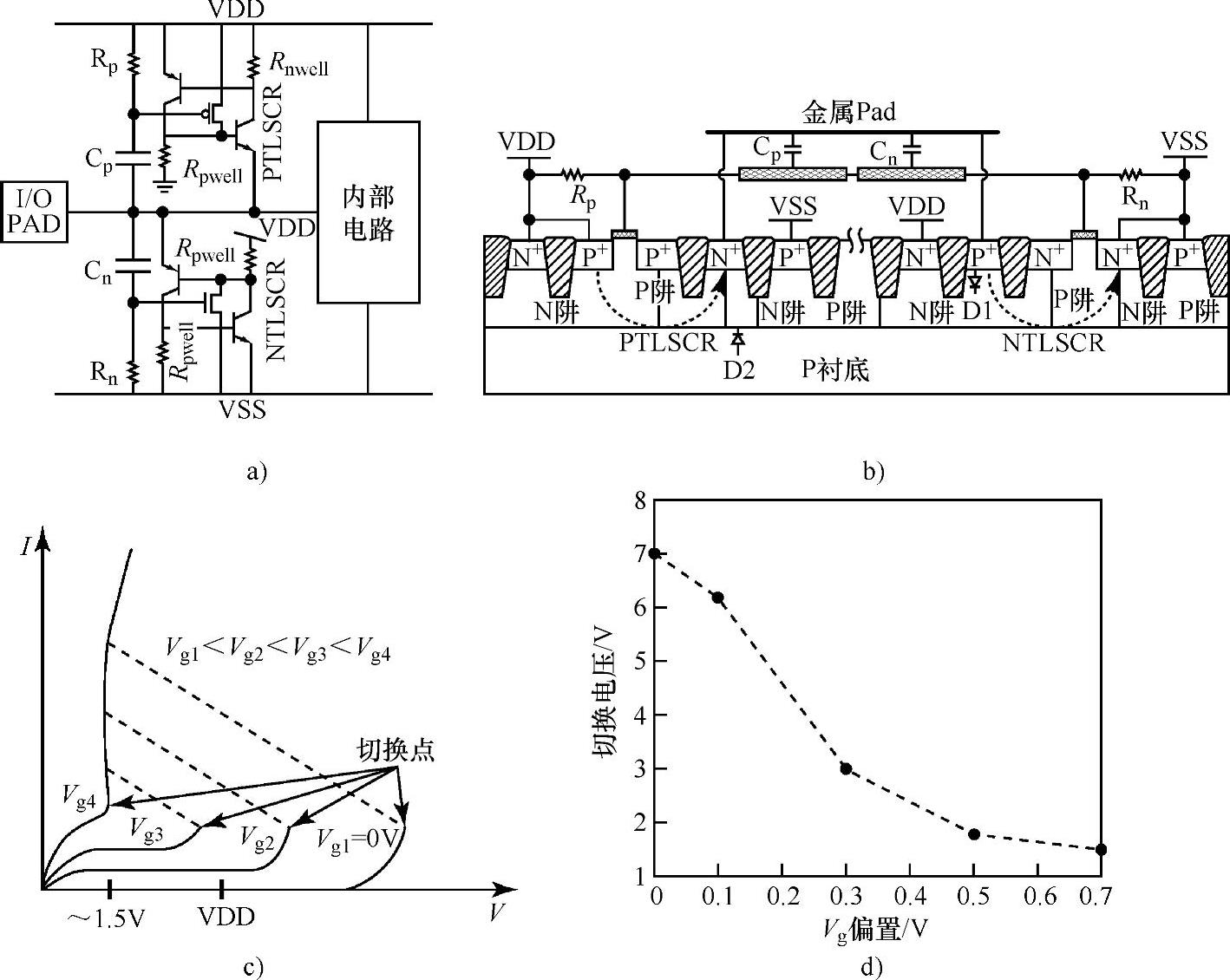

图5-27 a)采用栅耦合LVTSCR的ESD保护电路 b)CMOS工艺实现的栅耦合LVTSCR器件结构 c)0.25μm工艺栅耦合LVTSCR的I-V特性 d)SCR器件开关电压与NTLSCR器件栅偏置电压之间的关系

栅耦合LVTSCR[86] 为了有效保护深亚微米CMOS工艺中的超薄栅氧,栅耦合技术被用来进一步减小LVTSCR的开关电压,而不涉及雪崩击穿机制。采用互补栅耦合LVTSCR器件[NMOS触发LSCR(NTLSCR)和PMOS触发LSCR(PTLSCR)]的输入或输出压焊点的ESD保护电路如图5-27a所示。互补栅耦合LVTSCR的器件结构如图5-27b所示,采用0.25μm工艺的栅耦合LVTSCR的I-V特性如图5-27c所示。SCR器件的开关电压与NTLSCR器件的栅偏置电压之间的关系如图5-27d所示。图5-27c中的电容(Cn和Cp)值必须设计合理,以保证在电路正常工作条件下耦合的电压小于NMOS/PMOS的阈值电压,而在受到ESD作用的条件下耦合电压则应该大于NMOS/PMOS的阈值电压[20]。栅耦合NTLSCR(PTLSCR)的开关电压可以通过SCR器件结构中的短沟NMOS(PMOS)栅上的耦合电压来调整。在LVTSCR中,短沟NMOS/PMOS栅上较高的耦合电压会导致LVTSCR较低的开关电压。因此,栅耦合LVTSCR器件能快速的泄放ESD电流以更有效地保护输入或输出级的超薄栅氧。

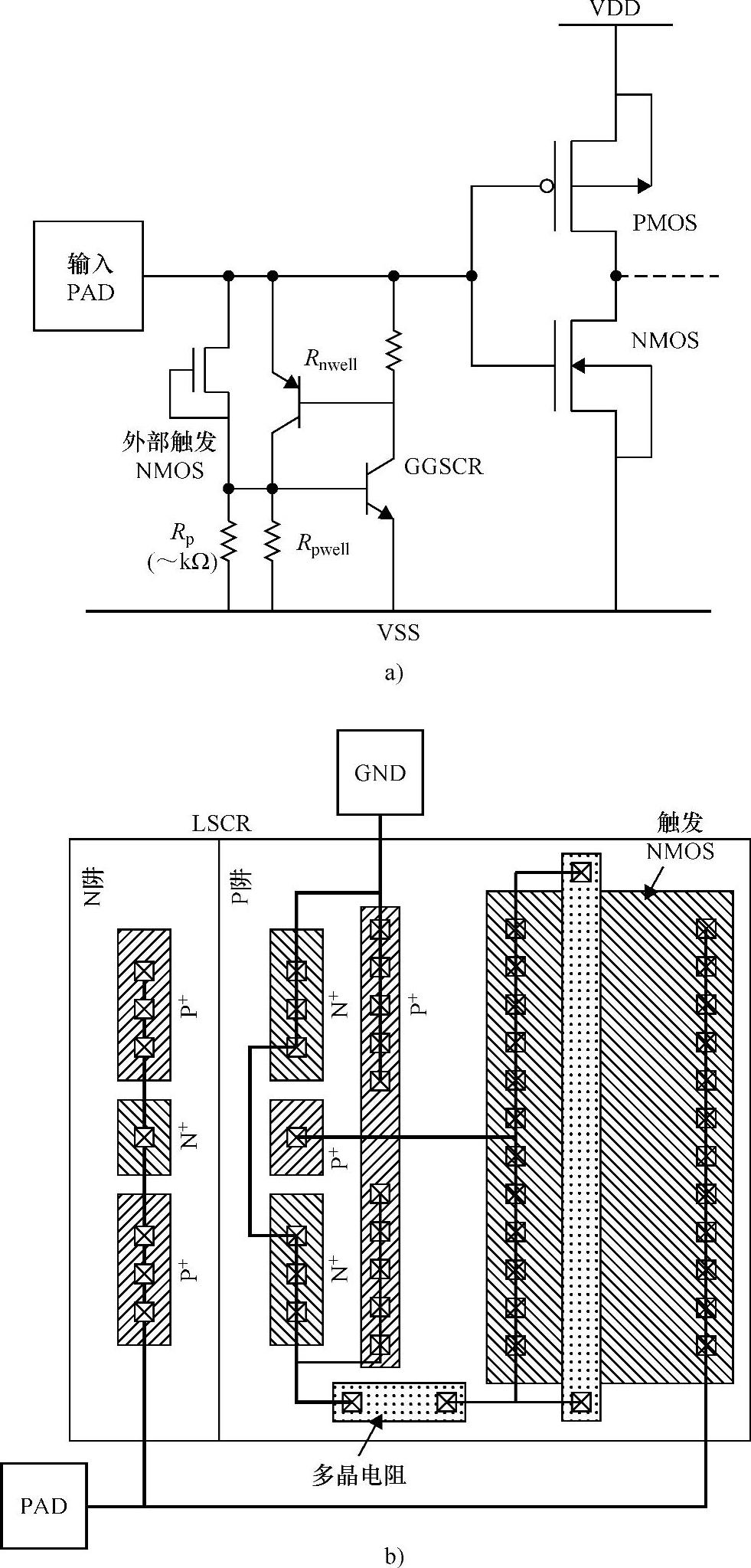

栅接地NMOS触发SCR[88,89] 采用栅接地NMOS触发的SCR是片上ESD保护电路的另一个选择。一个类似于GGNMOS结构的NMOS晶体管被用作一个外部触发器件以触发开启GGSCR。与LVTSCR相比,GGSCR中的外部触发NMOS的漏极被直接耦合到压焊点,而它的栅和源被耦合到P衬底(NPN的基极)。一个使用GGSCR器件作为输入ESD保护电路的实例如图5-28a所示。图5-28b所示为GGSCR版图的俯视图[105]。当ESD电压被加到图5-28a所示的I/O压焊点时,外部触发NMOS将进入雪崩击穿状态并开始将触发电流注入到P衬底和多晶电阻。只要NPN的基极电压大于0.7V,GGSCR将触发开启。图5-28b中多晶电阻用来控制触发电流和保持电流,并阻止GGSCR的误触发。实验结果表明,与阳极到阴极间距较大的LVTSCR相比,阳极到阴极间距较小的GGSCR具有较低的保持电压、较高的It2、更好的dV/dt触发能力和较快的开启速度。

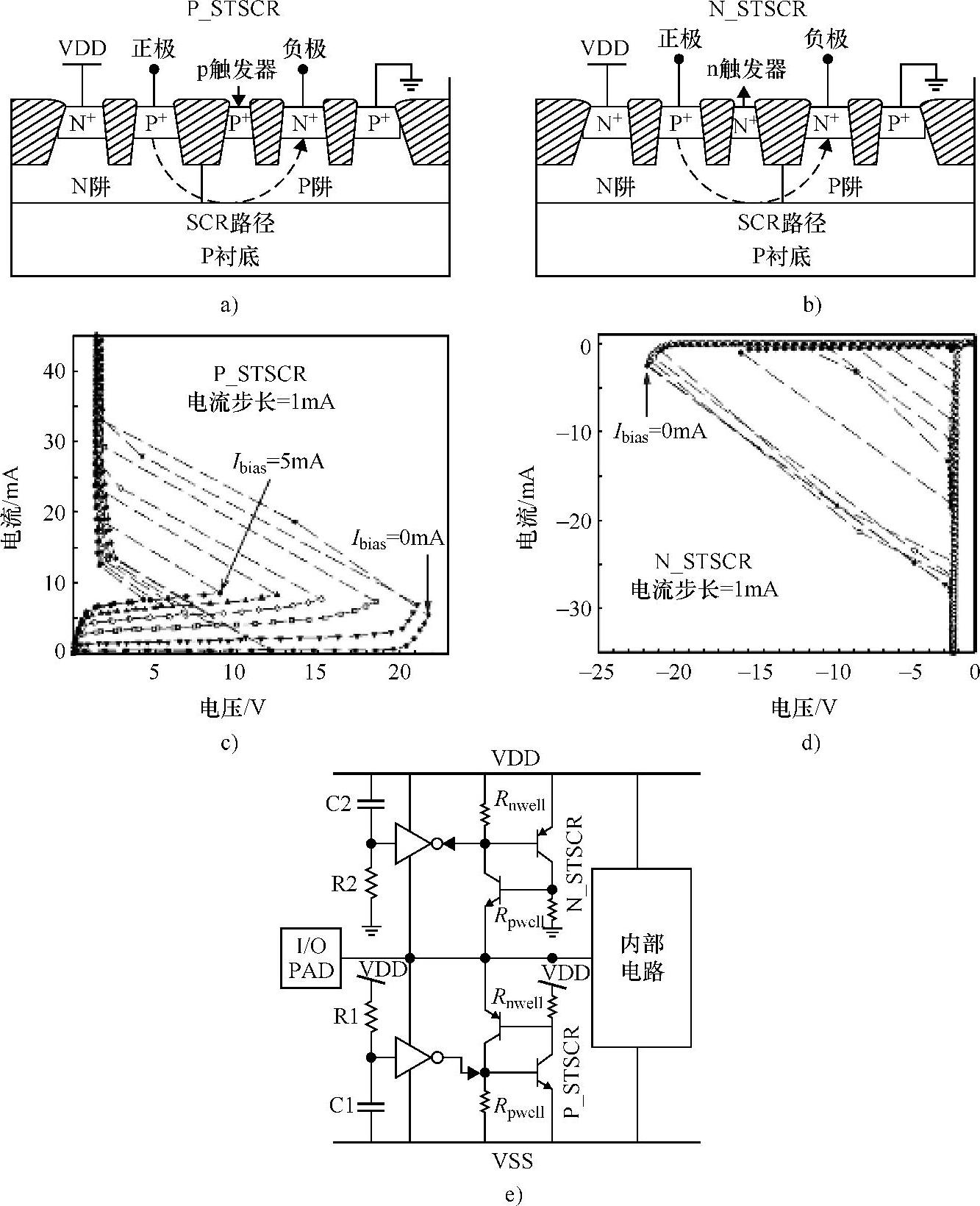

衬底触发的SCR[90,91] SCR器件的开启机制本质上是电流触发事件。当电流被加到SCR器件的基极或衬底时,它能被快速地触发进入闩锁状态。有报道说已经开发出了使用衬底触发技术的P型衬底触发的SCR(P_STSCR)和N型衬底触发的SCR(N_STSCR)器件实现ESD保护。P_STSCR和N_STSCR的器件结构分别如图5-29a和图5-29b所示。与传统的横向SCR器件结构相比,这种结构在P_STSCR器件结构的P阱中插入了一个附加的P+扩散,并且将其接出作为P_STSCR器件的P触发器节点。对N_STSCR,在N_STSCR器件结构的N阱中插入了一个附加的N+扩散,并且将其接出作为N_STSCR器件的N触发器节点。P_STSCR和N_STSCR的I-V特性分别如图5-29c和图5-29d所示。随着衬底/阱触发电流的增加,P_STSCR/N_STSCR器件的开关电压可以被减小到它的保持电压。在0.25μm工艺中,STSCR的开启时间在上升时间为10ns的5V电压脉冲下会减小到约10ns。开关电压较低的STSCR器件可以更快地把ESD电压钳位到较低的电压水平,以充分保护输入级的超薄栅氧免受ESD过应力的损伤。使用P_STSCR和N_STSCR器件的输入或输出压焊点的ESD保护电路如图5-29e所示。在有采用VDD和VSS电源的电路在正常工作条件下,inv_1(inv_2)的输入被偏置到VDD(VSS)。因此,由于inv_1(inv_2)中NMOS(PMOS)的开启,不管输入信号是逻辑高电平还是逻辑低电平,inv_1(inv_2)的输出都被偏置到VSS(VDD)。P_STSCR(N_STSCR)的p触发器(n触发器)节点被inv_1(inv_2)的输出偏置到VSS(VDD)。所以,在电路正常工作情况下,P_STSCR和

图5-28 a)采用GGSCR器件的输入ESD保护电路 b)CMOS工艺实现的GGSCR版图俯视图(https://www.xing528.com)

N_STSCR器件可以保证处于关断状态。在图5-29e所示的正脉冲加于VSS(PS)的ESD作用条件下(VSS接地而VDD悬空),inv_1的输入最初处于零电平悬空状态;因此,由于压焊点上的正ESD电压作用,inv_1的PMOS将导通。所以inv_1的输出被ESD能量充电,产生流向P_STSCR器件P触发器节点的触发电流。因此,P_STSCR器件被触发开启,ESD电流通过P_STSCR器件从I/O压焊点泄放到

图5-29 a)P型衬底触发的SCR(P_STSCR)器件结构 b)N型衬底触发的SCR(N_STSCR)器件结构 c)采用0.25μmCMOS工艺的P_STSCR的I—V特性 d)采用0.25μmCMOS工艺的N_STSCR的I-V特性e)采用P_STSCR和N_STSCR实现的I/O压焊点ESD保护电路

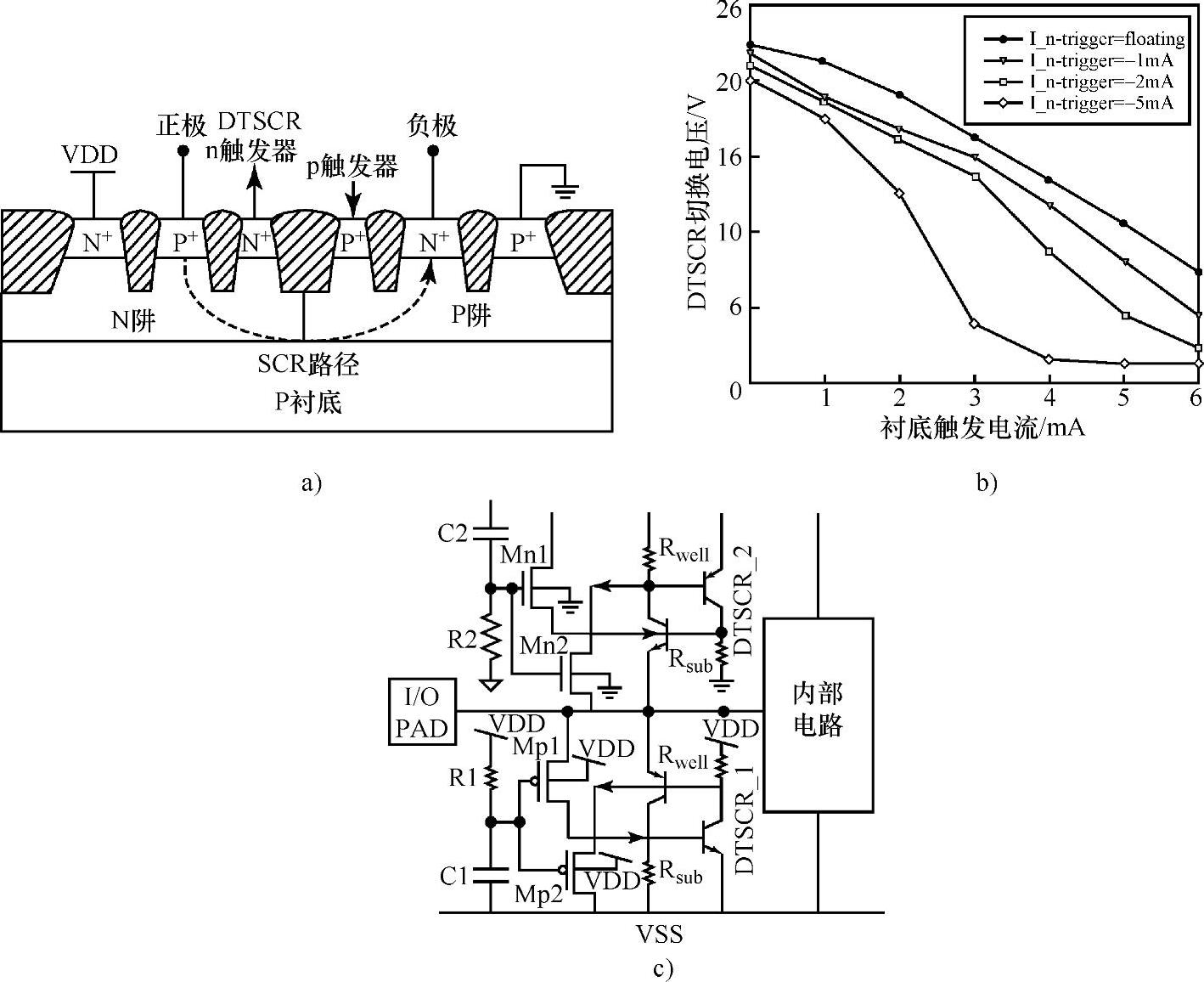

图5-30 a)双触发SCR(DTSCR)的器件结构 b)在不同N阱触发电流下,采用0.25μmCMOS工艺的DTSCR器件维持电压与衬底触发电流之间的关系 c)采用DTSCR器件的I/O压焊点ESD保护电路

接地的VSS引脚。在负脉冲加于VSS(ND)模式下的ESD作用情况下(VDD接地而VSS悬空),N_STSCR的工作原理类似。另外,还发明了一种采用哑元栅结构的STSCR器件[108,109]可以进一步减小开关电压并且提高STSCR的开启速度。采用哑元栅结构的STSCR的双极电流增益大于采用浅沟槽隔离技术(STI)结构的STSCR的双极电流增益,因此采用哑元栅结构的STSCR的触发效率优于采用STI的STSCR。

双触发SCR[94] 进一步减小LSCR器件开关电压、更有效提高LSCR开启速度的另一种方式是双触发技术。双触发SCR(Double-Triggered SCR,DTSCR)的器件结构如图5-30a所示。在DTSCR器件结构的P阱和N阱中又添加了P+和N+扩散,并且被接出作为DTSCR器件的P触发器和N触发器的节点。图5-30b汇总了在不同的N阱触发电流下,DTSCR器件的开关电压与衬底触发电流之间的关系。如果衬底和N阱触发电流被分别同步加到p触发器和n触发器的节点,DTSCR器件的开关电压能被有效减小到较低的电压水平。采用DTSCR器件实现的I/O ESD保护电路如图5-30c所示。基于RC延迟原理,在PS(ND)ESD作用条件下,衬底和N阱触发电流可以分别由Mp1和Mp2(Mn1和Mn2)产生。因此,图5-30c所示的双触发电流的DTSCR可以被更快的触发以泄放ESD电流。在采用VDD和VSS电源的电路正常工作条件下,Mp1和Mp2(Mn1和Mn2)的栅通过电阻R1(R2)偏置到VDD(VSS)。因此,无论输入信号为高电平或低电平,Mp1、Mp2、Mn1和Mn2都处于关断状态。DTSCR器件的p触发器(n触发器)节点通过寄生电阻Rsub(Rwell)保持在VSS(VDD),所以在电路正常工作条件下,可以确保这种DTSCR处于关断状态。根据0.25μmCMOS工艺的试验结果,当一个0V到5V的电压脉冲被加到DTSCR的阳极时,如果DTSCR的p触发器节点上有1.5V的正电压脉冲,它的开启时间约为37ns。但是当一个-5V的负电压脉冲被加到它的n触发器的节点时,DTSCR的开启时间可以进一步减小到约12ns。SCR器件中被用来阻挡STI的假栅结构可以被应用到DTSCR结构中进一步减小开关电压、更加有效地提高DTSCR器件的开启速度。

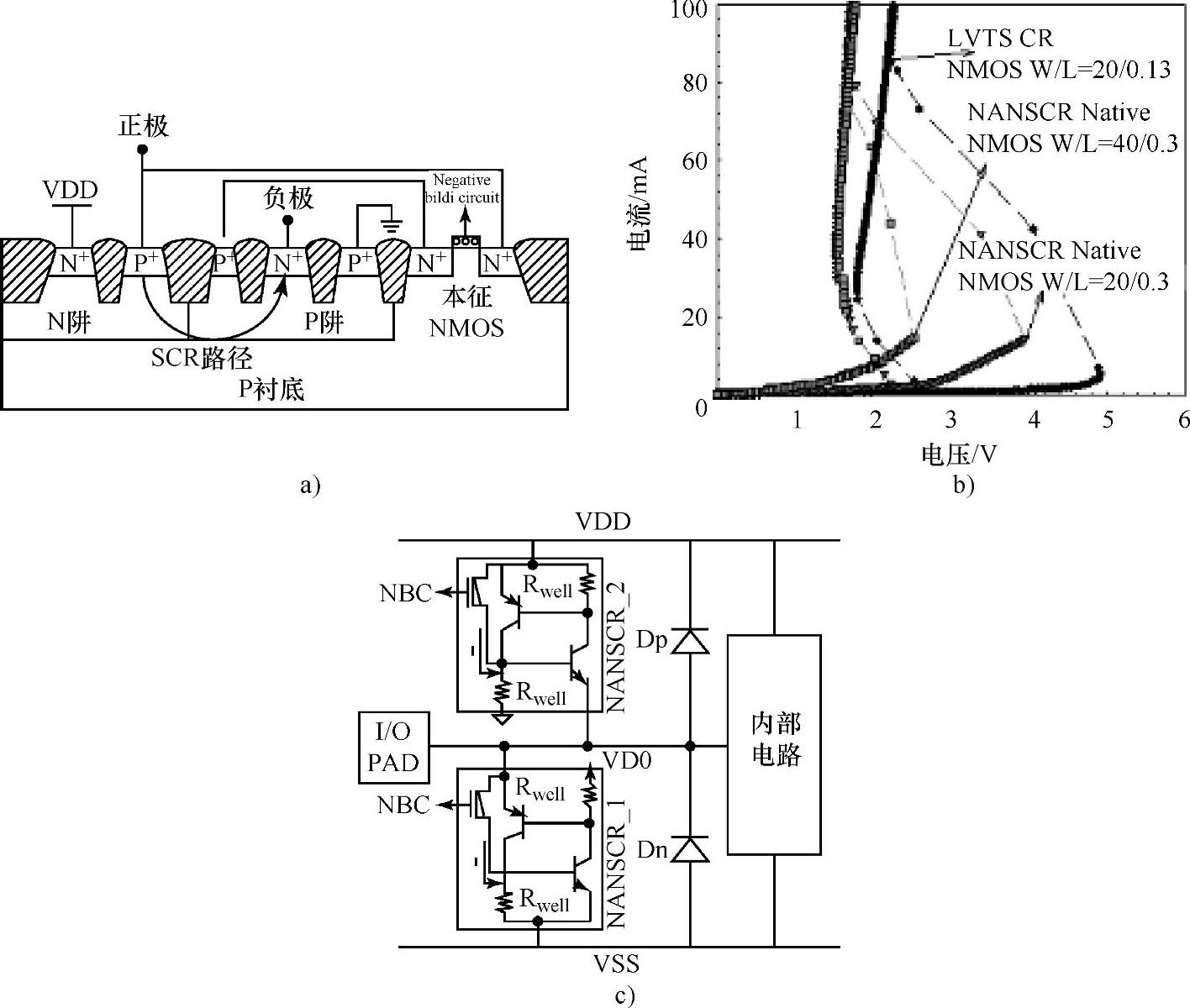

本征NMOS触发SCR[95] 本征NMOS是直接在亚0.25μmCMOS工艺中的p型轻掺杂衬底上形成,而通常的NMOS(PMOS)则是在采用p型衬底的双阱工艺中的重掺杂P阱(N阱)中形成。本征NMOS和横向SCR可以被结合在一起形成一种新的ESD保护器件,称为本征NMOS触发SCR(Native-NMOS-triggered SCR,NANSCR)。这种器件的优势是具有更低的开关电压和更快的开启速度。NANSCR的器件结构如图5-31a所示。本征NMOS的栅被连接到了负偏压电路(Negative Bias Circuit,NBC)[96],使其在电路正常工作条件下关断NANSCR。NANSCR与LVTSCR的DC I-V曲线对比如图5-31b所示。在0.13μm金属硅化物CMOS工艺下,沟道宽度相同、沟道长度为0.3μm的NANSCR的开关电压(约4V)小于沟道长度为0.13μm的LVTSCR的开关电压(约5V)。采用衬底触发技术,NANSCR的开关电压可以随着本征NMOS的W/L比的增加而进一步下降。采用NANSCR器件的输入或输出压焊点的ESD保护电路如图5-31c所示。在电路正常工作条件下,所有NANSCR器件中的本征NMOS的栅被同一个NBC偏置,使NANSCR器件关断。所以NANSCR器件NANSCR_1和NANSCR_2将不会干扰I/O电路的功能。在PS模式ESD作用条件下,NANSCR_1中的本征NMOS栅悬空,已经开启的本征NMOS产生的衬底触发电流快速将NANSCR_1触发开启。所以正ESD电流可以从I/O压焊点通过NANSCR_1快速泄放到接地的VSS。根据0.13μm工艺的实验结果,NAN-SCR的开启速度快于LVTSCR。而且,NANSCR承受的CDM ESD级别(5V/μm2)高于LVTSCR(2.33V/μm2),因此它更适合用于保护纳米技术中的超薄栅氧。

图5-31 a)本征NMOS触发SCR(NANSCR)的器件结构 b)0.13μm工艺实现的NANSCR与LVTSCR的I-V特性比较 c)采用NANSCR器件的ESD保护电路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。