加载和存储指令用于完成数据的读入和保存。加载指令是将存储器内容或立即数赋给目的寄存器;存储指令是把源操作数或立即数存入存储器或寄存器。在计算机的工作过程中,存在着大量数据存取操作,数据的加载和存储指令在应用程序中占有很大比例。TMS320C54x为用户提供了非常灵活、方便的数据加载和存储指令,按照功能的不同可以将加载和存储指令分为8组:加载指令、存储指令、条件存储指令、并行加载和存储指令、并行加载和乘法指令、并行存储和加/减法指令、并行存储和乘法指令以及其他加载和存储指令。分别叙述如下。

1.加载指令

加载指令用于将数据存储单元内的值、立即数或源累加器的值装入目的累加器、临时寄存器等,也就是给目的累加器和临时寄存器等赋值。加载指令共有21条,见表4-32。

表4-32 加载指令

(续)

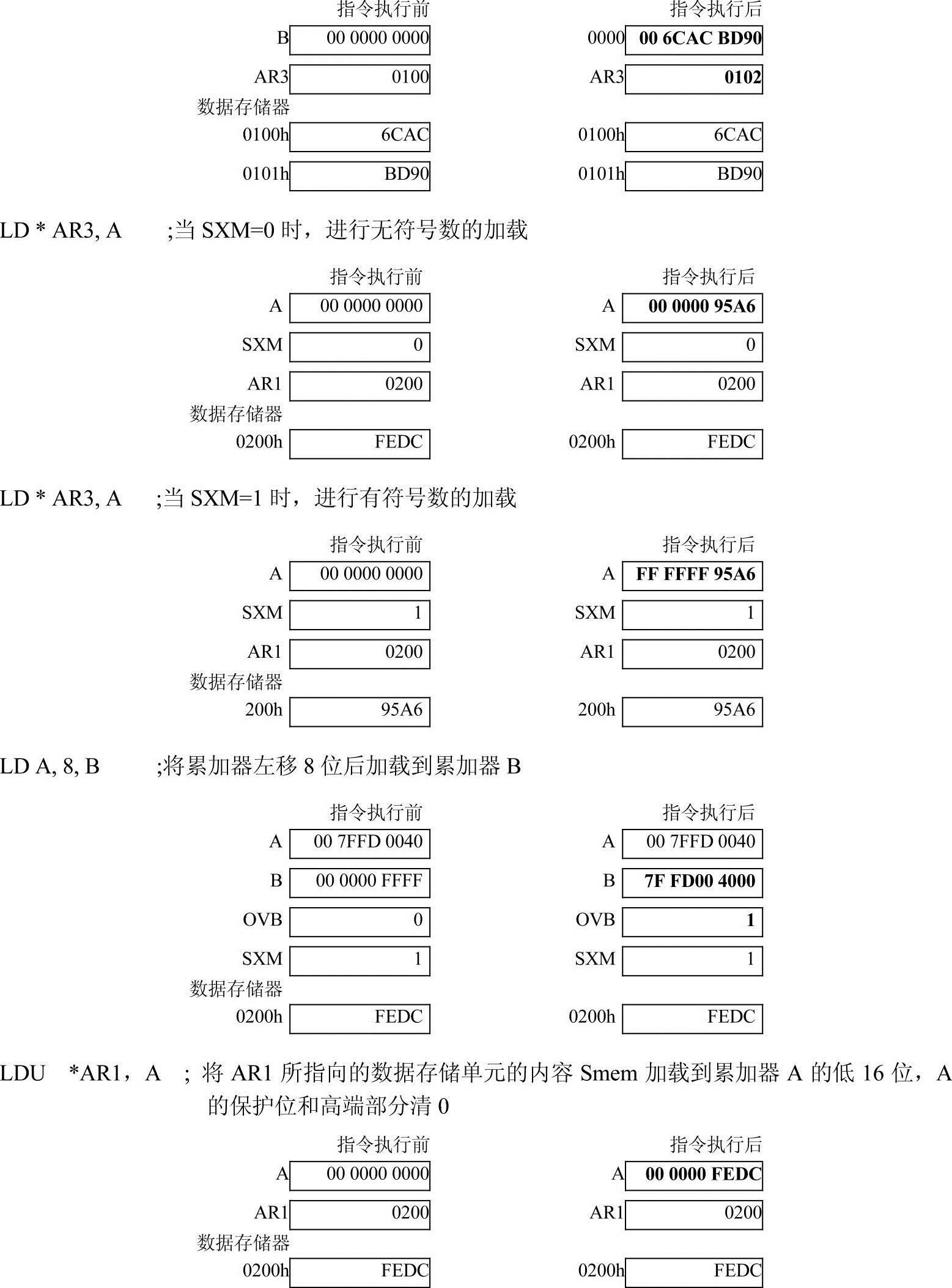

TMS320C54x提供的加载指令分别为DLD、LD、LDM、LDR、LDU和LTD。其中:

1)DLD指令将32位Lmem数值加载到dst中,ST1的C16位决定了指令的执行方式。若C16=0,指令以双精度模式执行,Lmem加载到dst中。若C16=1,指令以双16位模式执行,Lmem的高16位加载到dst的高24位,同时Lmem的低16位加载到dst的低16位。

2)以累加器A或B为目标操作数的LD指令是将数据存储器操作数或立即数K、lk或累加器A、B中的内容先移位或者不移位,然后传送到目标操作数A或B中去,而源操作数的内容不变。当标志位SXM=1时,进行有符号数的加载,否则,进行无符号数的加载;当加载指令中带有SHIFT或ARM移位时,OVM会影响指令的结果,且当操作的结果有溢出时,OVA或OVB被置1。

3)以暂存器T或ST0、ST1的DP、ASM及ARP字段为目标操作数的LD指令为状态寄存器的有关位赋值,多用于程序的初始化设计,指定直接寻址的数据页指针DP值,当前辅助寄存器指针ARP的值及移位位数ASM值等。这些指令不会影响其他的状态位,也不受任何控制位的影响。

4)LDM指令将存储器映射寄存器MMR中的值加载到dst中。无论DP的当前值或ARx的高9位为何值,都将有效地址的最高9位清0,以便限制在第0页内寻址。

5)LDR指令将Smem左移16位之后加载到累加器dst的31~16位。Smem值加上215进行舍入操作,dst的低15位(0~14位)清0,第15位置1。

6)LDU指令将Smem内容加载到累加器dst的低16位(15~0位),dst的保护位和高端部分(39~16位)清0。数据被当作无符号数,无论SXM如何取值,都不做符号扩展。

7)LTD指令将Smem的内容复制到T寄存器中,也复制到下一个数据单元中,Smem的内容保持不变。该指令用于实现数字信号处理的Z延迟。

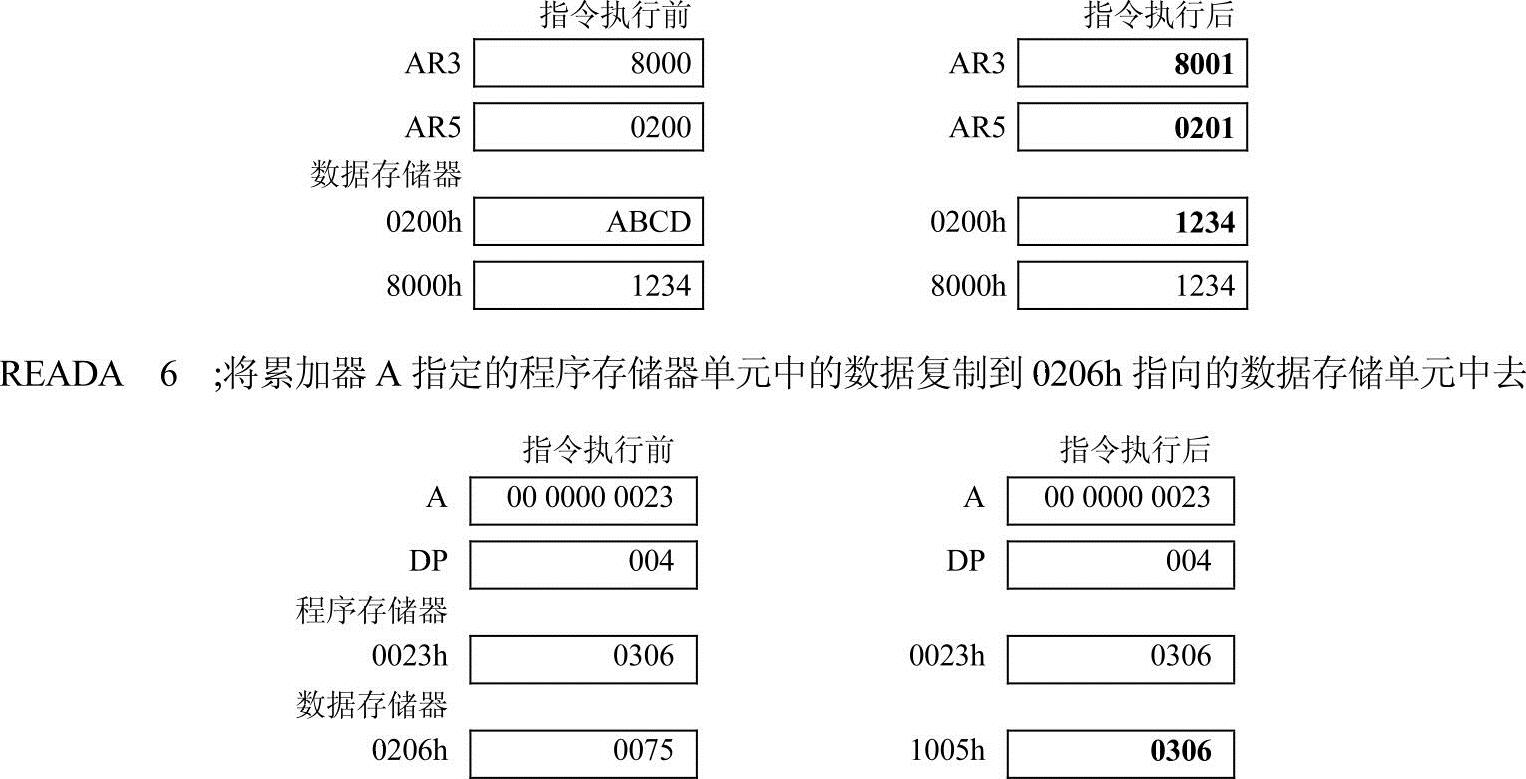

【例4-35】 加载指令示例。

2.存储指令

存储指令用于将源累加器、立即数或临时寄存器等的值保存到数据存储单元或存储映射寄存器。存储指令共有14条,见表4-33。

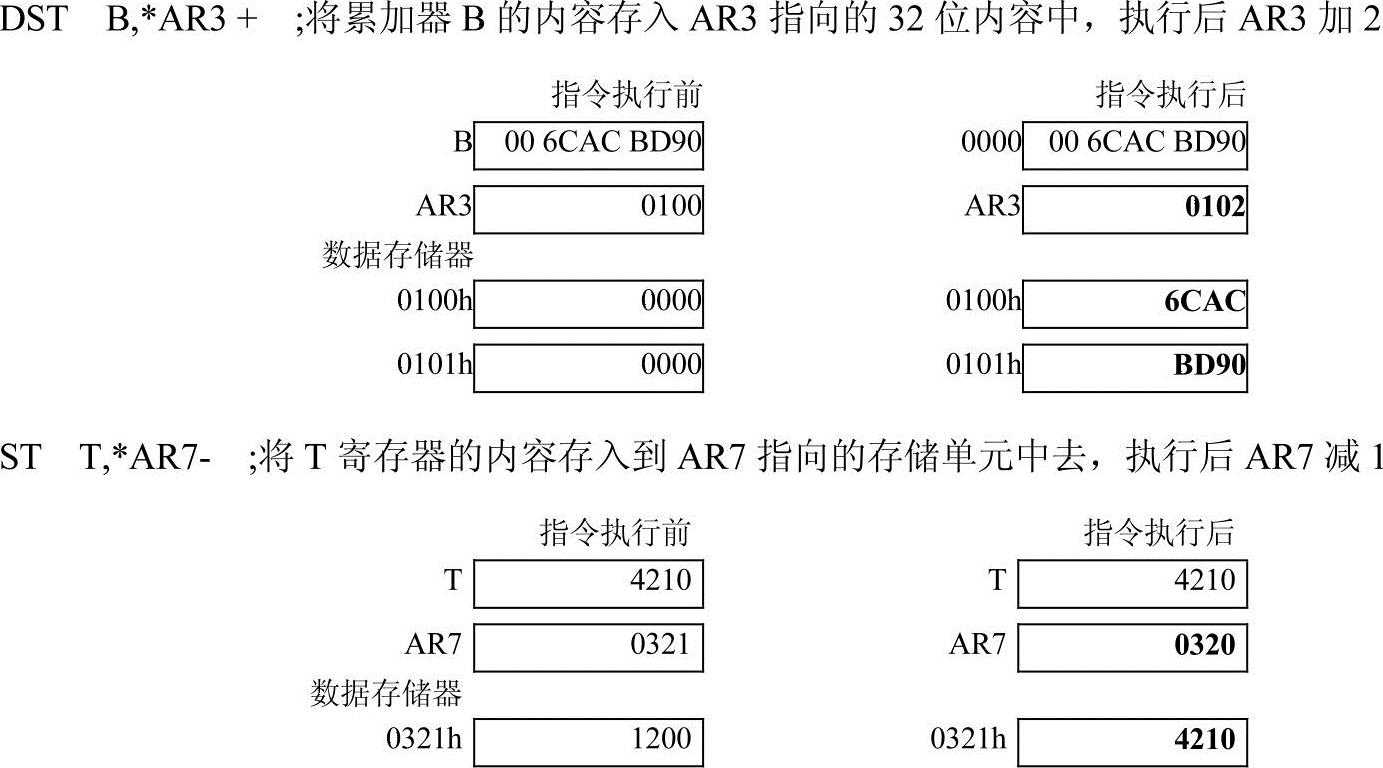

TMS320C54x提供的存储指令分别为DST、ST、STH、STL、STLM和STM。其中:

1)DST指令将src的内容存入32位的Lmem存储单元中。

2)ST指令将T寄存器、TRN寄存器或一个16位常数lk存入数据存储器的Smem中。

表4-33 存储指令

3)STH指令将src的高位部分(31~16位)存储到数据存储器Smem中。src存储之前需要左移,移位的位数由ASM、SHFT或者SHIFT决定,并且移位后的31~16位存储到数据存储器Smem或Xmem中。

4)STL指令将src的低位部分(15~0位)存储到数据存储器Smem中。操作数src需要左移,移位的位数由ASM、SHFT或SHIFT确定,移位后的15~0位存储到数据存储器Smem或Xmem中。如果移位的位数是正数,低位补0。

5)STLM指令将src的低位部分(15~0位)存储到存储器映射寄存器MMR中。无论当前辅助寄存器ARx的高9位或DP为何值,有效地址的高9位都被清0。

6)STM指令将16位常数存储到MMR或者数据页0的存储单元中,但不改变状态寄存器ST0的DP字段。

【例4-36】 存储指令示例。

3.条件存储指令

条件存储指令共有4条,见表4-34。

表4-34 条件存储指令

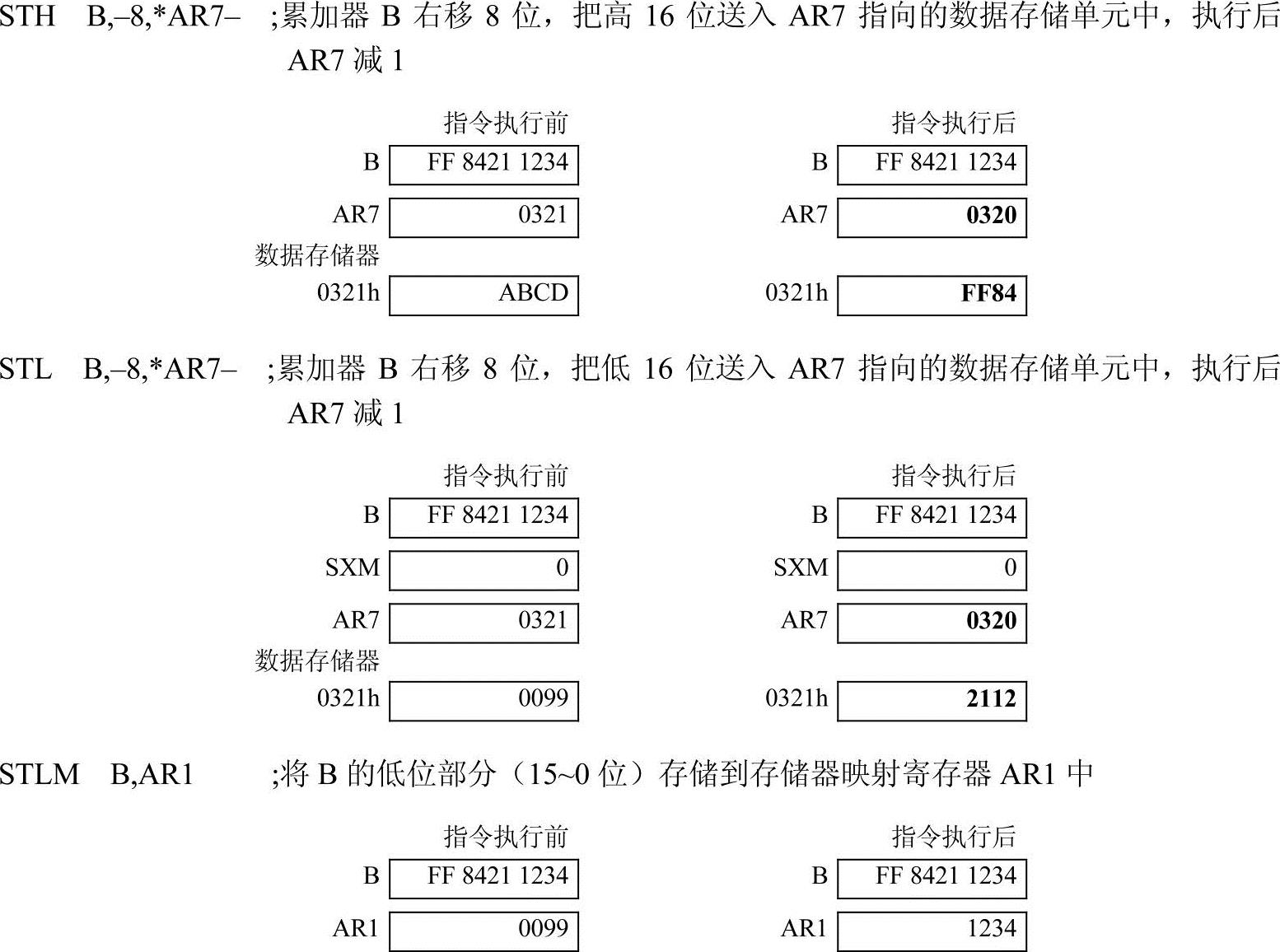

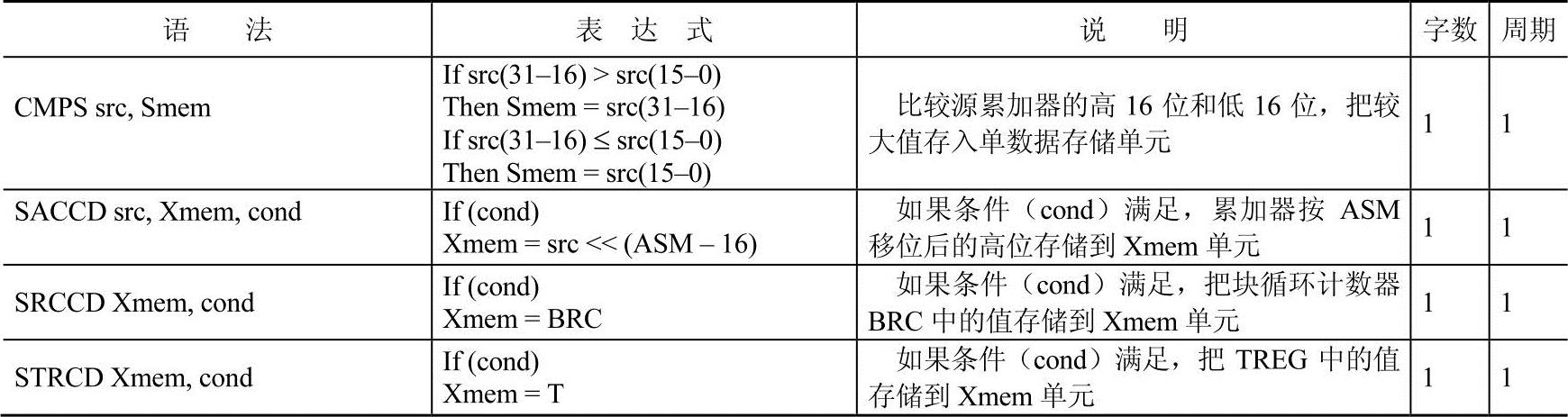

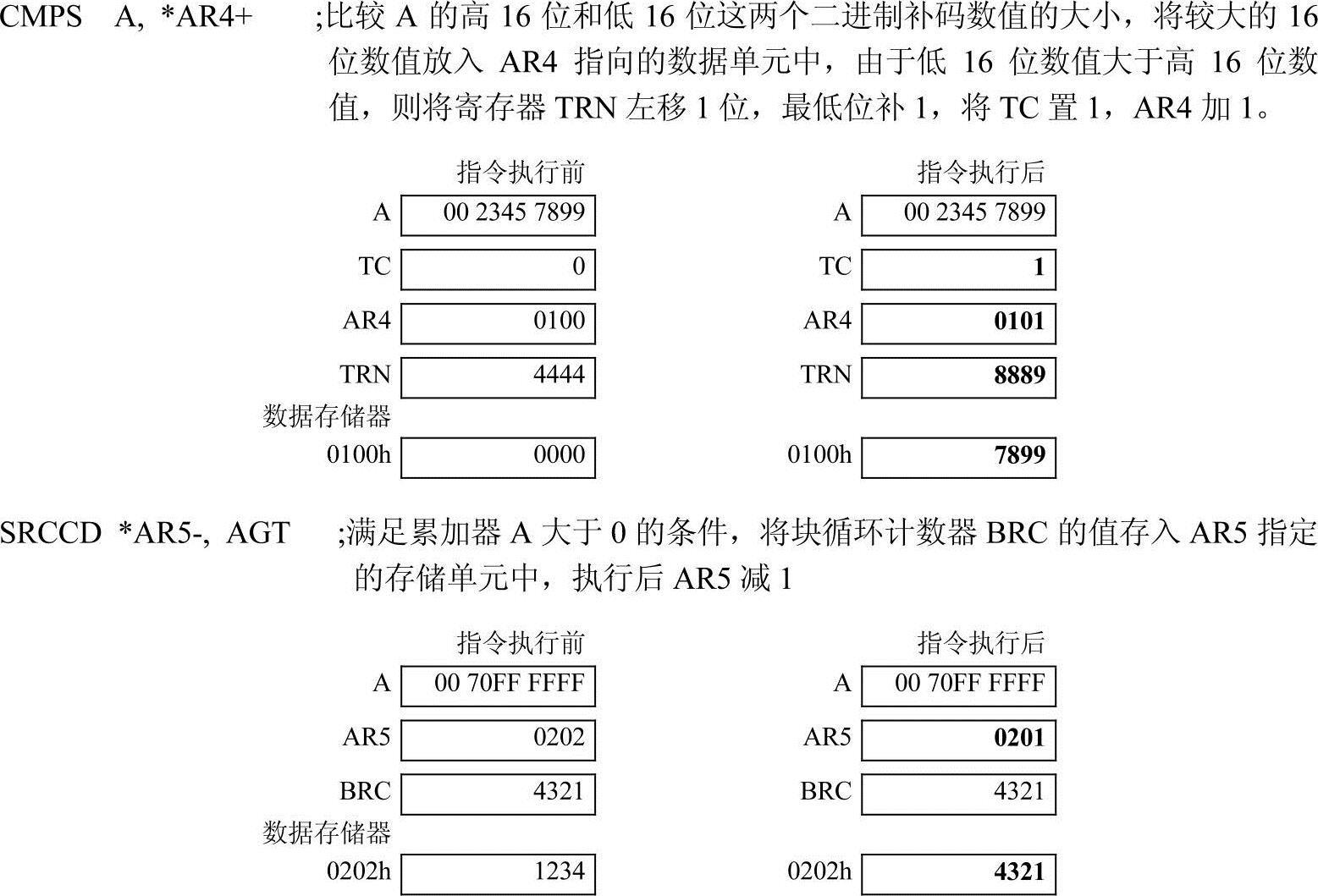

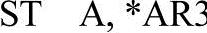

TMS320C54x提供的条件存储指令分别为CMPS、SACCD、SRCCD和STRCD。其中:

1)CMPS指令比较src的高16位和低16位这两个二进制补码数值的大小,将较大的16位数值放入Smem中。如果src中的高16位数值大,则将寄存器TRN左移1位,最低位补0,将TC清0;如果低16位数值大于或者等于高16位数值,则将寄存器TRN左移1位,最低位补1,将TC置1。

2)SACCD、SRCCD、STRCD指令如果满足指定的条件,分别为将src内容左移(ASM-16)位之后的值、块循环计数器BRC的值、T寄存器的值存入Xmem指定的存储单元,如果不满足条件,指令读入Xmem的值后不做改变,再写回Xmem中。

【例4-37】 条件存储指令示例。

4.并行加载和存储指令

并行操作指令包括并行加载和存储指令、并行加载和乘法指令、并行存储和加/减法指令、并行存储和乘法指令。并行操作指令的数据传输与各种运算同时进行,充分利用了TMS320C54x的流水线特性,代码和时间效率高。但这类指令的前后指令应注意流水线冲突问题。所有并行操作指令都是单字单周期指令,且都工作在累加器的高位,同时某些并行操作与ASM有关,在并行操作指令中只能采用间接寻址方式寻址Xmem或Ymem。

并行加载和存储指令共有两条,见表4-35。

表4-35 并行加载和存储指令

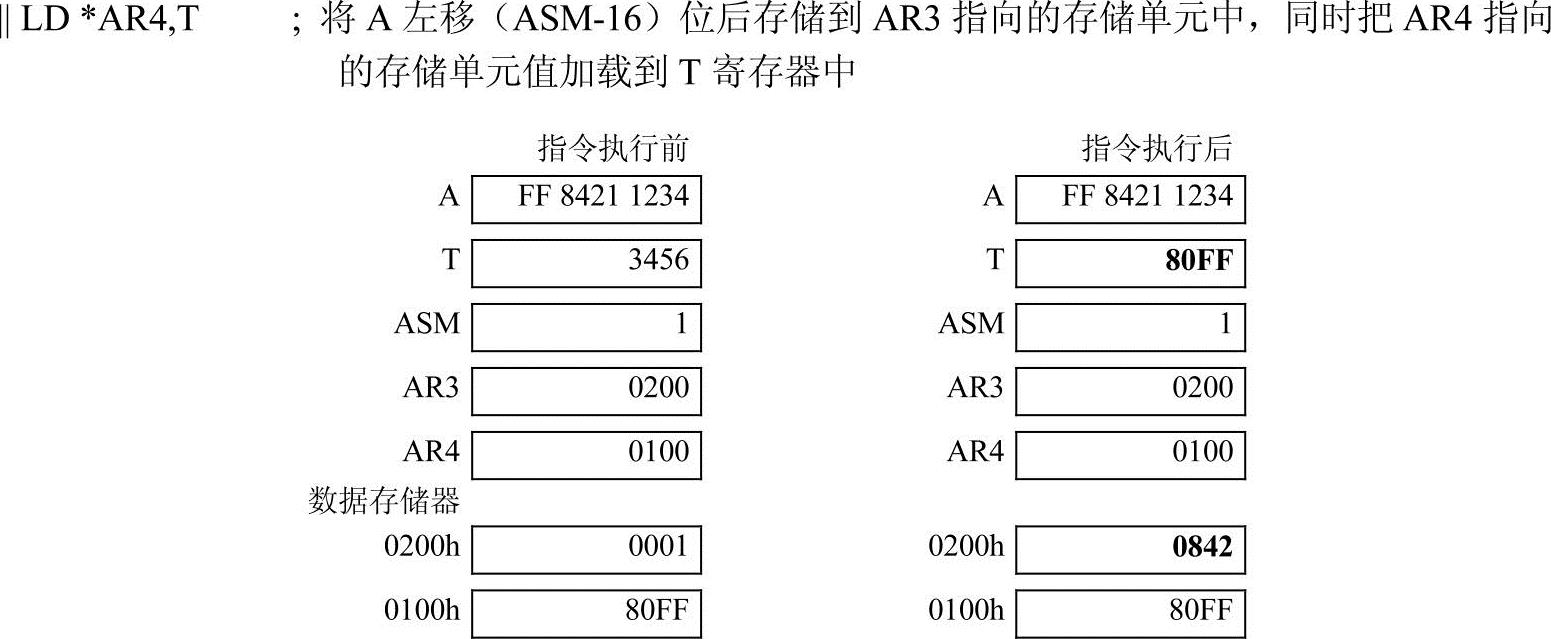

TMS320C54x提供的并行加载和存储指令ST||LD用于存储累加器内容,并行执行加载操作,该并行指令将src左移(ASM-16)位后存储到Ymem中,同时把16位的双数据存储器操作数Xmem值加载到dst或T寄存器中。如果src和dst为同一个累加器,则存储到Ymem中的值是指令执行前src的值,该指令受状态位OVM和ASM的影响,执行结果影响状态位C。(https://www.xing528.com)

【例4-38】 并行加载和存储指令示例。

5.并行加载和乘法指令

并行加载和乘法指令共有4条,见表4-36。

表4-36 并行加载和乘法指令

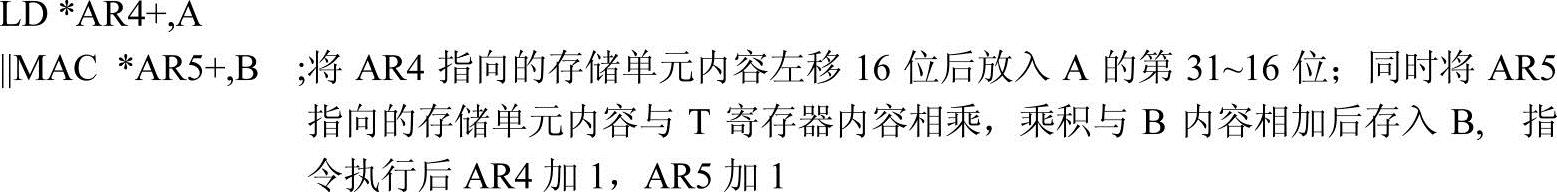

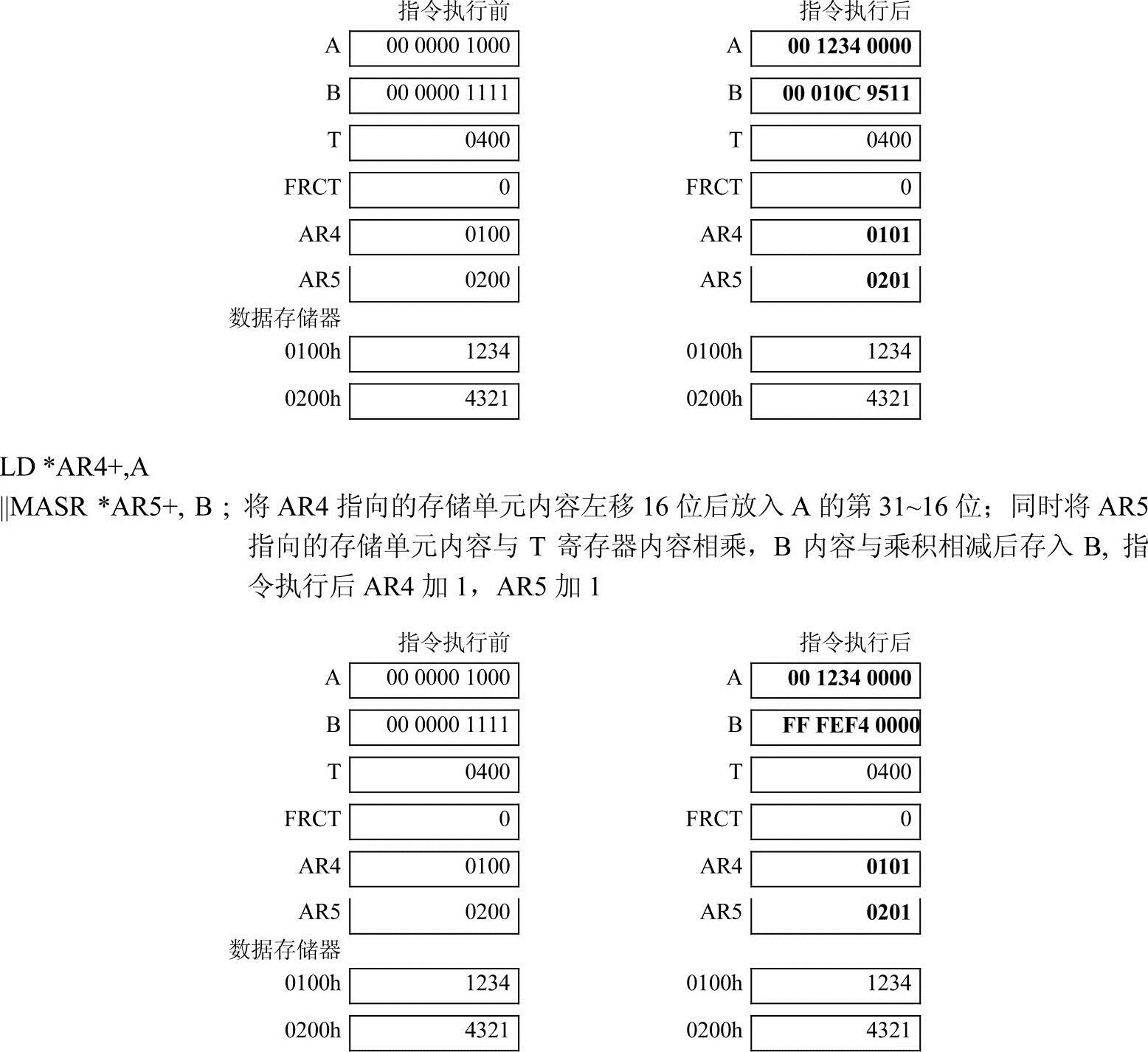

TMS320C54x提供的并行加载和乘法指令分别为LD||MAC[R]和LD||MAS[R],其中:

1)LD||MAC[R]指令用于加载累加器,同时并行地执行累加器的乘法(舍入操作可选),一方面将16位双数据存储器操作数Xmem左移16位后放入dst的第31~16位;同时另一个双数据存储器操作数Ymem与T寄存器内容相乘,乘积与dst_内容相加后存入dst_。如果使用了扩展名R,还需要对乘法累加结果进行凑整操作,方法是与215相加,将结果的第15~0位清0,存储到dst_。

2)LD||MAS[R]指令用于加载累加器,同时并行地执行乘减指令(舍入操作可选),一方面将16位双数据存储器操作数Xmem左移16位后放入dst的第31~16位;同时另一个双数据存储器操作数Ymem与T寄存器内容相乘,从dst_中减去该乘积后再存入dst_。如果使用了扩展名R,还需要对减法结果进行凑整操作,方法是与215相加,将结果的第15~0位清0,存储到dst_。

上述指令受状态位SXM、FRCT和OVM的影响,执行结果影响状态位OVdst_。

【例4-39】 并行加载和乘法指令示例。

6.并行存储和加/减法指令

并行存储和加/减法指令共有两条,见表4-37。

表4-37 并行存储和加/减法指令

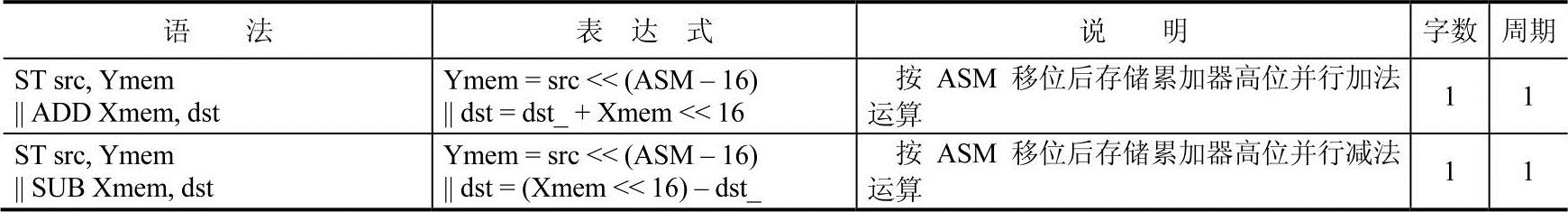

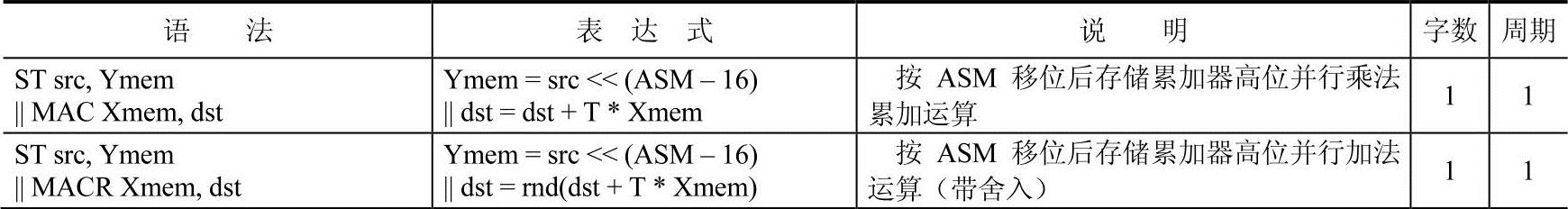

TMS320C54x提供的并行存储和加/减法指令分别为ST||ADD和ST||SUB,其中:

1)ST||ADD指令用于保存累加器内容,并行执行加法运算。该指令将src左移(ASM-16)位后存储到Ymem中;同时将dst_的内容与左移16位后的Xmem相加,加法结果存储到dst中。如果src和dst为同一个累加器,则存储到Ymem中的值是指令执行前src的值。

2)ST||SUB指令用于保存累加器内容,并行执行减法运算。该指令将src左移(ASM-16)位后存储到Ymem中;同时并行地Xmem的内容左移16位后减去dst_的内容,结果存入dst中。如果src和dst为同一个累加器,则存储到Ymem中的值是指令执行前src的值。

上述指令受状态位OVM、SXM和ASM的影响,执行结果影响状态位C和OVdst。

【例4-40】 并行存储和加/减法指令示例

7.并行存储和乘法指令

并行存储和乘法指令共有5条,见表4-38。

表4-38 并行存储和乘法指令

(续)

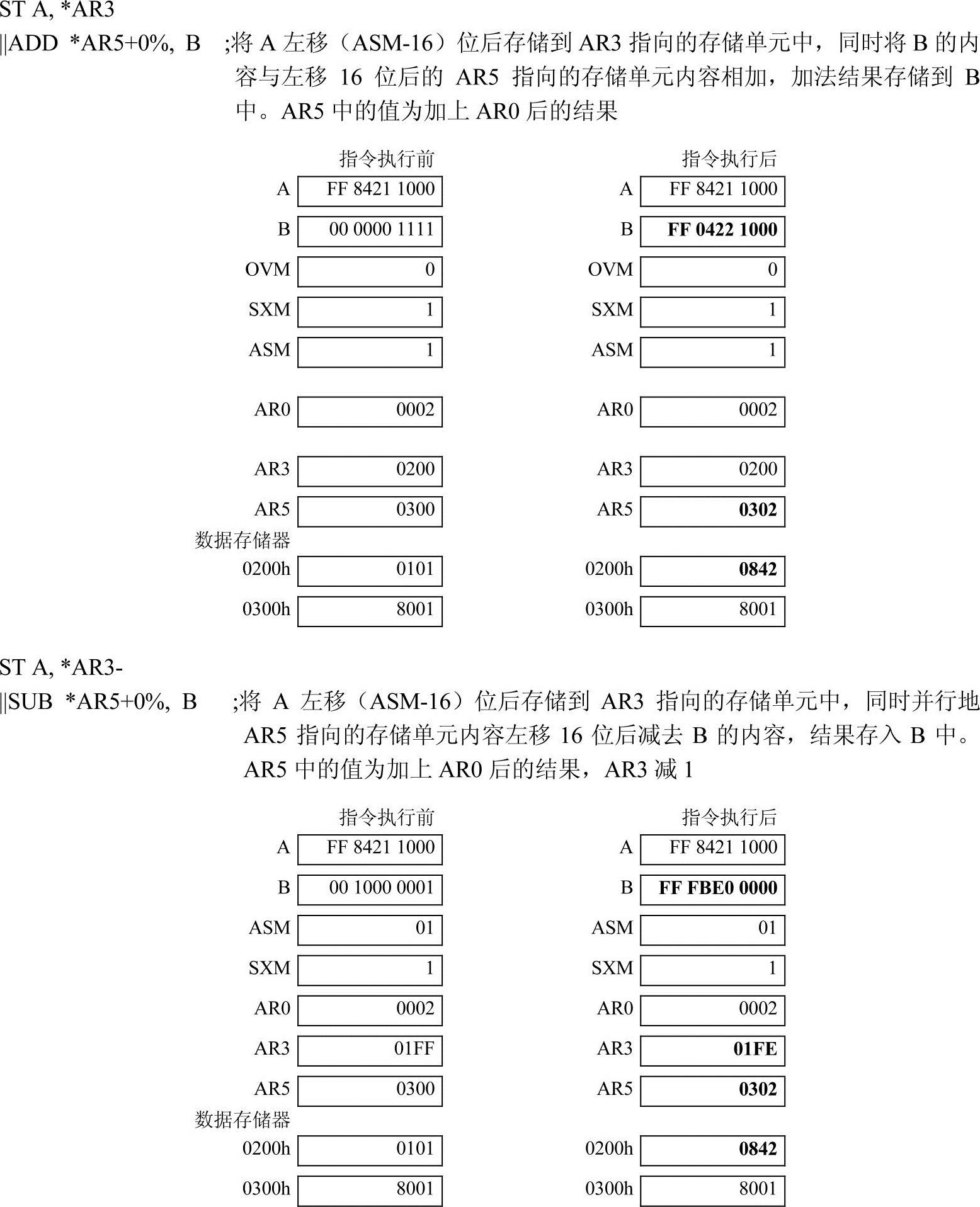

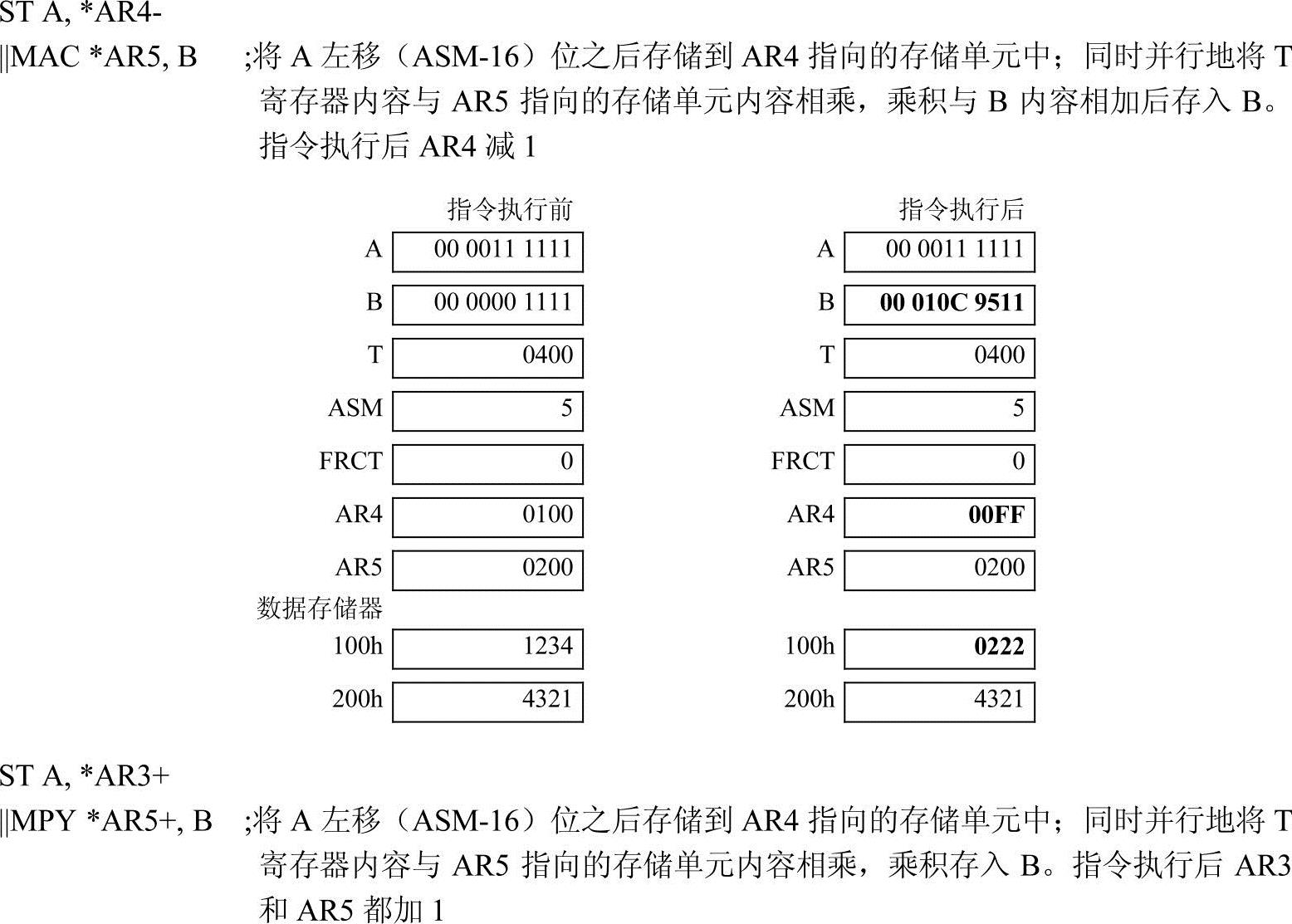

TMS320C54x提供的并行存储和乘法指令分别为ST||MAC[R]、ST||MAS[R]和ST||MPY,其中:

1)ST||MAC[R]指令用于存储累加器内容,并行执行乘法累加运算(舍入操作可选),该指令将src左移(ASM-16)位之后存储到Ymem;同时并行地将T寄存器内容与Xmem存储单元内容相乘,乘积与dst内容相加后存入dst。如果使用了扩展名R,还需要对乘法累加结果进行凑整操作,方法是与215相加,将结果的第15~0位清0,存储到dst。

2)ST||MAS[R]指令用于存储累加器内容,并行执行乘减运算(舍入操作可选),该指令将src左移(ASM-16)位之后存储到Ymem;同时并行地将T寄存器内容与Xmem存储单元内容相乘,用dst减去该乘积后再存入dst。如果使用了扩展名R,还需要对减法结果进行凑整操作,方法是与215相加,将结果的第15~0位清0,存储到dst。

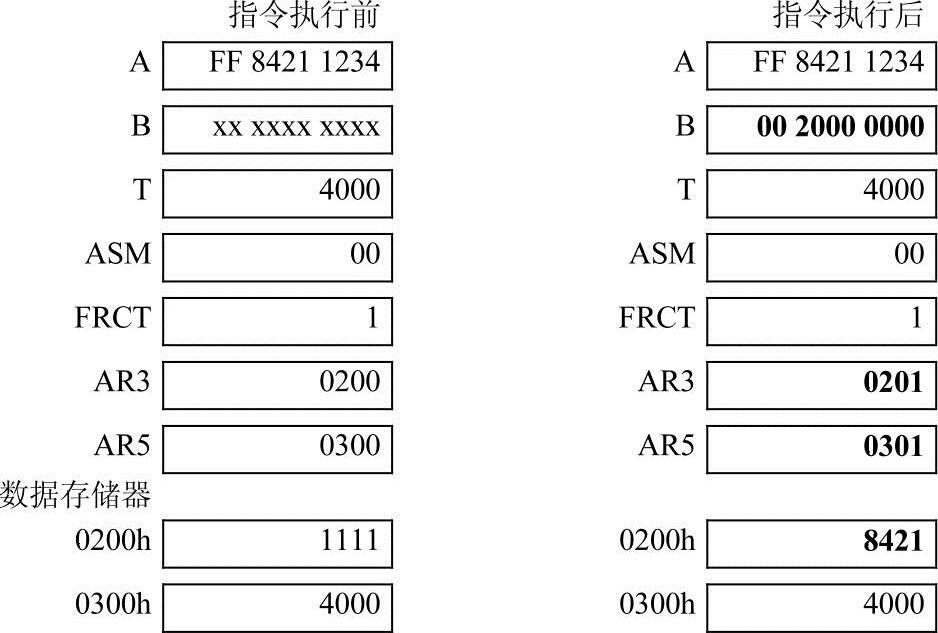

3)ST||MPY指令用于存储累加器内容,并行执行乘法运算,该指令将src左移(ASM-16)位之后存储到Ymem;同时并行地将T寄存器内容与Xmem存储单元内容相乘,乘积存入dst。

上述指令中如果src与dst为同一个累加器,则存储到Ymem中的值是指令执行前src的值。指令受状态位OVM、SXM、FRCT和ASM的影响,执行结果影响状态位C和OVdst。

【例4-41】 并行存储和乘法指令示例。

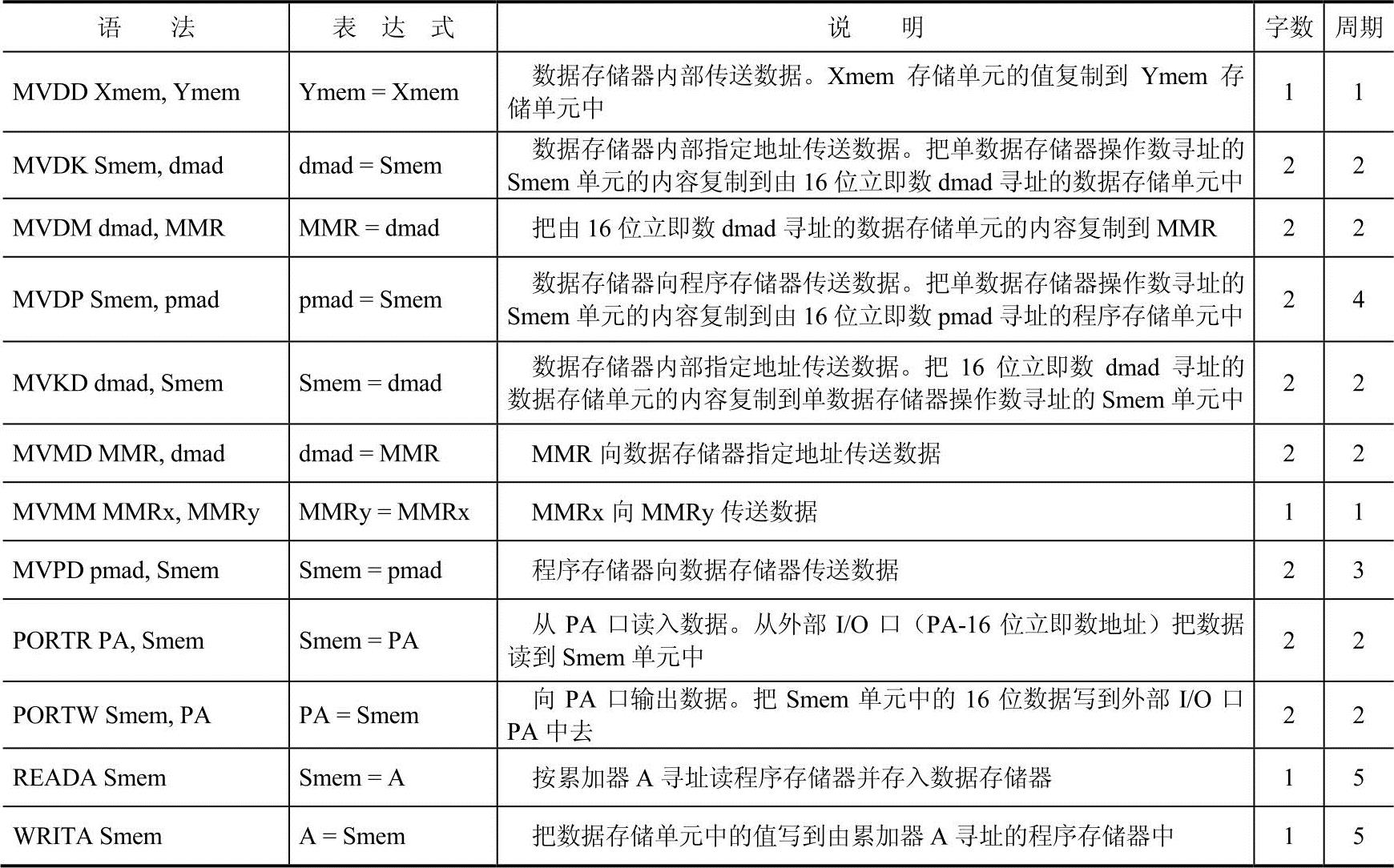

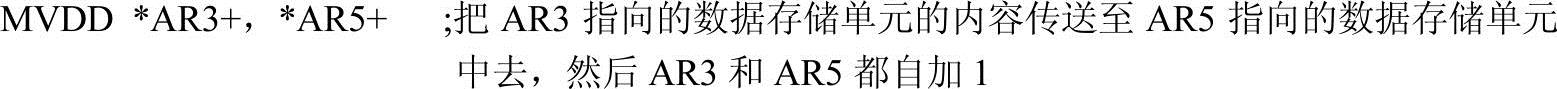

8.其他加载和存储指令

除了上述加载和存储指令外,还有一些其他的加载和存储指令,它们可以实现两个数据存储单元间数据的交换,两个存储映射寄存器间数据的交换等。其他加载和存储指令共有12条,见表4-39。

表4-39 其他加载和存储指令

TMS320C54x提供的其他加载和存储指令在4.1节寻址方式中已经进行了说明,在此不再做详细赘述。

【例4-42】 其他加载和存储指令示例。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。