存储单元是随机存取存储器RAM的核心部分,存储单元电路的形式多种多样。按工作方式的不同可分为静态和动态两类,按所用元件类型又可分为双极型和MOS型两种。双极型存储单元速度高,单极型存储单元功耗低、容量大。在要求存取速度快的场合,常用双极型RAM电路。单极型存储器适用于容量大、功耗低,常用于对速度要求不高的场合。

由于单极型存储器相对应用较多,下面以此为例介绍RAM的工作原理。

图8.3 静态RAM存储单元

1.静态RAM存储单元

图8.3所示为一个CMOS管构成的静态存储单元,由6只三极管VT1~VT6组成。其中VT1与VT2、VT3与VT4各构成一个反相器,两个反相器的输入和输出交叉连接,构成基本的触发器,作为数据存储单元。VT5、VT6是门控管,它们的导通或截止均受行选择线的控制。同时,VT5、VT6门控管控制触发器输出端与位线之间的连接状态。

当行选择线为低电平时,VT5、VT6截止,这时存储单元和位线断开,存储单元的状态保持不变;当行选择线为高电平时,VT5、VT6导通,触发器输出端与位线接通,此时通过位选择线对存储单元操作。在读控制R信号的作用下,可将基本触发器存储的数据输出。如Q=1时,1位线输出 “1”,0位线输出 “0”。根据两条线上的电位高低就可知道该存储单元的数据。在写控制信号 作用下,需写入的数据被送入1位线和0位线,经过VT5、VT6门控管加在反相器的输入端,将基本触发器置于所需的状态。(https://www.xing528.com)

作用下,需写入的数据被送入1位线和0位线,经过VT5、VT6门控管加在反相器的输入端,将基本触发器置于所需的状态。(https://www.xing528.com)

静态RAM的特点是:在不断电的情况下,信息可以长时间保存。

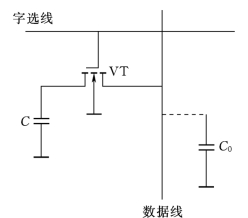

图8.4 动态RAM存储单元

2.动态RAM存储单元

一个MOS管和一个电容就可组成一个最简单的动态存储单元电路,如图8.4所示。动态存储单元电路是利用电容C上存储的电压来表示数据的状态,晶体管VT起一个开关的作用。

当存储单元未被选中时,字选线为低电平0,VT截止,C和数据线之间隔离。当存储单元被选中时,字选线为高电平1时,VT导通,可以对存储单元进行读/写操作。写入时,送到数据线上的二进制信号经VT存入C中;读出时,C的电平经数据线读出,读出的数据经放大后,再送到输出端。同时由于C和数据线的分布电容C0并联,C要放掉部分电荷。为保持原有的信息,放大后的数据同时回送到数据线上,对C要进行重写(即刷新)。对长时间无读/写操作的存储单元,C会缓慢放电,所以存储器必须定时对所有存储单元进行刷新。

动态存储器的特点是:存储的信息不能长时间保留,需要不断地刷新。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。