1.McBSP接收

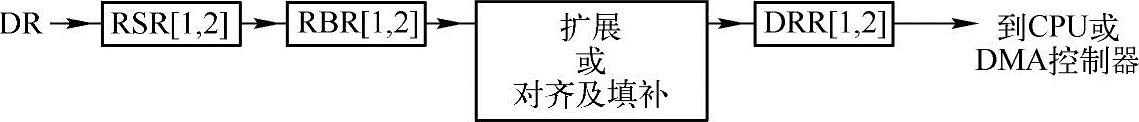

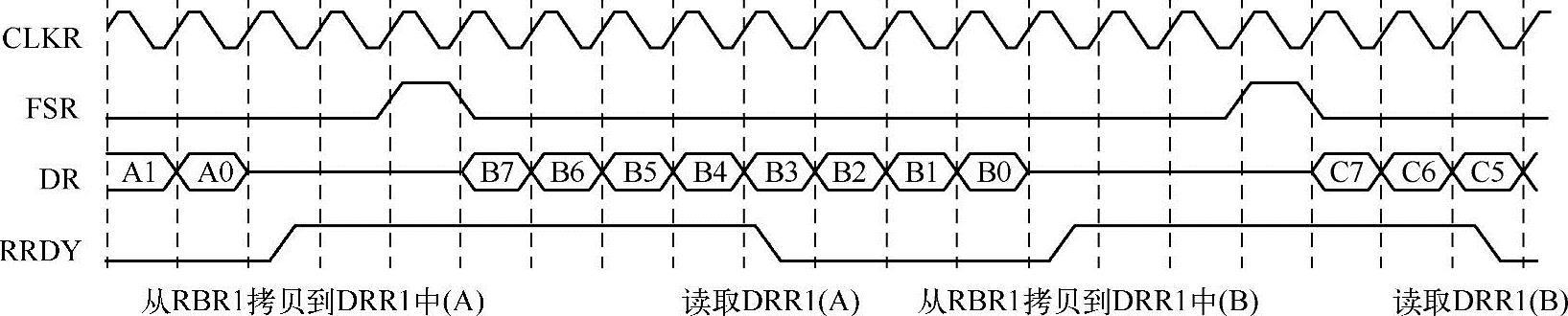

图7-15和图7-16分别给出了McBSP接收数据的物理路径和时序图。

图7-15 McBSP接收数据的物理路径

图7-16 McBSP接收数据时序

数据从DR传输到CPU或DMA控制器的过程如下:

1)McBSP等待接收帧同步脉冲FSR。

2)FSR到达后,McBSP根据RCR2寄存器RDATDLY位的设置,插入相应数据延迟时间。在图7-16中,插入了1个周期的延迟。

3)McBSP开始从DR引脚接收数据,并移入到接收移位寄存器。若串行字长度小于等于16位,则只用到RSR1;若串行字长度大于16位,则RSR1、RSR2都需要用到,并且RSR2存放了数据的高有效位。

4)当接收到一个完整串行字后,若RBR1寄存器没有被之前的数据填满,McBSP就将RSRx中的数据复制到RBRx中。若串行字长度小于等于16位,则只用到RBR1;若串行字长度大于16位,则RBR1、RBR2都需要用到,并且RBR2存放数据的高有效位。

5)若DRR1寄存器没有被之前的数据填满,McBSP将RBRx中的内容复制到DRRx中。当DRR1接收到新的数据后,SPCR1寄存器中的接收就绪位(RRDY)将被置位,这表明CPU或DMA控制器可以读取接收到的数据。若串行字长度小于等于16位,则只用到DRR1;若串行字长度大于16位,则DRR1、DRR2都需要用到,并且DRR2存放数据的高有效位。

若使用了数据压缩扩展功能(RCR2寄存器中的RCOMPAND=10b或11b),RBR1中的8位压缩数据被扩展成左对齐的16位数据存放在DRR1;若没有使用数据压缩扩展功能,数据从RBR[1,2]复制到DRR[1,2]时,会按照RJUST位的设置进行相应的对齐和填充。

6)CPU或DMA控制器从DRR寄存器中读取数据。当DRR1内容被读取后,RRDY位自动清除,即可进行下一个RBR到DRR的复制。

注意,如果两个DRR寄存器都被使用(串行字长度大于16位),CPU或DMA控制器必须先读取DRR2的内容然后再读取DRR1的内容。当DRR1被读取后,即可进行下一个RBR到DRR的复制,如果此时DRR2没有读取,那么DRR2中的数据就会丢失。

2.McBSP发送

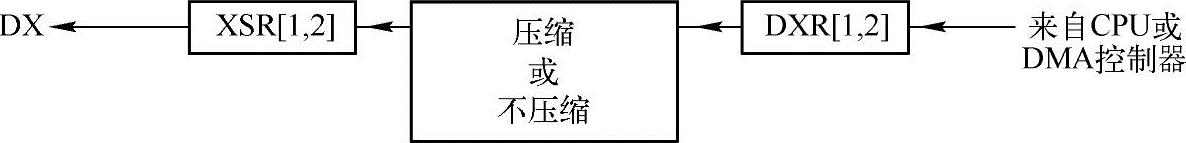

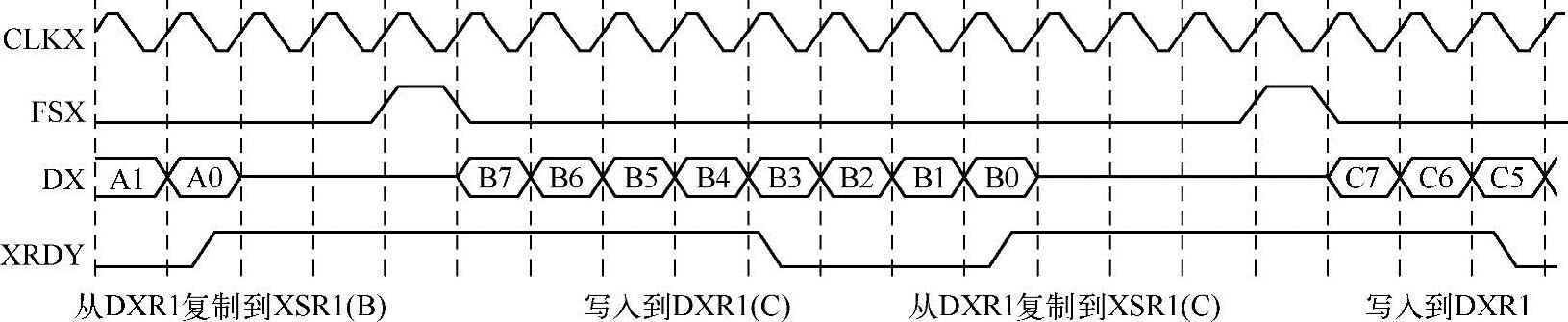

图7-17和图7-18分别给出了McBSP发送数据的物理路径和时序图。

图7-17 McBSP发送数据的物理路径

图7-18 McBSP发送数据时序

McBSP发送过程如下:

1)CPU或DMA控制器将要发送的数据写入到数据发送寄存器。当DXR1被装载时,SPCR2中的发送就绪位(XRDY)被清除,表明当前发送器还没有为新的数据准备好。

若串行字长度小于等于16位,则只用到DXR1;若串行字长度大于16位,则DXR1、DXR2都需要用到,并且DXR2存放数据的高有效位。

注意,如果两个DXR寄存器都被使用(串行字长度大于16位),CPU或DMA控制器必须先装载DXR2的数据然后再装载DXR1的数据。当DXR1被装载后,两个DXR寄存器的内容就会复制到XSRx中,因此,如果DXR2的数据没有先装载,那么会将之前DXR2中的数据复制到XSR2中。

2)当新的数据装载到DXR1后,McBSP将DXRx内容复制到XSRx,并且发送就绪位XRDY被置位,表明发送器准备好从CPU或DMA控制器接收下一个新数据。

若串行字长度小于等于16位,则只用到XSR1;若串行字长度大于16位,则XSR1、XSR2都需要用到,并且XSR2存放数据的高有效位。

如果使用了压缩扩展功能(XCR2寄存器中的XCOMPAND=10b或11b),McBSP将DXR1中的16位数据按μ-律或A-律压缩成8位数据后复制到XSR1中。若未使用压扩功能,则McBSP将DXRx中的数据原样复制到XSRx中。

3)McBSP等待发送帧同步脉冲FSX。

4)当帧同步脉冲到达后,McBSP根据XCR2寄存器XDATDLY位的设置,插入相应的数据延迟时间。在图7-18中,插入了一个周期的延迟。

5)McBSP将数据从XSRs中移出至DX引脚。

3.数据的压缩扩展

2833x支持硬件上的数据压缩扩展功能,使得数据能够以μ-律或A-律格式进行压缩扩展。μ-律和A-律分别允许13位和14位的动态范围。超出该范围的数据都将被置为最大正数或最小负数,所以为了使数据的压缩扩展达到最好的效果,通过McBSP传输的数据至少应是16位宽。

μ-律和A-律都将数据编码成8位字长,且压缩扩展后的数据总是8位长度。因此,相应的字长位(RWDLEN1、RWDLEN2、XWDLEN1、XWDLEN2)必须配置为0,表明串行数据流长度为8位。当使用压缩扩展功能时,即使帧中数据字的长度小于8,压扩时仍将数据作为8位处理。

4.先传送最低有效位(https://www.xing528.com)

一般而言,McBSP都是先发送或接收数据的最高有效位(MSB)。但是某些特定的8位数据协议(不用压扩数据)要求先发送数据的最低有效位(LSB)。若将XCR2寄存器中的XCOMPAND位设置成01b,那么这8位数据的发送顺序将被颠倒(先发送LSB)。同理,如果将RCR2寄存器中的RCOMPAND位设置成01b,数据的接收顺序也将颠倒(先接收LSB)。与数据压缩扩展一样,该操作需要将传送数据的字长位设置成0(表明传送的串行字长度为8位)。如果每一帧数据长度不足8位,McBSP会将其当做8位数据处理,且首先传送LSB。

5.时钟和串行字

数据一位一位地从DR引脚移入到RSRx中或从XSRx移出至DX引脚。每一位数据的传送时间由时钟信号的上升沿或下降沿来控制。接收时钟信号(CLKR)控制每位数据从DR引脚到RSRx的传送;发送时钟信号(CLKX)控制每位数据从XSRx到DX引脚的传输。CLKR和CLKX信号可以由McBSP外部引脚提供,也可以由McBSP内部提供且极性可以配置。

要注意的是,McBSP的时钟信号频率不能高于LSPCLK/2。当CLKX或CLKR由外部引脚提供时,要选择合适的输入时钟频率;当CLKX或CLKR由内部采样率发生器提供时,要选择合适的输入时钟频率和分频系数CLKDV(保证CLKX和CLKR小于LSPCLK/2)。

6.帧和帧同步

一个或多个串行字组合成一组传输,这个组被称为帧。用户可以定义每一帧中有多少个串行字。同一帧中的所有字以连续的数据流形式传送,但各帧之间的数据传输允许暂停。McBSP使用帧同步信号确定何时接收或发送一帧数据。出现帧同步脉冲信号时,McBSP就开始接收/发送一帧数据;下一个帧同步脉冲信号到来时,McBSP开始下一帧的发送/接收,如此反复。FSR和FSX信号可以由外部引脚提供,也可由McBSP内部提供。在McBSP操作过程中,帧同步信号从无效到有效转变时,就代表新的一组数据帧传输,因此帧同步信号的高电平脉宽可以是任意一个时钟周期。只有当帧同步信号变为无效,然后再次有效时,才发生下一个帧同步。由图7-16、图7-18的例子可看出,帧同步发生后,一组帧数据开始传输。

为使检测帧同步更加方便,可以将中断触发源设置成帧同步脉冲事件,即将RINTM(对于接收中断)和XINTM(对于发送)位配置成10b。与其他串行口中断模式不一样的是,当相应的串行口处于复位状态时,中断模式仍然可以工作(如当接收器处于复位状态时,仍然可激活RINT)。在这种情况下,FSRM/FSXM和FSRP/FSXP仍然可以为帧同步选择适当的信号源和极性。因此,即使串行口处于复位状态,FSRM/FSXM和FSRP/FSXP可以与CPU时钟同步,帧同步信号会以RINT和XINT的形式向CPU申请中断。在CPU检测到新的帧同步后,便可以安全地将串行口从复位状态重新使能。

McBSP可以配置成忽略发送和/或接收帧同步脉冲的模式。为使接收器和发送器识别帧同步信号脉冲,应清除相应的帧同步忽略位(对于接收,设置RFIG=0;对于发送,设置XFIG=0);相反,当需要忽略帧同步脉冲时,将帧同步忽略位置1。

7.帧相位

McBSP允许用户配置每帧数据有一个或两个相位,每个相位发送字的个数以及每个字的长度都可以独立配置,例如用户可以配置一帧数据包含两个相位,第一个相位传输两个16位串行字,第二个相位传输10个8位串行字。

8.中断和DMA事件

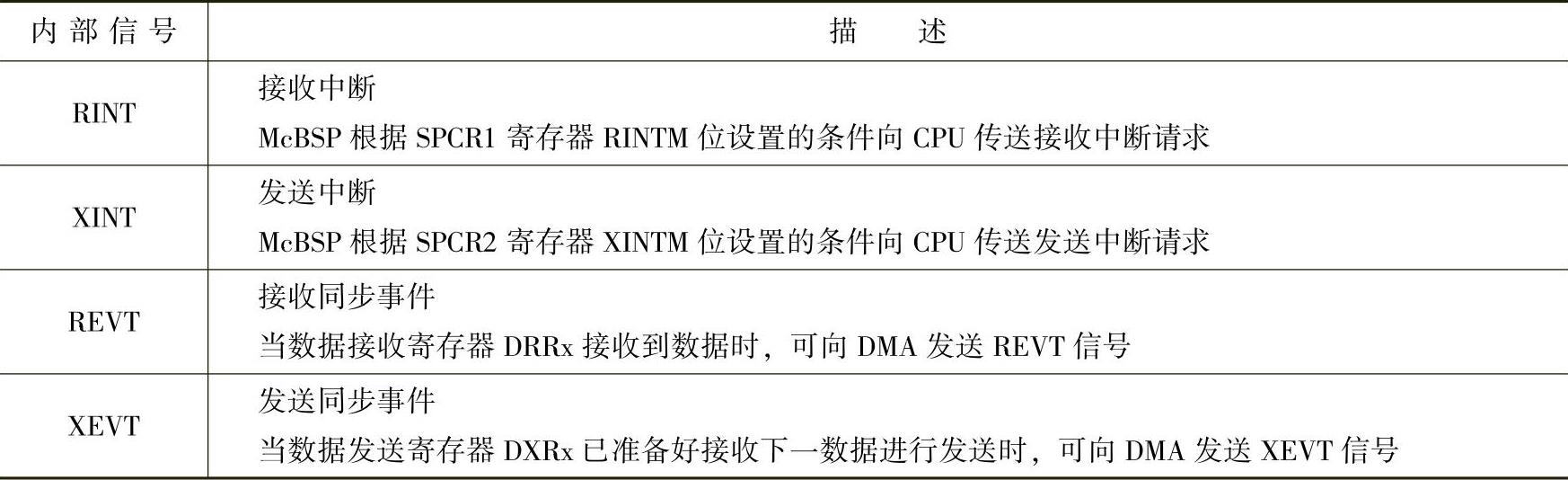

McBSP通过内部信号向CPU和DMA发送重要事件信息,这些信号见表7-15。

表7-15 McBSP产生的中断和DMA事件信号

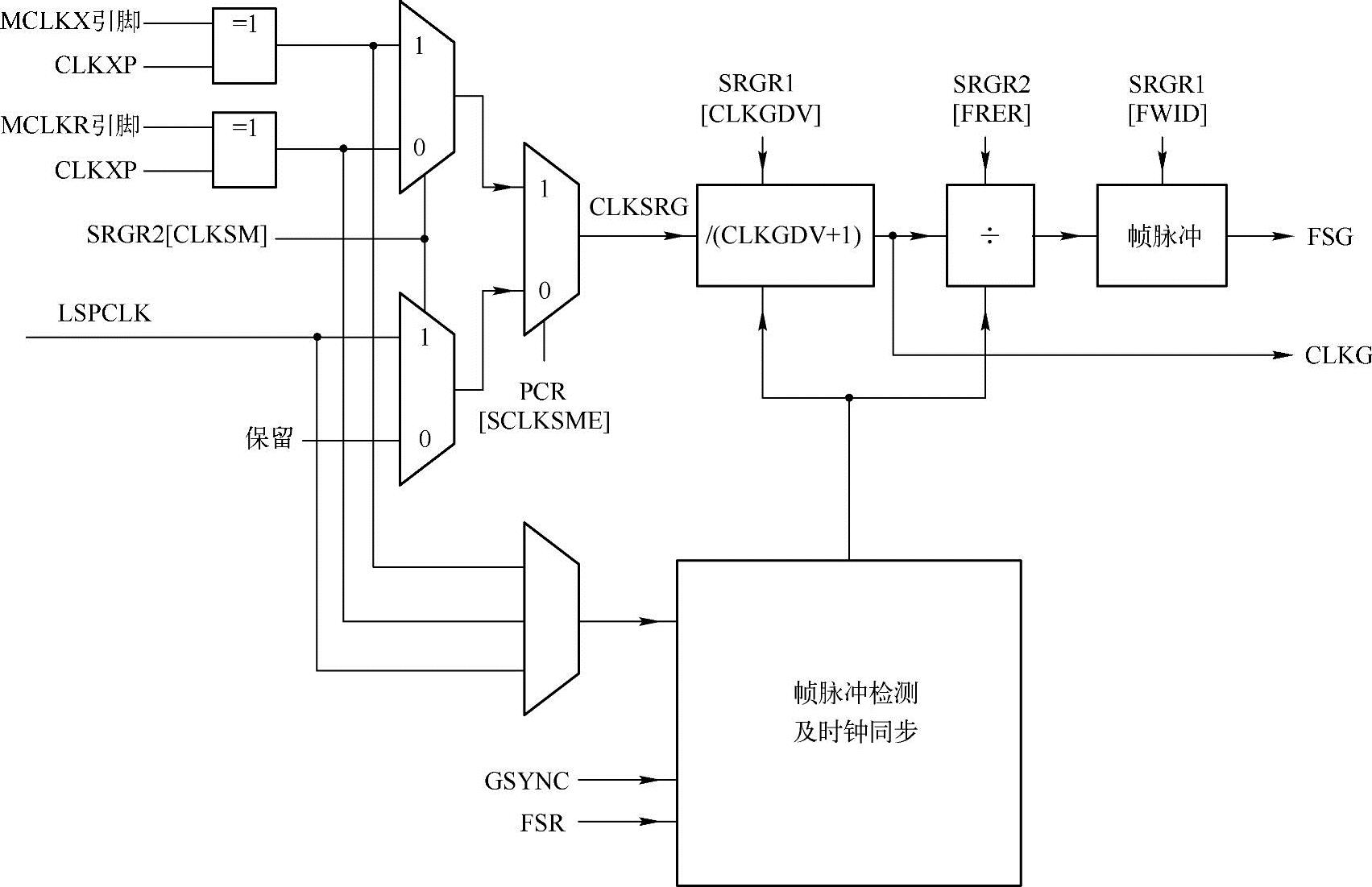

9.采样率发生器

每个McBSP都有一个可编程的采样率发生器SRG用来产生内部数据时钟CLKG和内部帧同步信号FSG。CLKG可用作DR引脚或DX引脚移位时的时钟信号。FSG可用来启动DR或DX引脚上的数据帧传送。图7-19给出了采样率发生器模块的框图。

图7-19 采样率发生器模块框图

采样率发生器有三级时钟分频器供CLKG和FSG编程设置,分别如下:

●时钟分频。通过设置SRGR1中CLKGDV位对时钟源进行分频,提供CLKG。

●帧周期分频。根据SRGR2中FPER位对CLKG分频控制从一个帧同步信号到下一个帧同步信号之间的周期。

●帧同步脉冲宽度。通过设置SRGR1中的FWID位对CLKG计数,控制每个帧同步脉冲的宽度。

除了时钟的三级分频外,采样率发生器还有帧同步脉冲检测和时钟同步模块,允许分频后的时钟与FSR引脚的帧同步脉冲同步。通过设置SRGR2中的GSYNC位来使能或禁止该功能。

采样率发生器可以为接收器和发送器提供时钟信号。通过设置时钟模式位(PCR寄存器的CLKRM和CLKXM位)控制采样率发生器提供时钟。当时钟模式位设置成1时(对于接收,CLKRM=1;对于发送,CLKXM=1),由采样率发生器输出时钟CLKG提供相应的数据时钟。需要注意的是,CLKRM=1、CLKXM=1的配置对McBSP的作用分别受到数字回送模式(由SPCR1寄存器的DLB位设定)和时钟停止模式(SPI模式,由SPCR1寄存器中CLKSTP位设定)的影响,这在PCR寄存器的位域描述中会进行介绍。

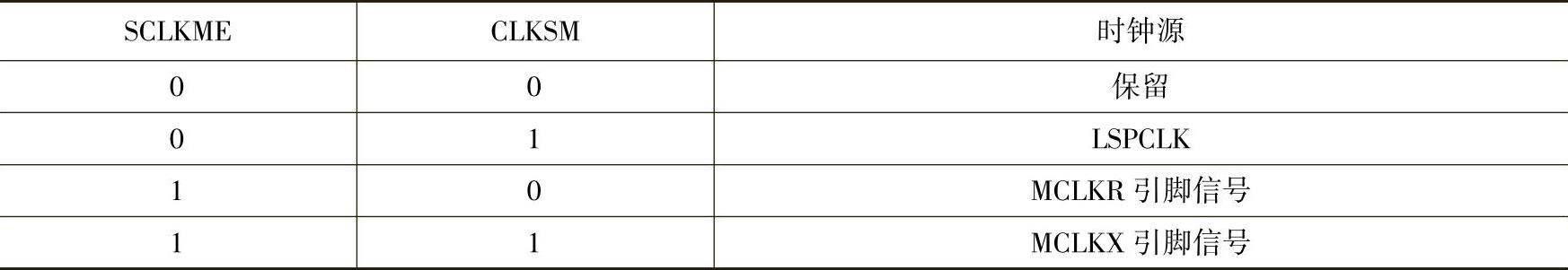

采样率发生器的输入时钟源由PCR寄存器中SCLKME位和SRGR2寄存器中CLKSM位设置,具体见表7-16。当CLKSM=1时,CLKGDV的最小值是1。

表7-16 采样率发生器时钟源设置

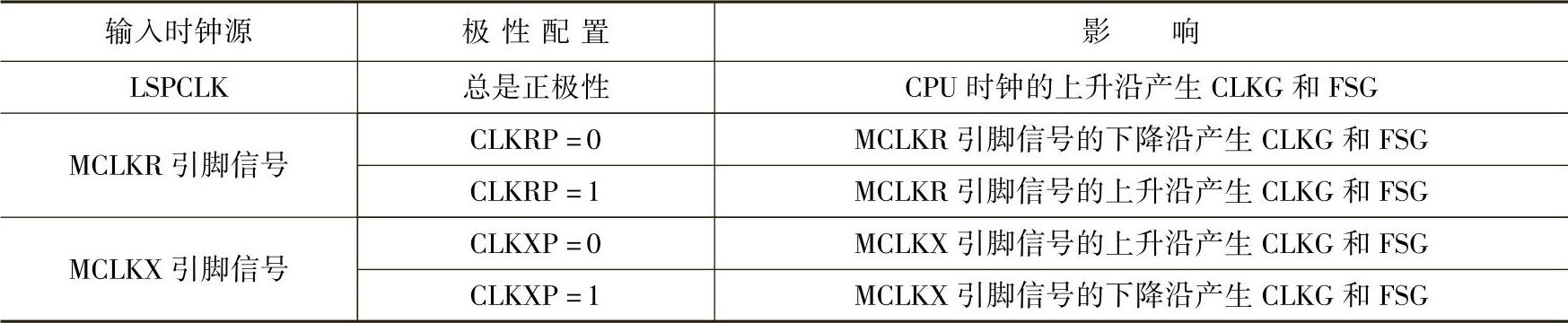

当时钟源来自外部引脚时,用户可以选择时钟极性。CLKSRG的上升沿将产生CLKG和FSG,用户可以设定输入时钟源的哪个边沿产生CLKSRG的上升沿。其极性配置和影响见表7-17。

表7-17 采样率发生器的输入时钟极性配置和影响

输入时钟源(LSPCLK或外部时钟)可通过编程分频得到CLKG,这通过SRGR1寄存器中的CLKGDV位来设置。当选择外部信号作为采样率发生器的时钟源时,SRGR2中的GSYNC位和FSR引脚可以用来控制CLKG和FSG相对于输入时钟的时序。GSYNC=1可以保证McBSP和外部器件采用相同的相位关系对输入时钟分频。若GSYNC=1,FSR引脚上一个无效到有效的电平跳变将触发CLKG和FSG的重新同步。

采样率发生器可以为接收器和发送器提供帧同步信号(FSG)。若用户需要使用FSG作为接收帧同步信号,应将FSRM设置成1(当FSRM=0,接收帧同步信号由引脚FSR提供)。

若用户需要使用FSG作为发送器的帧同步信号,应设置FSXM=1且FSGM=1。FSXM=1表明发送帧同步信号由McBSP提供而不是外部FSX引脚;在FSXM=1时,FSGM=1表明发送帧同步信号由SRG提供(当FSGM=0,FSXM=1时,数据每次从DXR[1,2]向XSR[1,2]的复制产生发送帧同步脉冲)。无论使用FSG作为接收还是发送帧同步信号,都需要使能采样率发生器(GRST=1)及帧同步逻辑(FRST=1)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。