1.设计流程

设计流程是一组过程,能够帮助设计者无差错地从芯片的设计规范开始设计直到实现最终的芯片。

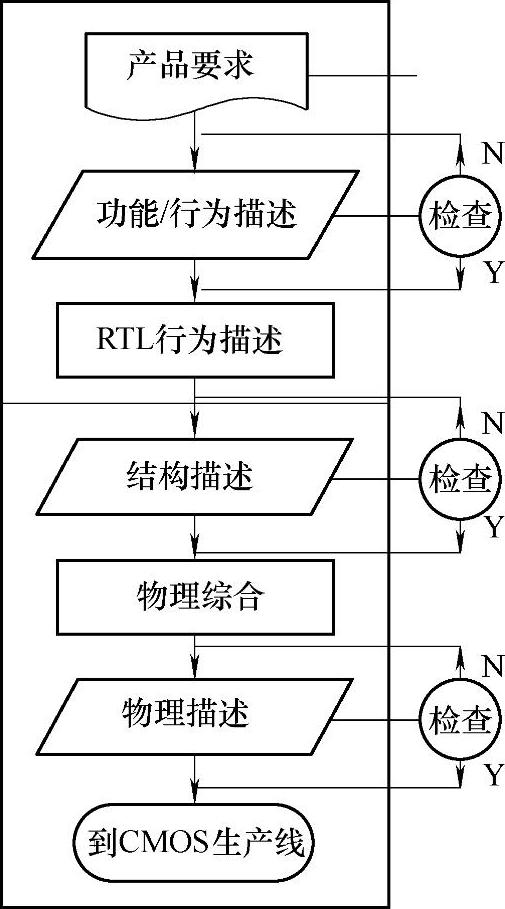

通用设计流程如图4-28所示。设计流程从行为级开始,然后进入结构级(门和寄存器),这一步称为行为级综合或RTL综合,因为在RTL级是使用硬件描述语言(Hardware Description Language,HDL)进行设计的。然后将这种设计描述转换成用于芯片生产的物理描述,这一步称为物理综合,或版图生成。

图4-28 通用设计流程

在图4-28中,设计被划分成了前端的行为级和后端的结构与物理级。在ASIC设计过程中,设计者可以在完成HDL级设计后把HDL设计交给另外的公司,将设计转化为真正的芯片。

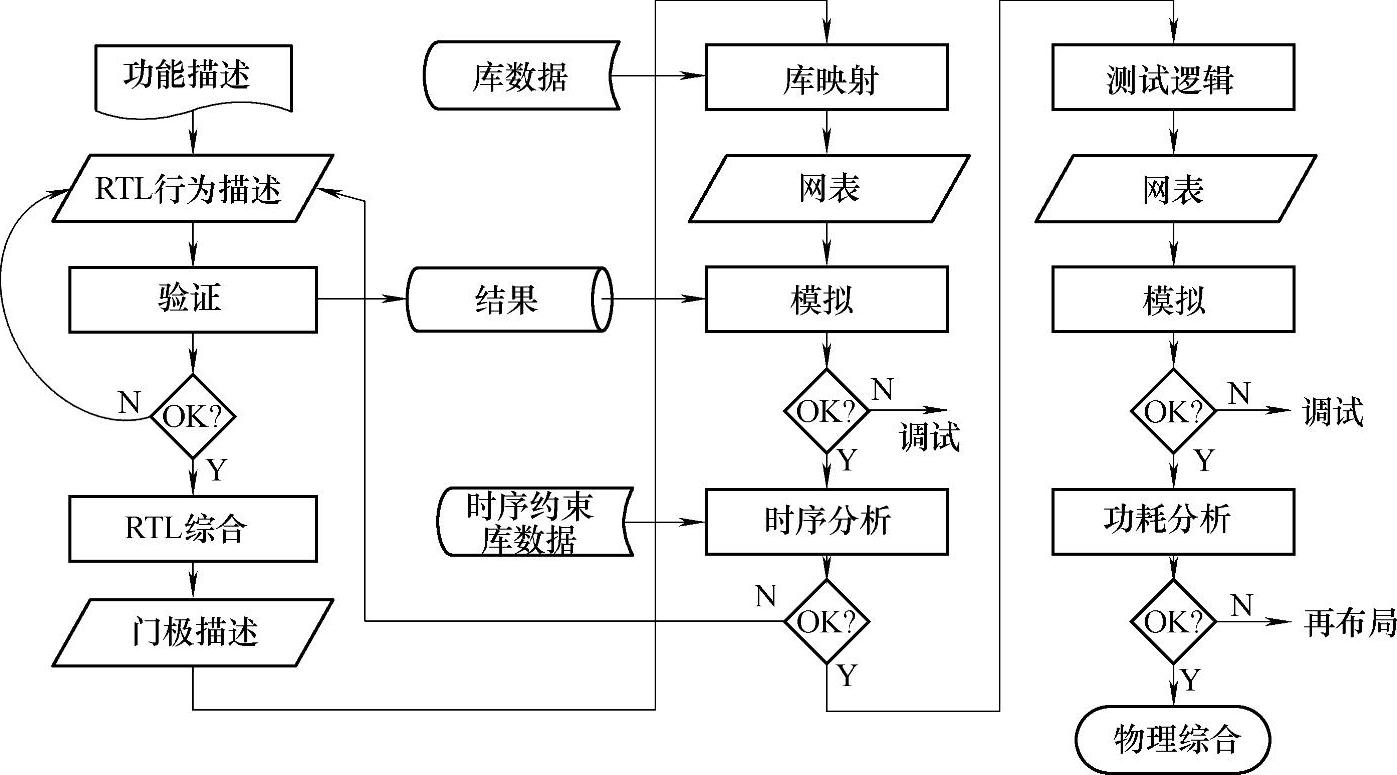

(1)行为级综合 在行为级,我们在描述操作系统特征的时候不需要指定其实现方式。行为级是与具体的实现细节相关性最小的一级,而要想获得较好的设计,行为级也是最依赖设计工具的一级。最常用的行为级综合工具会直接把RTL行为描述转化为门级、触发器级网表。RTL综合流程如图4-29所示。

图4-29 RTL综合流程

提供行为级综合常用工具的公司有Synopsys、Cadence、Design System、Mentor Graphics和Synplicity等。

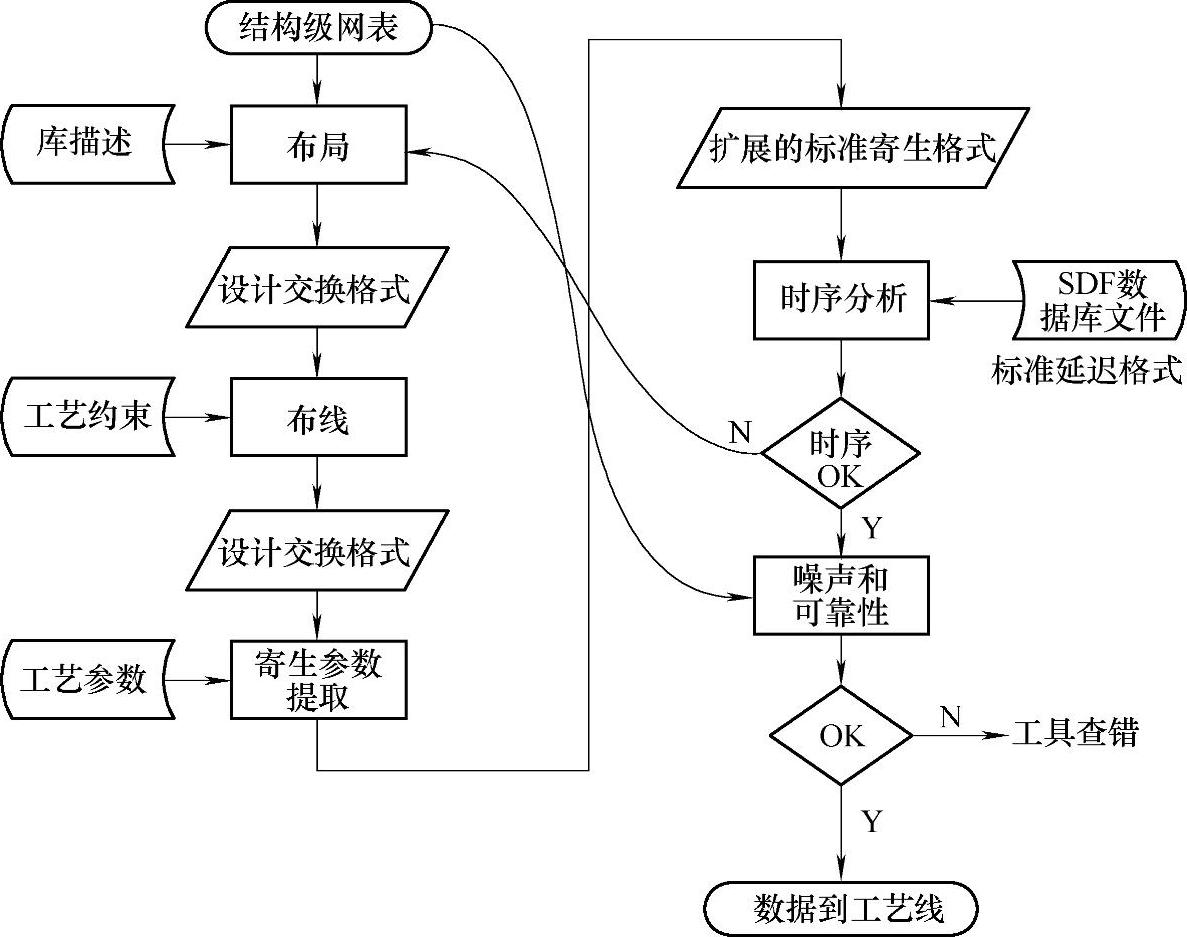

(2)物理综合 物理综合,又叫版图生成,是将设计转化为可用于制造数据的最后一步,它把一个设计从结构域转换到物理域。它对门级、触发器级网表进行处理,并产生物理版图。

自动生成版图方法主要有两种:一种是使用标准单元进行布局布线,另一种是使用软件生成器。

标准单元布局布线设计流程如图4-30所示,图中给出了一种标准的布局布线版图生成的流程,它描述了从门级、触发器级及其互连的结构级网表开始的设计过程。

2.硬件描述语言

所谓硬件描述语言,就是可以描述硬件电路的功能、信号连接关系及定时关系的语言,它可以比电路原理图更有效地表示硬件电路的特性。随着EDA技术的发展,使用HDL设计集成电路已经成为一种发展趋势。

目前最主要的硬件描述语言是美国国防部开发的VHDL(VHSIC Hardware Description Language)和Verilog公司开发的Verilog HDL。VHDL发展得较早,语法严格,而Verilog HDL是在C语言的基础上发展起来的一种硬件描述语言,语法较自由。VHDL和Verilog HDL两者相比,VHDL的书写规则比Verilog HDL烦琐一些,但VerilogHDL自由的语法也容易让一些初学者出错。

(1)HDL的特点 利用HDL设计系统硬件的方法,归纳起来有以下特点:

1)采用自上而下(Top Down)的设计方法。所谓自上而下的设计方法,就是从系统总体要求出发,自上而下逐步地将设计内容细化,最后完成系统硬件的整体设计。在利用HDL的硬件设计方法中,设计者将自上至下分成三个层次对系统硬件进行设计。

第一层次:行为描述。实质上是对整个系统的数学模型的描述。目的是在系统设计的初始阶段,通过对系统行为描述的仿真来发现设计中存在的问题。

图4-30 标准单元布局布线设计流程

第二层次:RTL方式描述。这一层次称为寄存器传输描述,用行为方式描述的系统结构程序,直接映射到具有逻辑单元的硬件是很难的。系统采用RTL方式描述,才能导出系统的逻辑表达式,才能进行逻辑综合。

第三层次:逻辑综合。利用逻辑综合工具,将RTL方式描述的程序转换成用基本逻辑元件表示的文件。逻辑综合的结果相当于在人工设计硬件电路时,根据系统要求画出了系统的逻辑原理图。

2)系统中可大量采用ASIC芯片。硬件设计人员在设计硬件电路时,无须受只能使用通用元器件的限制,而可以根据硬件电路的设计需要,设计自用的ASIC芯片或可编程逻辑器件。

3)多层次仿真。在系统设计过程中进行了三级仿真,即行为层次仿真、RTL层次仿真和门级层次仿真,从而可以在系统设计早期发现设计中存在的问题。

4)降低了硬件电路设计难度。在用HDL设计硬件电路时,可以使设计者免除编写逻辑表达式或真值表之苦。

5)主要设计文件是用HDL编写的源程序。用HDL的源程序作为归档文件具有资料量小、便于保存、继承性好和阅读方便等优点。(https://www.xing528.com)

(2)VHDL简介 VHDL最开始是美国军方设计开发的,因此在实际使用的过程中语法要求比较严格。下面简单介绍一下VHDL的基本知识。

1)概述。一个完整的VHDL程序通常包含实体(Entity)、结构体(Architecture)、配置(Configuration)、包集合(Package)和库(Library)5部分。前4部分是可分别编译的源设计单元。实体用于描述所设计系统的外部接口信号;结构体用于描述系统内部的结构和行为;包集合存放各设计模块都能共享的数据类型、常数和子程序等。配置用于从库中选取所需单元来组成系统设计的不同版本;库存放已经编译的实体、构造体、包集合和配置。库可由用户生成或由ASIC芯片制造商提供,以便在设计中为大家所共享。

2)格式。电路基本结构都由实体说明(Entity Declaration)和构造体(Architecture Body)两部分构成。实体说明部分规定了设计单元的输入输出接口信号和引脚,而构造体部分定义了设计单元的具体构造和操作(行为)。

实体说明:

Entity实体名IS

[类型参数说明];

[端口说明];

END实体名;

一个基本单元设计的实体说明以“Entity实体名IS”开始至“END实体名”结束。

构造体说明:

ARCHITECTURE构造体名OF实体名IS

[定义语句]内部信号、常数、数据类型、函数等的定义;

BEGIN

[并行处理语句];

END构造体名;

一个构造体从“ARCHITECTURE构造体名OF实体名IS”开始至“END构造体名”结束。

VHDL有3种形式的子结构描述语句:BLOCK语句结构、PROCESS语句结构和SUB-PROGRAMS语句结构。

比较常用的是PROCESS语句,PROCESS语句的基本格式如下。

[进程名]:PROCESS(信号1,信号2,…)

BEGIN

…

ENDPROCESS;

PROCESS语句从“PROCESS”开始至“ENDPROCESS”结束。

(3)使用工具 VHDL源代码编写完成之后,还需要对源代码进行操作,主要包括语法检查、功能检查等,此时就要用到一些EDA工具。下面简单列出常用的几种EDA工具。

1)ModelSim。ModelSim是Mentor Graphics公司的模拟工具,可以实现对VHDL和Ver-ilogHDL源程序的模拟,同时也支持混合模拟。

2)Active HDL。Active HDL是Aldec公司的模拟工具,可以实现对VHDL和Verilog HDL源程序的模拟,同时也支持混合模拟。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。