本节将利用Mentor Graphics公司的仿真软件HyperLynx进行一些仿真实验与演示,通过仿真来观察接收端波形,以验证各种端接的效果以及其差异。

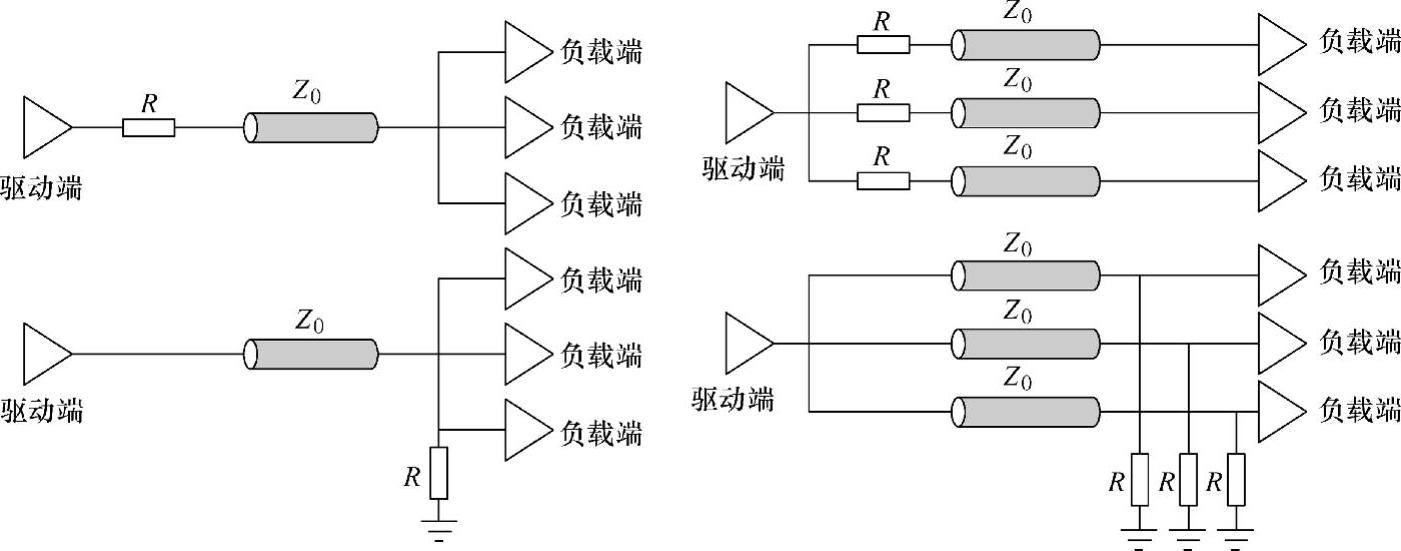

图5-15 多负载端接匹配

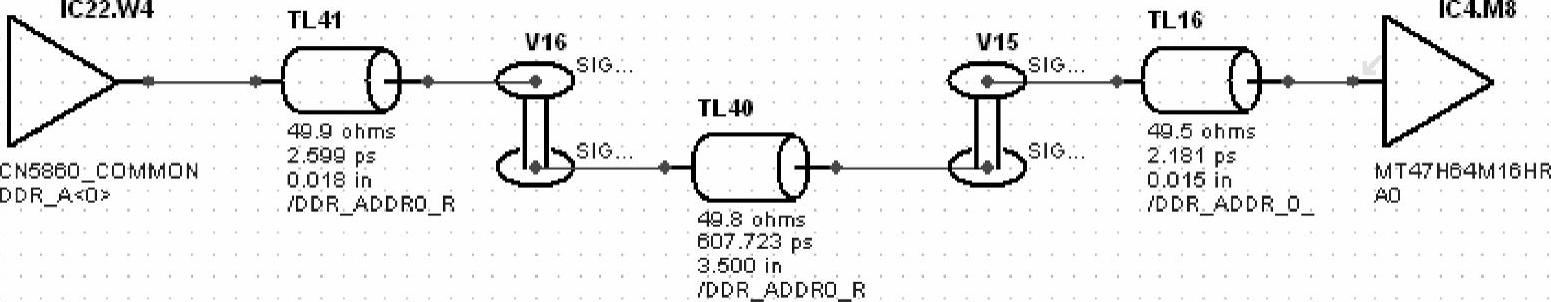

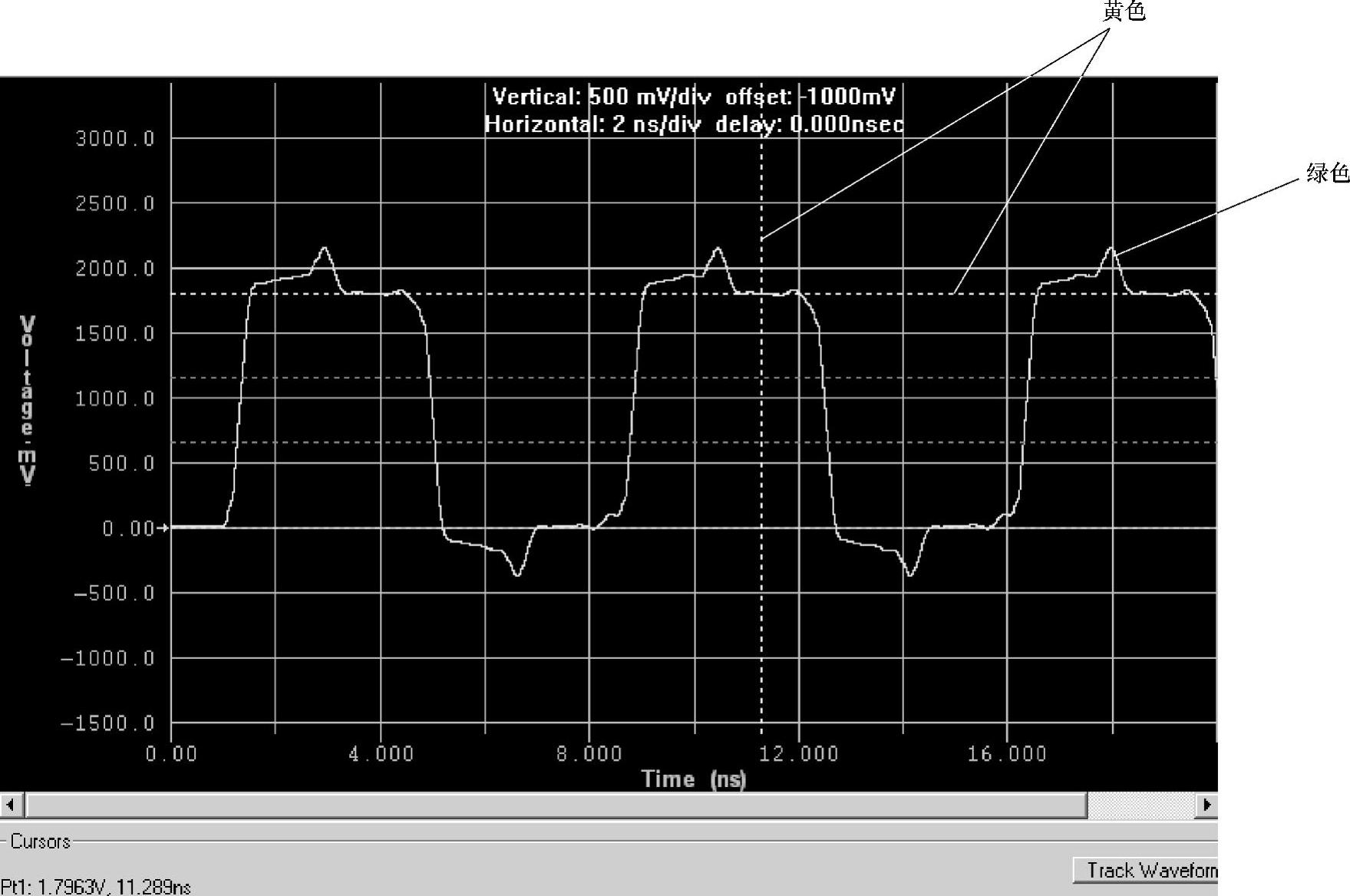

为了更明显地观察到有端接和没有端接时接收端波形的区别,先来仿真一下没有端接时的情况,在此选用一个非常简单的拓扑结构,以方便分析问题。仿真所用的拓扑结构如图5-16所示。

图5-16 无端接走线拓扑

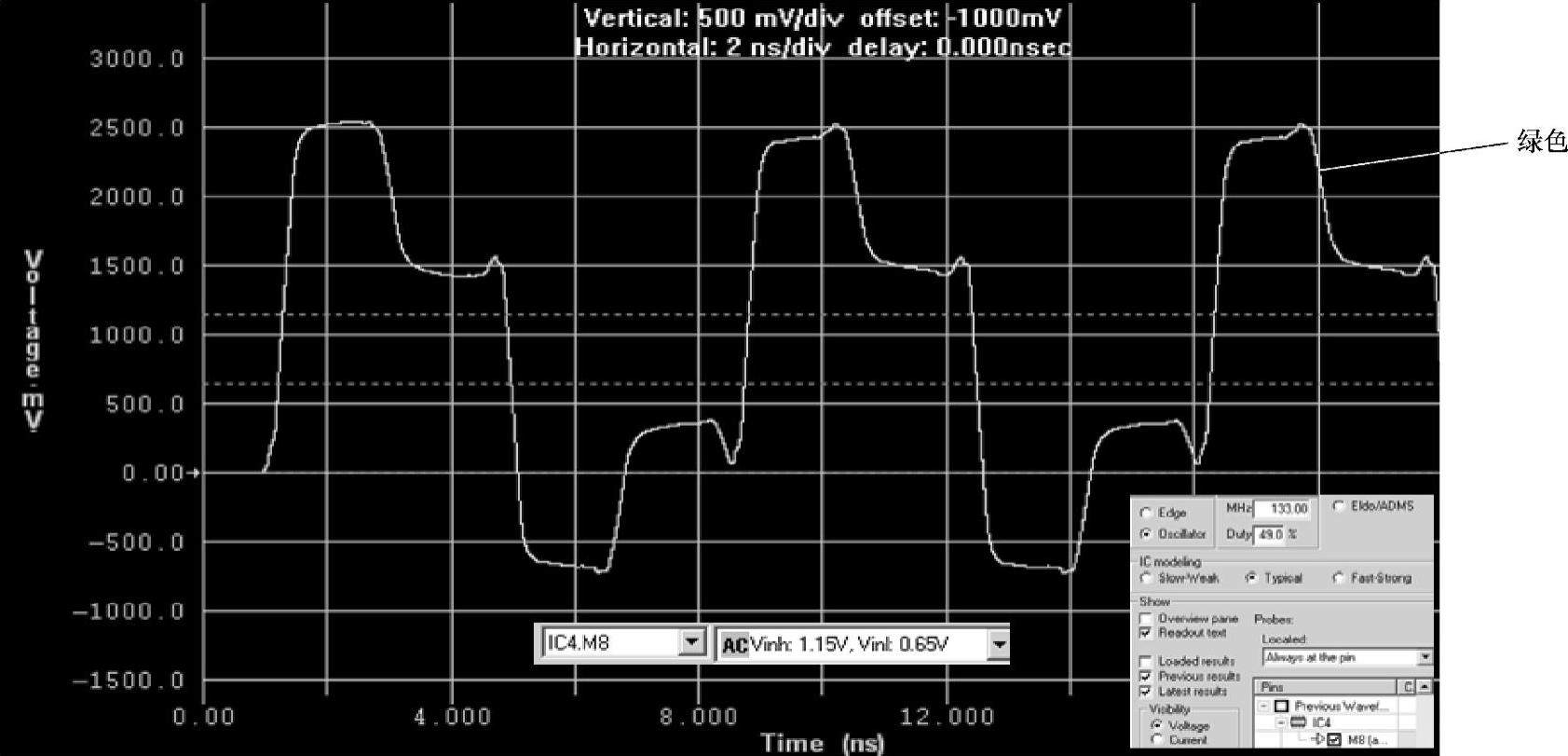

发送端芯片(driver)IC22通过breakout via后换至PCB内层,经过3.5in[1]的主传输线后再经过一个via到达接收端芯片(receiver)IC4。这其实是一个DDR2的地址信号线,分析方便起见,并没有连接多个receiver,而是以一个receiver为例进行分析。仿真结果参考图5-17,绿色波形为receiver IC4端的波形。

图5-17 无端接走线拓扑仿真结果

可见波形上叠加了明显的反射波能量,波形幅度最大达到了2.5V,远高于其正常的工作电平1.8V,这个因反射而叠加的波形正是由于传输线和芯片内部的阻抗不匹配造成的,反射的存在可能会导致data的setup time和hold time不能满足要求而引起时序错误,因而在设计中是需要避免的。

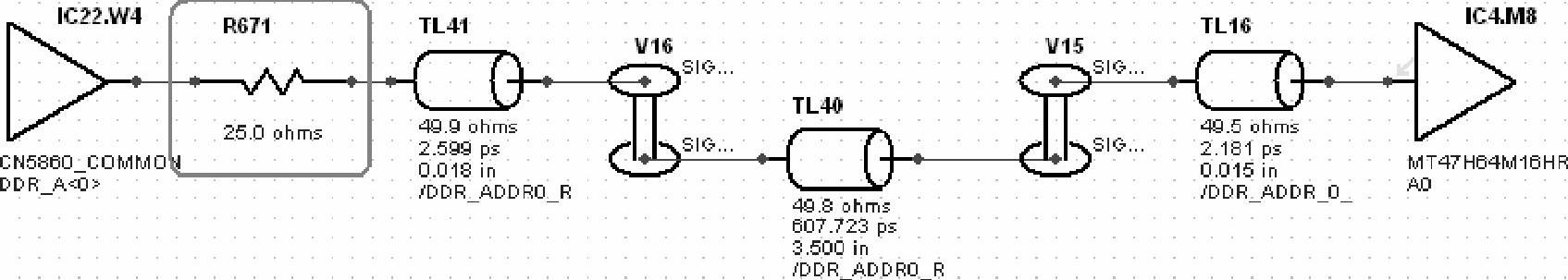

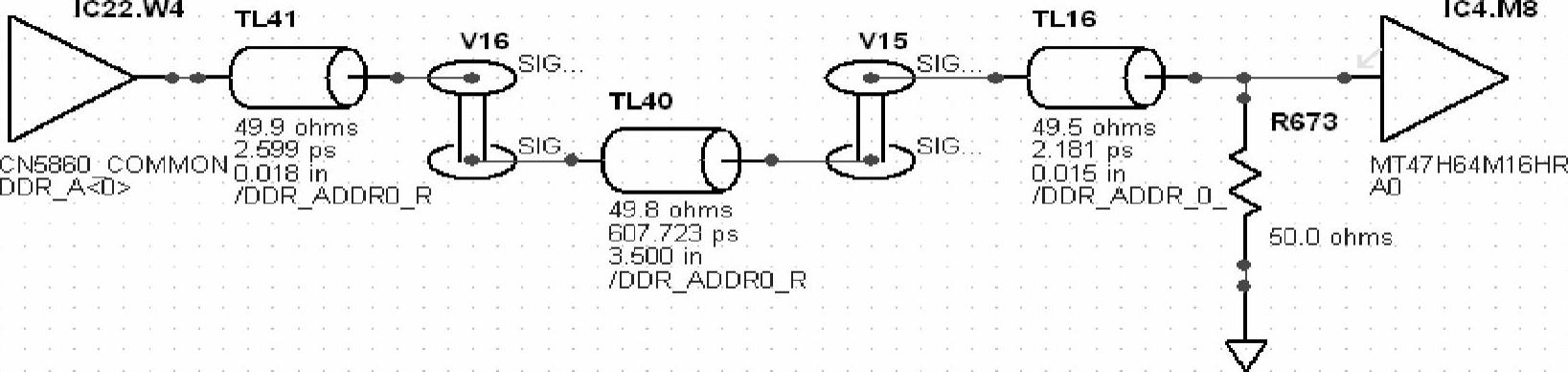

既然driver端的模型提示芯片内部输出阻抗为25Ω,而传输线阻抗为49.8Ω,基本上是标准的50Ω阻抗传输线,这样根据串联端接时串联电阻的选取规则,选用一个25Ω的电阻作为源端匹配电阻,加上串联匹配电阻的拓扑结构如图5-18所示,电阻放在非常靠近driver的位置。

图5-18 串联端接走线拓扑

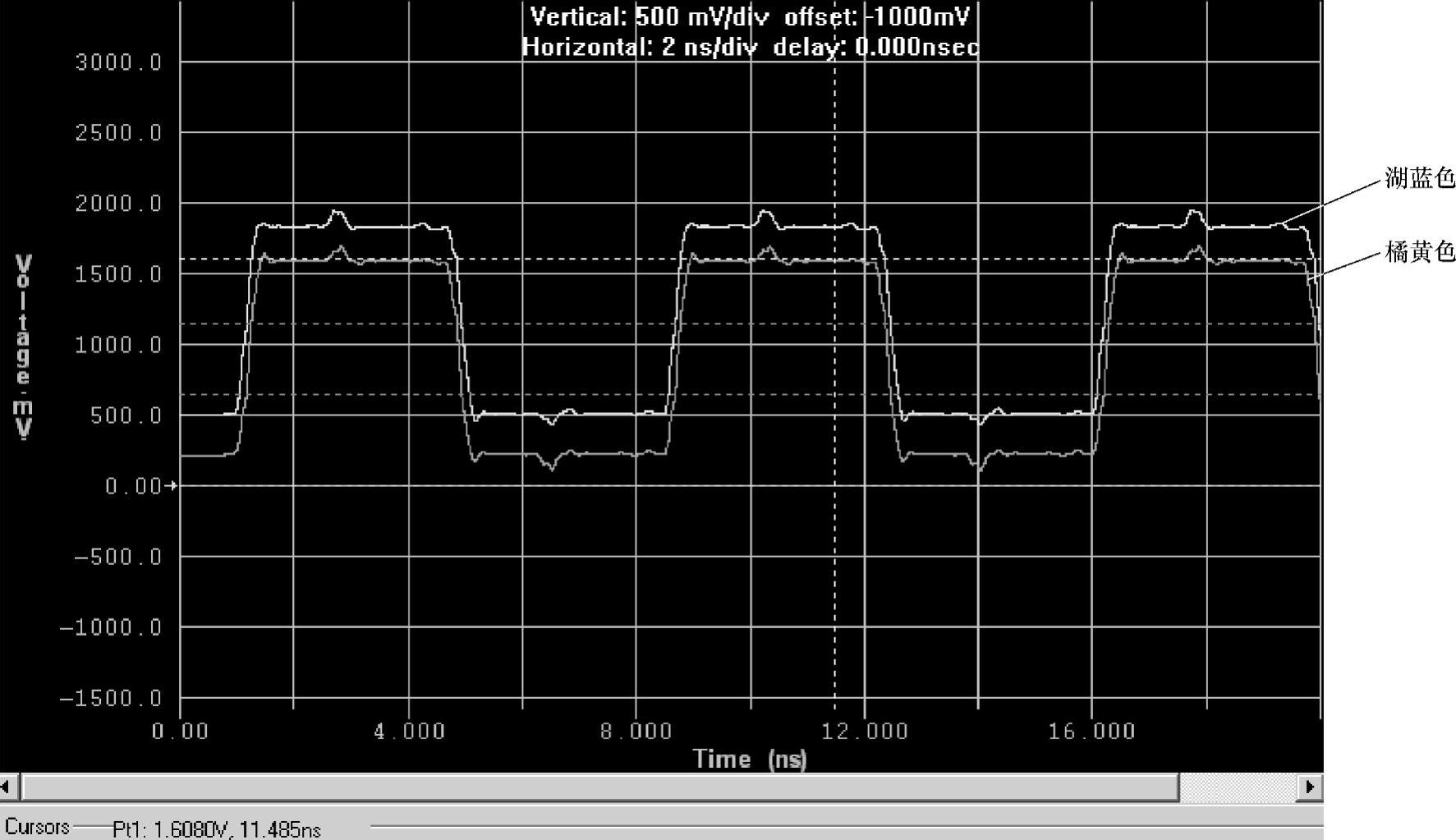

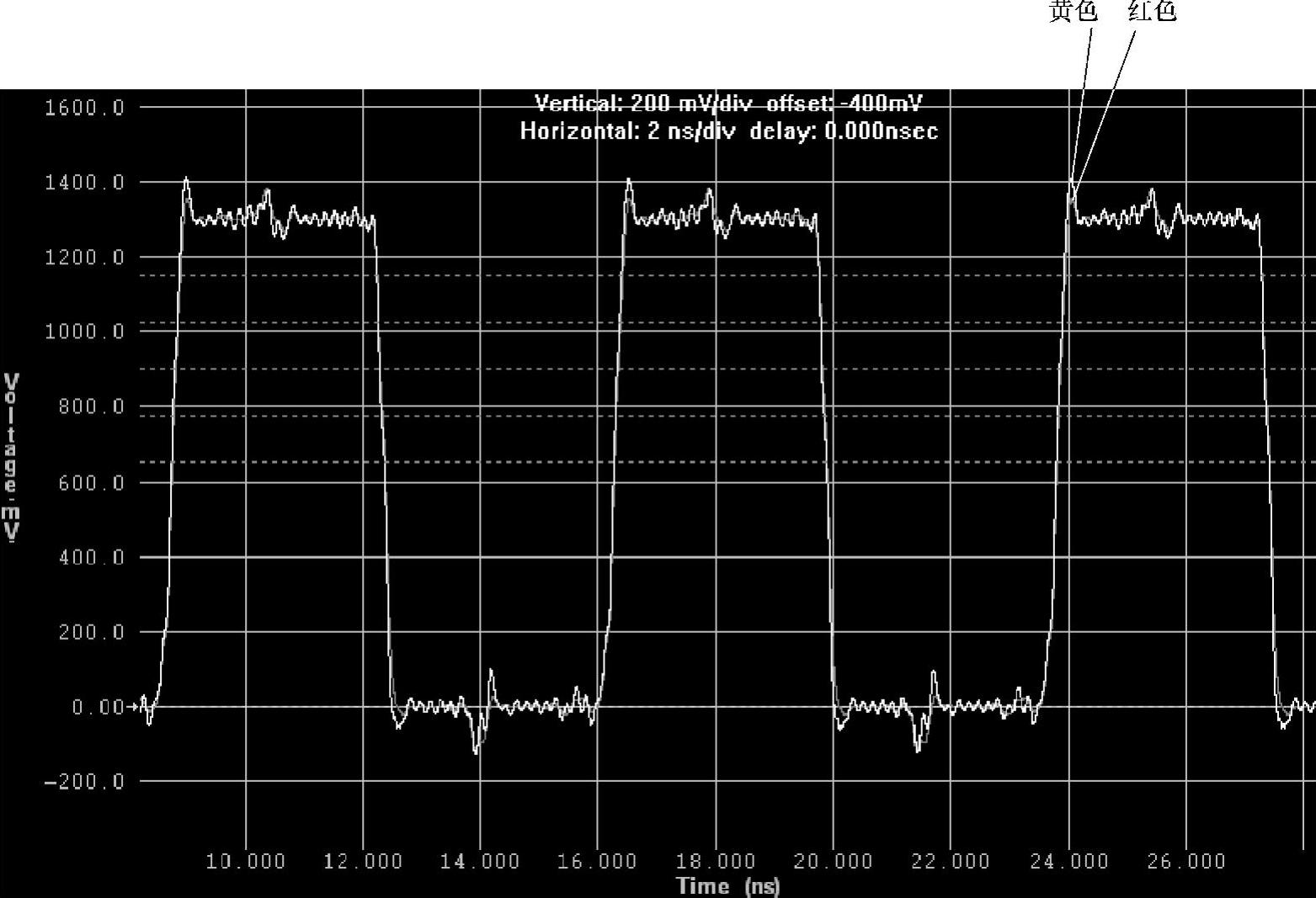

仿真结果如图5-19所示,相比没有端接的情况,接收端波形有明显的改善,黄色mark坐标显示的电平为1.7963V,即电平基本稳定在1.8V,从波形上来看也很容易满足时序的要求,可见正确的端接对改善信号质量是非常重要而有效的。

图5-19 串联端接走线拓扑仿真结果

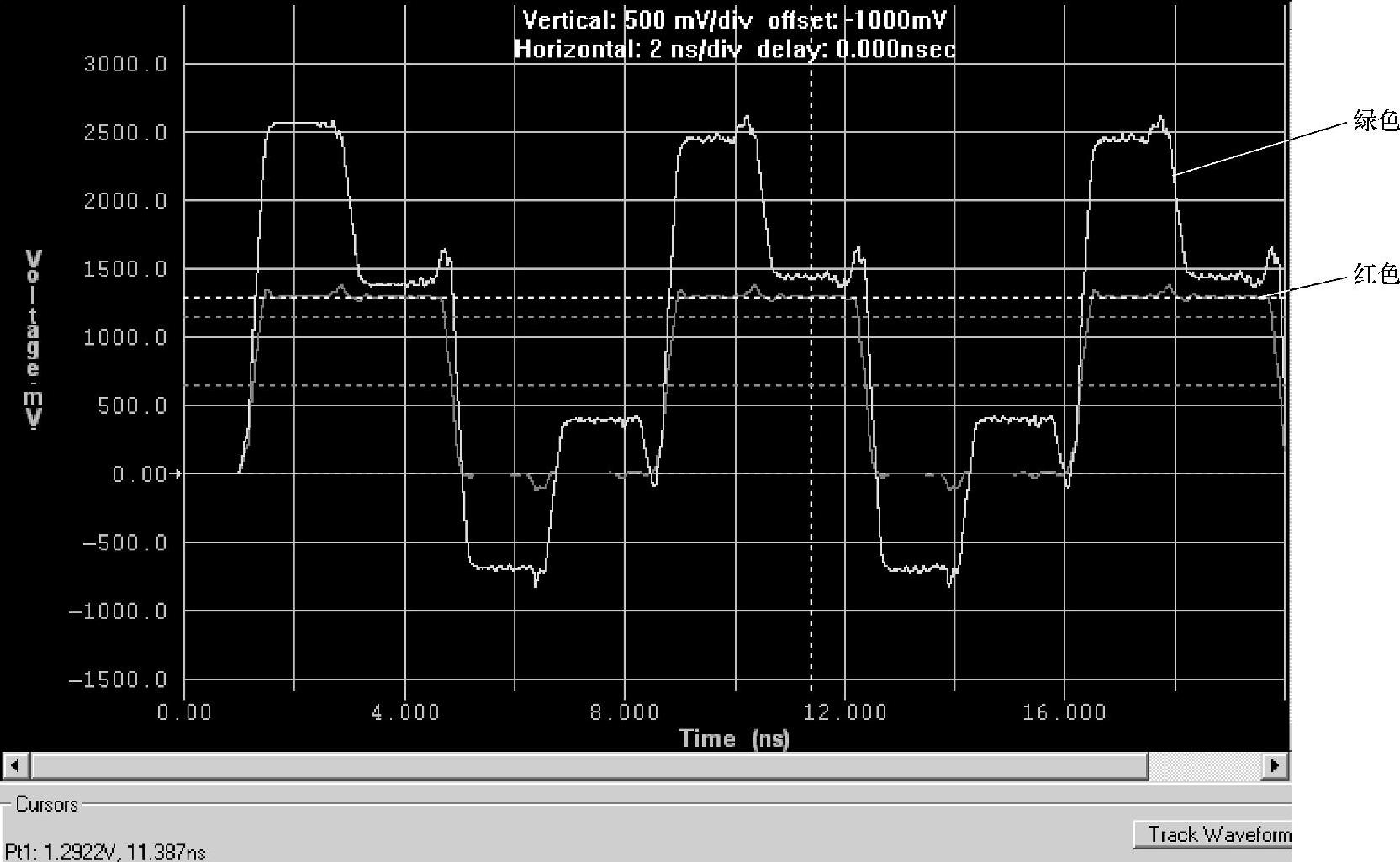

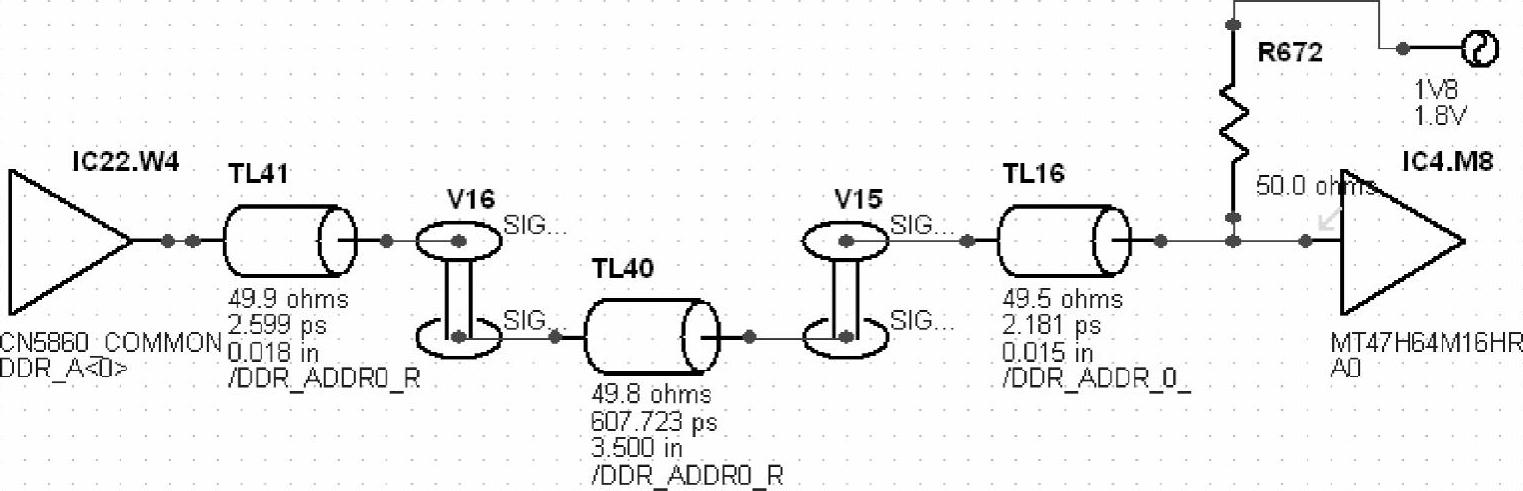

并联端接可以通过一个电阻连接到电源或者地,此处选用50Ω电阻连接到地(即Gnd),如图5-20所示。图5-20中绿色和红色曲线分别为receiver端没有端接和接了图5-21中并联匹配电阻的仿真结果,两者相比,端接后波形同样有明显的改善。

图5-20 并联端接走线拓扑

(https://www.xing528.com)

(https://www.xing528.com)

图5-21 并联端接走线拓扑仿真结果

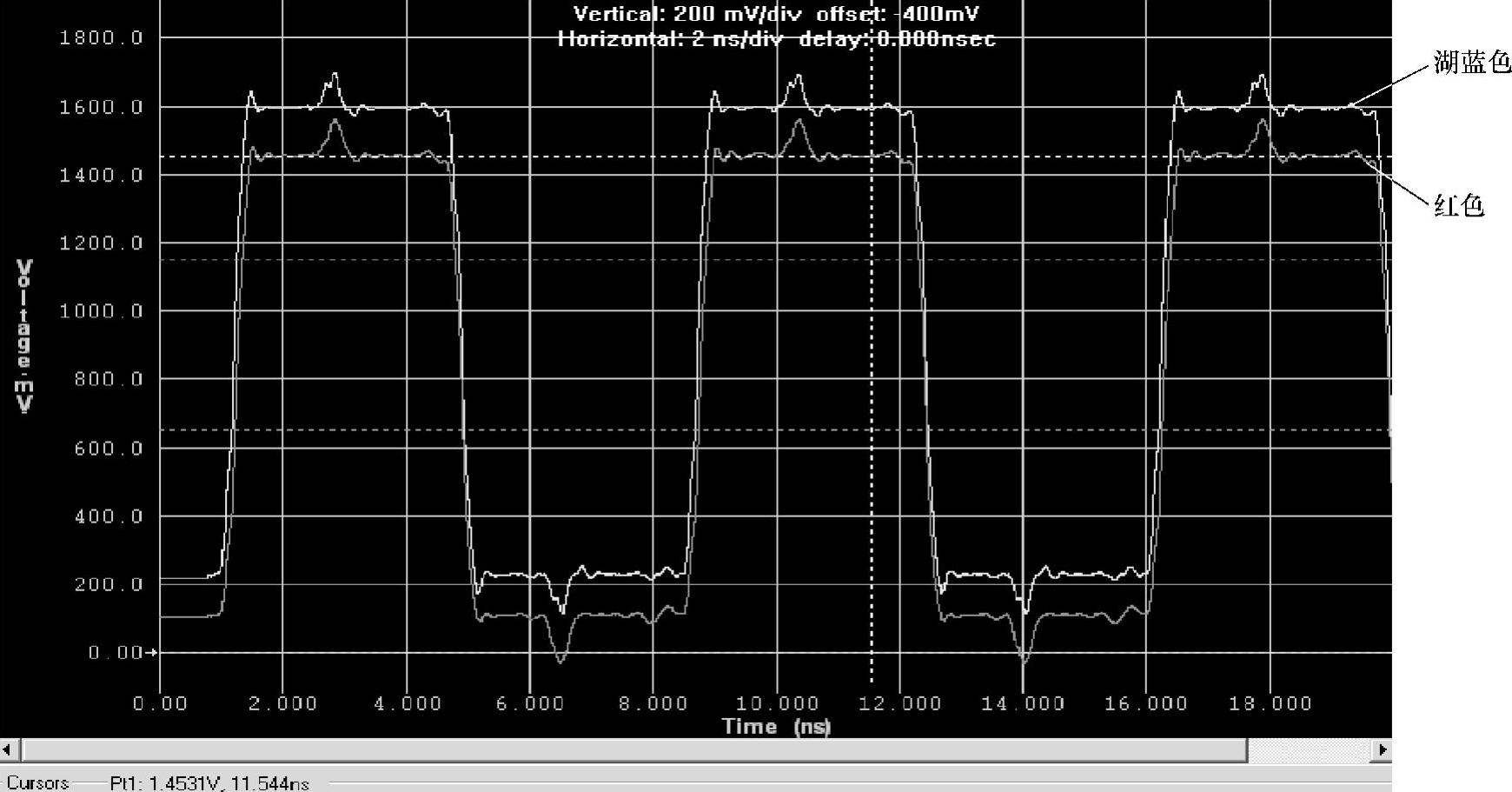

仿真结果如图5-21所示,而高电平的大小随着连接到地或者电源的不同会有所不同。图5-22和图5-23所示分别是接50Ω电阻到电源的拓扑结构图上和仿真结果。图5-23中湖蓝色曲线是50Ω接到1.8V电源,橘黄色曲线为50Ω接到0.9V电源,与接收端Spec的高低电平相比,接到0.9V的波形更好地稳定在高低电平之间。相比而言,上拉到0.9V比上拉到1.8V效果更好,这也是很多DDR2设计中实际采用的端接电平。

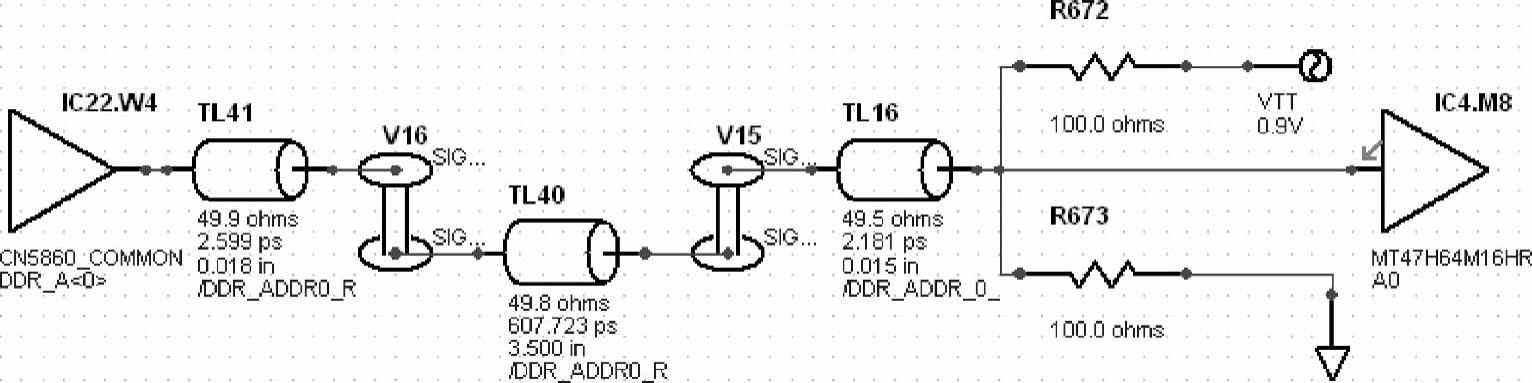

戴维南端接拓扑结构如图5-24所示,两个100Ω电阻分别连接到电源和地,并联后的阻抗50Ω,与传输线的50Ω阻抗匹配,其仿真结果为图5-25中的红色曲线。另一条湖蓝色曲线为并联端接50Ω电阻到0.9V电源的结果,即和图5-23中的橘黄色曲线为同一条曲线。两种端接方式仿真结果类似,但戴维南端接因为始终有DC电流流过电阻,因而额外的功耗要求较高。

图5-22 并联端接到VCC

图5-23 并联端接到VCC仿真结果

图5-24 戴维南端接拓扑

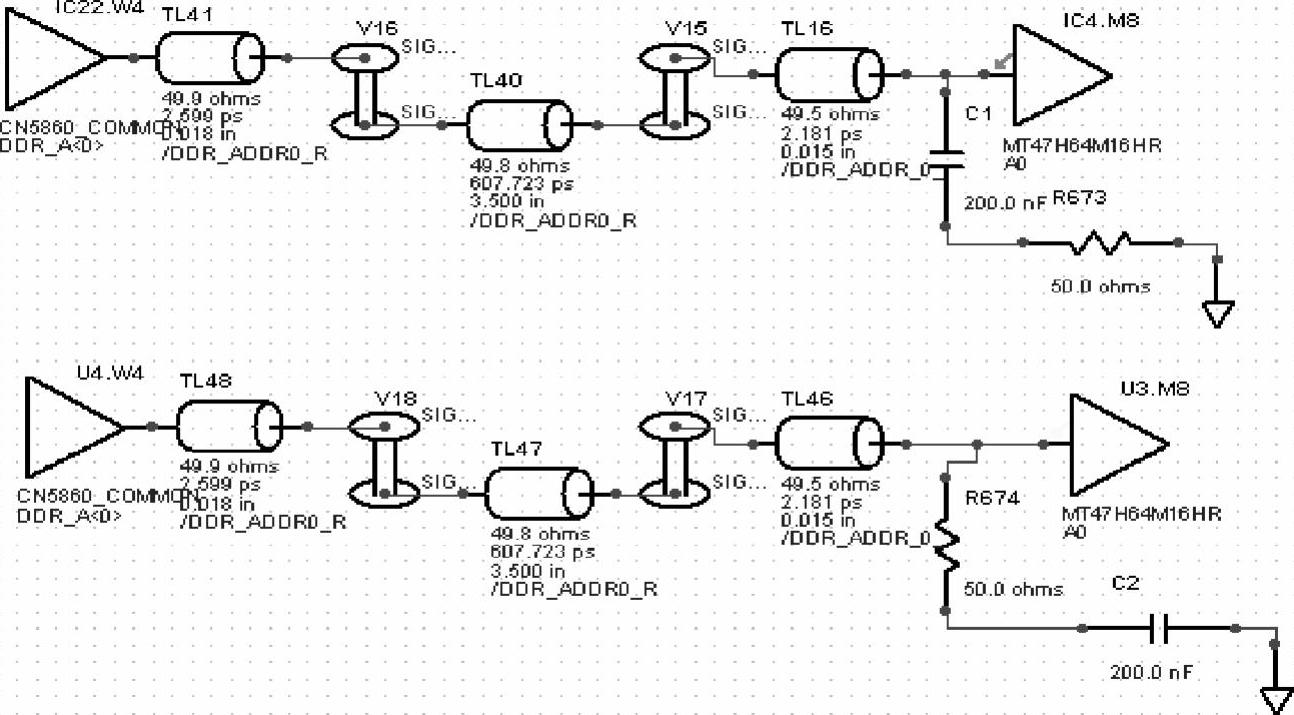

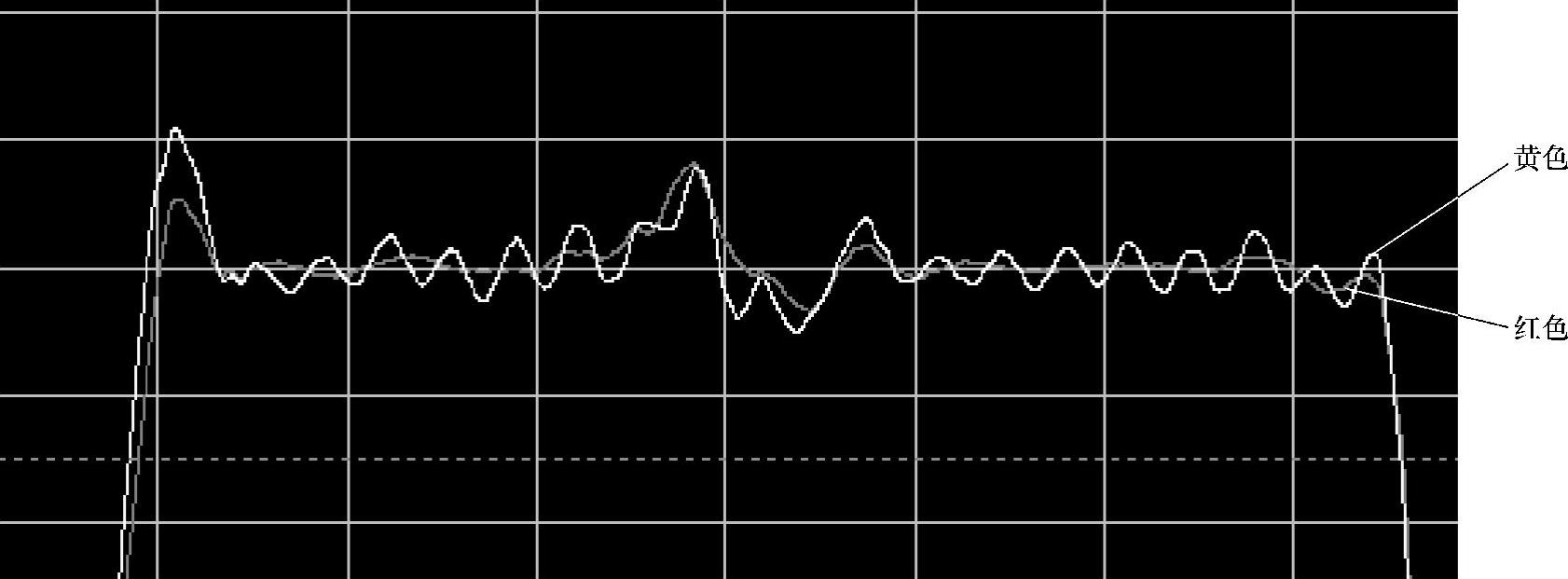

AC端接通常是先接电容再通过电阻连接到地,如果反过来就成为先接电阻再接电容到地,图5-26给出了这两种拓扑结构,电容值为200nF,电阻仍为50Ω,其结果如图5-27所示,图中红色曲线为C+R的结构,即第一个拓扑结构,接收端为IC4,黄色曲线为第二个拓扑结构中U3的接收端曲线。粗略地看两个波形区别不是很明显,基本重叠在一起,但如果将波形放到图5-28中,大概是16~20ns内高电平部分的细节显示,就可以发现红色曲线比黄色曲线稍微平滑一些,这是由于第一种拓扑中电容直接将DC电流阻隔掉,相当于比第二种拓扑少了连接电阻那一部分的分支长度,因而波形更好一些。

图5-25 戴维南端接拓扑仿真结果

图5-26 AC端接拓扑

当然选用不同的电容值,由于其充放电时间不同,所以最后接收端芯片高度电平稳定在什么值也是会有变化的。篇幅所限,不再列举其他电容值的仿真结果,但在实际应用中可以根据理论计算和仿真结果来选择合适的电容值。

图5-27 AC端接仿真结果

图5-28 AC端接仿真结果(区域放大)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。