在80386处理器中,分段存储管理是保护机制的基础,在一个存储器段内保存的信息都具有相同的属性。说明一个段的情况的所有信息都存储在一个由8个字节组成的段描述符中,这些描述则集中存放在一个由硬件识别的描述符表中。

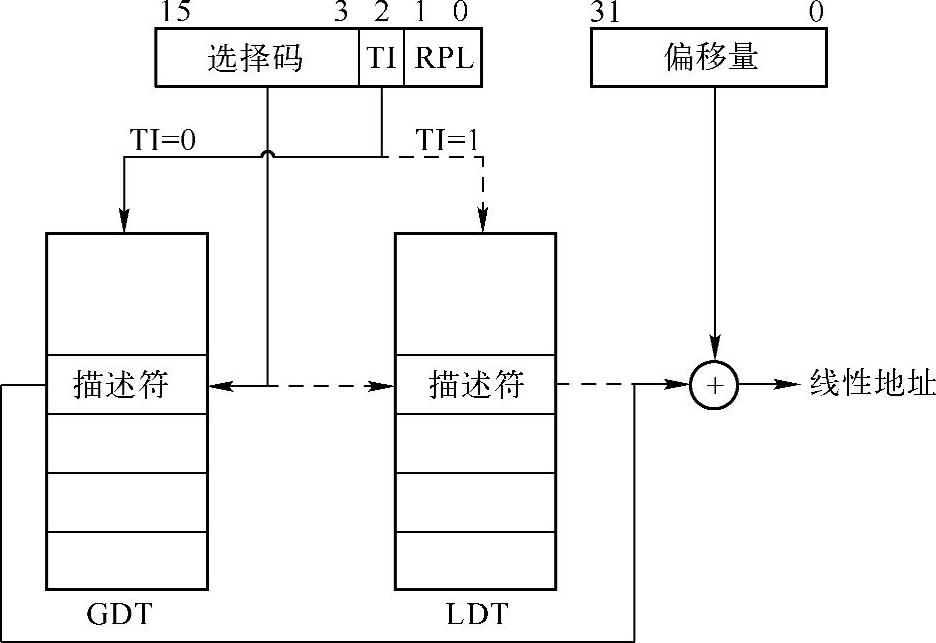

段式管理的基本思路是将进程的地址空间设计成为由段号和段内偏移组成的二维结构,其关键在于虚拟地址到实际地址的转换。在80386处理器中,该功能由存储管理部件MMU负责实现,MMU中的分段部件将逻辑地址转换为线性地址,同时对分段是否有错进行检查。在分段管理存储空间的情况下,80386处理器上运行的程序使用的是逻辑地址,该地址由一个16位的段选择符和一个32位的段偏移量组成。在保护模式下,分段部件根据段寄存器所给出的段选择符从全局描述符表GDT或局部描述符表LDT中取出对应的段描述符,将段描述符提供的32位段基地址和逻辑地址中的32位偏移量相加,从而得到线性地址。在使用分页机制的情况下,线性地址将被送给分页部件,用来产生物理地址。不使用分页机制的时候,线性地址直接作为物理地址使用。这个地址生成过程可以用图5-12表示。

图5-12 80386虚拟地址到实际地址的转换

在80386处理器中,描述符可以被分成两类:段描述符和门描述符。其中,门分成任务门、调用门、中断门和系统门四种,其作用是对一段程序到另一段程序的切换或从一个任务到另一个任务的切换进行控制,并在切换过程中自动进行保护检查,使系统正确地切换到目标程序的入口。门描述符的长度为64位,一般由一个16位的选择符、一个32位的偏移量以及16位的其他控制内容组成。

和门描述符一样,段描述符也由64位组成,包括一个32位的段基址、一个20位的段界限值和一组控制位。由于段界限可以以字节或页(4 KB)为单位,所以一个段长度的最大值根据不同的设置可以是1 MB(以字节为单位)或4 GB(以页为单位)。

由于80386处理器的地址总线宽度为32位,所以其物理地址空间为232字节=4G字节,而16位段选择符加32位偏移量组成的逻辑地址空间则应当是2(16+32)字节=64T字节。(https://www.xing528.com)

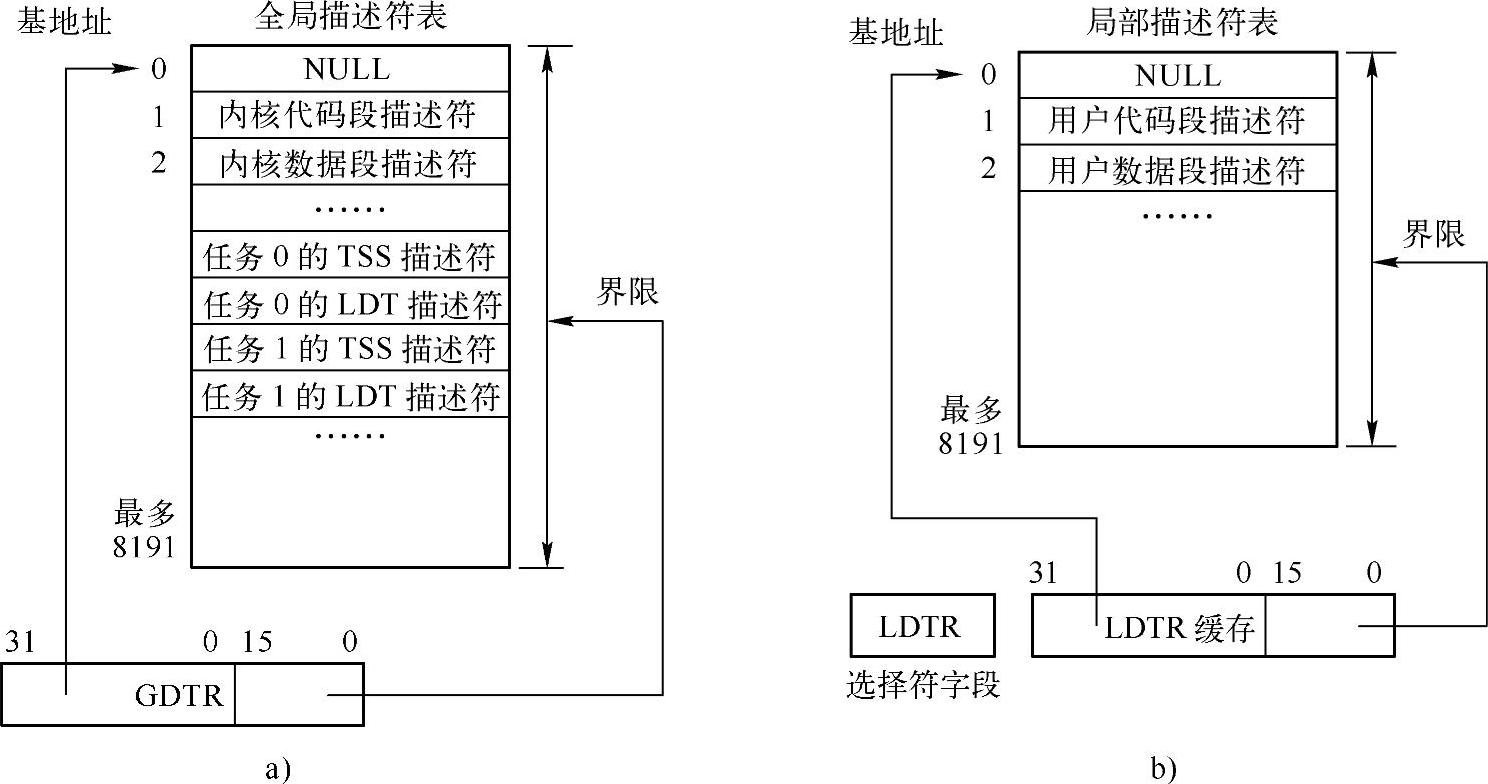

在80386处理器中,全局描述符表GDT、局部描述符表LDT和终端描述符表IDT、系统任务段TSS一样,是内存中开辟的一块特殊区域,由处理器的GDTR、LDTR等寄存器指出其基地址和长度界限(见图5-13)。GDTR、LDTR等寄存器由一些专门的特权指令加载,这些指令在特权级下由操作系统执行。由于段寄存器的选择码共有13位,描述符表的长度最大不能超过213项=8192项。在GDT中存放有系统中正在运行的各进程的TSS描述符和LDT描述符,这些描述符将在任务切换时被装入到相应的TSSR或LDTR中。每个进程有它自己的LDT,它存放在该进程独立的虚拟地址空间中。一个进程的LDT中至少包括3个描述符:作为起始标志的空描述符、用户代码段描述符和用户数据段描述符。如果进程定义了更多的段,则该进程的LDT中将包括更多的描述符。LDT由LDTR所指明,和GDTR不同的是,LDTR由一个程序员可见的用于存储16位选择符的LDTR寄存器和用户不可见的48位LDTR缓存组成,当程序从全局描述符表中根据16位选择符的值装入LDT描述符时,存储在全局描述符表中的LDT描述符会被装入到LDTR和LDTR缓存中。

图5-13 80386的全局描述符表和局部描述符表

a)全局描述符表 b)局部描述符表

为了寄存经常被使用的段描述符,80386处理器在每个段寄存器的背后设置了一个对程序员透明的64位段描述符寄存器,用来保存该段寄存器中的段选择符对应当前进程的段描述信息,以达到提高地址转换速度的目的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。