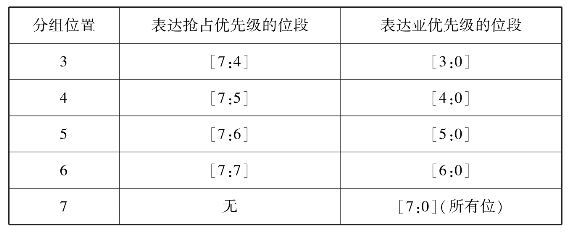

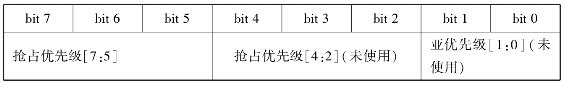

前面提到Cortex-M3支持256个优先级,但只有128个抢占级,这是为了使抢占机能变得更可控,Cortex-M3还把256级优先级按位分成高低两段,分别是抢占优先级和亚优先级。NVIC中有一个寄存器是“应用程序中断及复位控制寄存器”(内容见表3.11),它有一个位段名为“优先级组”。该位段的值对每一个优先级可配置的异常都有影响——把其优先级分为个位段:MSB所在的位段(左边的)对应抢占优先级,而LSB所在的位段(右边的)对应亚优先级,见表3.12。

表3.11 应用程序中断及复位控制寄存器(AIRCR)(地址:0xE000_ED00)

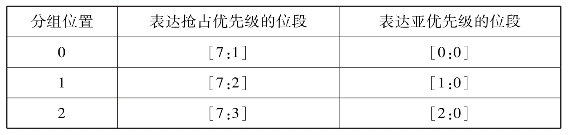

表3.12 抢占优先级和亚优先级的表达,位数与分组位置的关系

续表

抢占优先级决定了抢占行为:当系统正在响应某异常L时,如果来了抢占优先级更高的异常H,则H可以抢占L。亚优先级则处理“内务”:当抢占优先级相同的异常有不止一个悬起时,就优先响应亚优先级最高的异常。

这种优先级分组规定:亚优先级至少是1个位。因此抢占优先级最多是7个位,造成了最多只有128级抢占的现象。

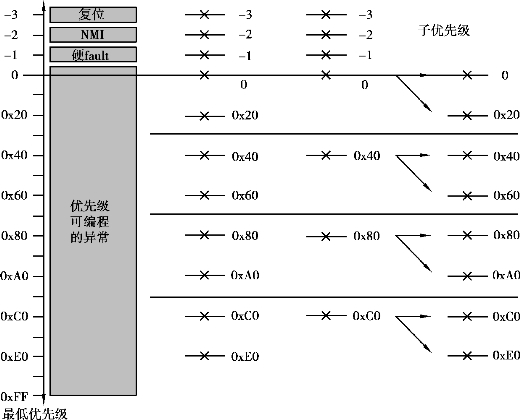

但是Cortex-M3允许从比特7处分组,此时所有的位都表达亚优先级,没有任何位表达抢占优先级,因此所有优先级可编程的异常之间就不会发生抢占——相当于除能了Cortex-M3的中断嵌套机制。但是复位、NMI和硬fault不受此影响,它们无论何时出现,都立即无条件抢占所有优先级可编程的异常。

在计算抢占优先级和亚优先级的有效位数时,必须先求出下列值:

①芯片实际使用了多少位来表达优先级;

②优先级组是如何划分的。

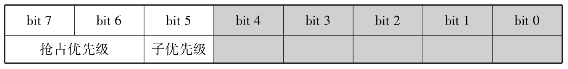

如果只使用[7:5]共3个位来表达优先级,并且优先级组的值是5(从bit 5处分组),则你得到4级抢占优先级,且在每个抢占优先级的内部有2个亚优先级,如图3.30所示。(https://www.xing528.com)

图3.30 3位优先级,从bit 5处分组时的优先级位段划分

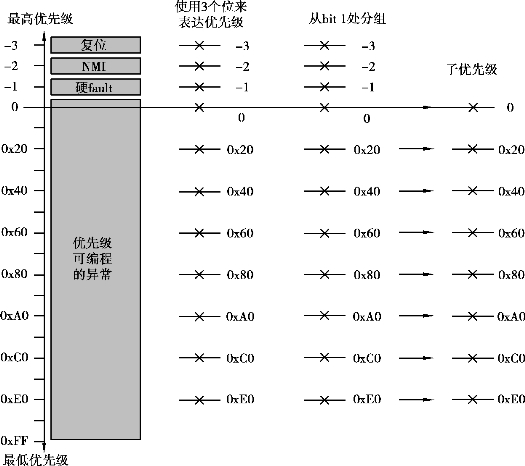

根据图3.30中演示的设置,其可用优先级的具体情况如图3.31所示。

需要注意的是:虽然[4:0]未使用,却允许从它们中分组。例如,如果优先级组为1,则所有可用的8个优先级都是抢占优先级,如图3.32和图3.33所示。

如果优先级完全相同的多个异常同时悬起,则先响应异常编号最小的那一个。如IRQ #3会比IRQ #5先得到响应。

虽然优先级分组的功能很强大,但是粗心地更改常常会改变系统的响应特性,导致某些关键任务有可能得不到及时响应。其实在绝大多数情况下,优先级的分组都要预先经过计算论证,并且在开机初始化时一次性地设置好,以后就再也不动它了。只有在绝对需要且绝对有把握时才小心地更改,并且要经过尽可能充分的测试。另外,优先级组所在的寄存器AIRCR(表3.10)也基本上是一次性设置好的,只是需要手工产生复位时才写里面相应的位。

图3.31 3位优先级,从bit 5处分组

图3.32 3位优先级,从bit 1处分组时的优先级位段划分

图3.33 3位优先级,从bit 1处分组的详细情况

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。