1.同步D触发器

在数字电路中,凡在CP时钟脉冲控制下,根据输入信号D情况的不同,具有置0、置1功能的电路,都称为D触发器。为了避免同步RS触发器输入信号R、S同时为1的情况出现,人们在RS触发器的R端与S端之间加一反相器,便构成了D触发器。

(1)电路组成及符号

图5-16所示为同步D触发器电路图及逻辑符号。

图5-16 同步D触发器电路图及逻辑符号

图5-16(a)中门G1和门G2构成基本RS触发器;与非门G3和门G4构成触发导引电路,它也是控制门。在图5-16(b)中,CP为时钟控制端,D为信号输入端,Q和 为两个互补输出端。

为两个互补输出端。

(2)逻辑功能分析

同步D触发器逻辑功能分析如下。

①当CP=0时,门G3、G4被封锁,![]() 由基本触发器的功能可知,触发器的状态Q保持不变。

由基本触发器的功能可知,触发器的状态Q保持不变。

②当CP=1时,门G3、G4被打开,![]() 触发器的输出状态随输入信号D发生翻转。由基本RS触发器的功能可知,当CP=1时,由于

触发器的输出状态随输入信号D发生翻转。由基本RS触发器的功能可知,当CP=1时,由于![]() 恰好互补,因此约束条件始终满足。

恰好互补,因此约束条件始终满足。

通过对图5-16的分析,得出同步D触发器的功能真值表如表5-10所示。

表5-10 同步D触发器功能真值表

(3)动作特点

同步D触发器有如下动作特点。

①时钟电平控制。在CP=1期间接收输入信号,CP=0期间不接收输入信号。与基本RS触发器相比,对触发器状态的转变增加了时间控制。CP=0期间,![]() 触发器状态保持不变;在CP=1期间,

触发器状态保持不变;在CP=1期间,![]() 输入信号D的变化,会引起触发器状态的改变,并且和D的状态相同。

输入信号D的变化,会引起触发器状态的改变,并且和D的状态相同。

②与同步RS触发器相比,R、S同时为0的情况不会出现,![]() 之间约束条件始终满足,触发器不会出现不确定状态。

之间约束条件始终满足,触发器不会出现不确定状态。

(4)特性方程

同步D触发器的特性方程为

![]()

(5)工作波形图

同步D触发器的工作波形图如图5-17所示。

图5-17 同步D触发器的工作波形图(https://www.xing528.com)

(6)状态转换图

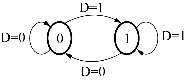

同步D触发器状态转换图如图5-18所示。

图5-18 同步D触发器状态转换图

2.边沿D触发器

同步D触发器在CP=1期间,输出同D保持一致,假如D状态发生变化,那么其输出也可能发生“空翻”,降低了触发器的抗干扰能力。为了解决这一问题,边沿D触发器(又称为维持-阻塞边沿D触发器)采用边沿触发的方法防止了“空翻”的出现,即它是仅在CP的上升沿或下降沿时刻对输入信号响应来防止“空翻”的。边沿D触发器与同步D触发器的逻辑功能相同。

(1)常用芯片及符号

集成TTL芯片74LS74是常用的双上边沿D触发器,图5-19所示为其引脚图和边沿D触发器的逻辑符号。

图5-19 74LS74引脚图及边沿D触发器的逻辑符号

(2)逻辑功能分析

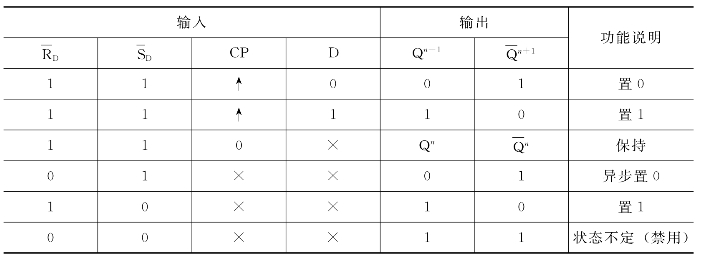

74LS74双上边沿D触发器的功能真值表如表5-11所示。

表5-11 74LS74边沿D触发器功能真值表

由表5-11可知,集成边沿D触发器设有异步复位输入端 和异步置位端

和异步置位端 低电平有效。在

低电平有效。在![]() 及CP上升沿时,实现D触发器的逻辑功能。

及CP上升沿时,实现D触发器的逻辑功能。

(3)动作特点

边沿D触发器仅在CP脉冲边沿到来时接收D端输入信号,触发器的输出状态仅取决于CP信号边沿到达前的一瞬间(这一时刻与边沿到达时的间隔趋近于零但不等于零)输入端的状态,而CP脉冲沿未到来之前和到来之后输入端状态的变化对输出端不会产生影响。正因如此,D触发器可以有效地抑制“空翻”,增强了触发器的抗干扰能力,提高了电路工作的可靠性。

(4)特性方程

边沿D触发器的特性方程为

![]()

(5)工作波形图

图5-20所示为边沿D触发器的工作波形图。

图5-20 边沿D触发器的工作波形图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。