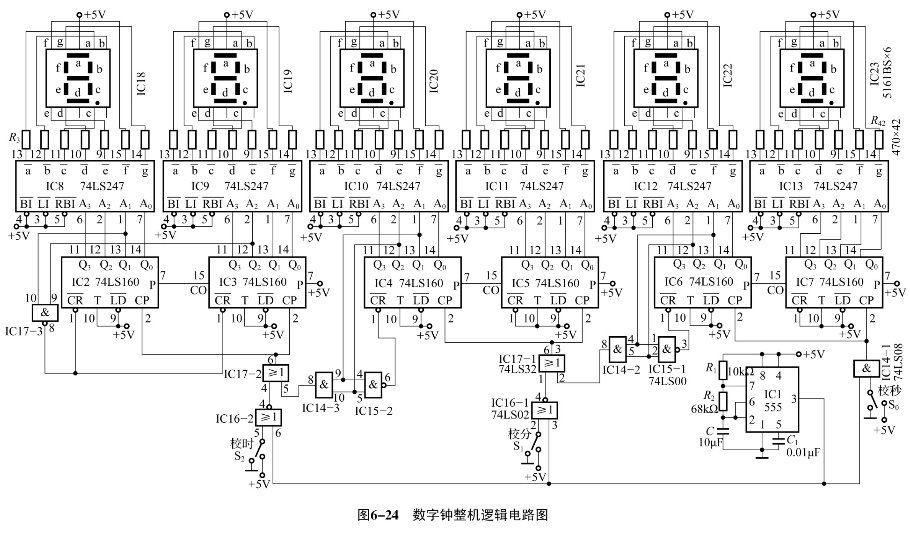

1.电路工作过程分析

该电路为24小时制数字钟电路,其原理图如图6-24所示。IC1、R1、R2、C和C1组成秒脉冲产生电路;IC7、IC13和IC23组成秒的个位计数、译码及显示电路;IC6、IC15-1、IC12和IC22组成秒的十位计数、译码及显示电路;IC5、IC11和IC21组成分的个位计数、译码及显示电路;IC4、IC15-2、IC10和IC20组成分的十位计数、译码及显示电路;IC3、IC9和IC19组成小时的个位计数、译码及显示电路;IC2、IC17-3、IC8和IC18组成小时的十位计数、译码及显示电路;S0和IC14-1组成秒校准电路;S1、IC14-2和IC17-1组成分校准电路;S2、IC16-2、IC14-3和IC17-2组成小时校准电路。

电路的工作过程是:555多谐振荡器产生秒信号,经IC14-1送往IC7和IC6,IC7按十进制对秒脉冲进行计数,当IC7计数到第10个脉冲时产生一个进位信号并送往IC6的功能保持端P,使该端为高电平1,同时IC6对CP端送来秒脉冲计数1次。此后,IC7每计数10个秒脉冲IC6计数1次,直到IC6计数到第6个脉冲,其输出端Q3Q2Q1Q0变为0110时经IC15-1产生清零信号,使其输出端变为0000,完成六进制计数。于是,IC6和IC7组合起来完成秒的六十进制计数。IC6、IC7的输出经IC12、IC13分别译码,再经IC22、IC23分别显示出符合人们习惯的六十进制数字。当IC6计数到第6个脉冲后,其Q2Q1端变为11,Q2Q1信号经IC14-2相与后,以上升沿脉冲方式送入IC17-1。由于正常计时校分开关S1接高电平5V,IC16-1输出为0,因此IC17-1在IC6计数到第6个秒脉冲时输出一个正脉冲,IC5计数1次。此后,IC6每计6个脉冲,IC5计脉冲1次,直到计满10个脉冲产生1次进位输出。IC5产生进位信号1后,IC4计数1次,直到IC4计满6个脉冲其输出端为0110时,经IC15-2产生清零信号为止。于是IC4和IC5组合起来完成分的六十进制计数。同样,IC4、IC5的计数输出经IC10、IC11分别译码,最后由IC20、IC21分别显示出来。当IC4和IC5计数到第60个分脉冲时,IC4的输出端Q3Q2Q1Q0为0110,此时与门IC14-3输出一个高电平1,由于正常计数时校时开关S2接高电平5V,IC16-2输出低电平0,因此IC17-2输出1个正脉冲,IC3计数1次。此后,IC4每计6个脉冲IC3计数1次,直到IC3计数到第10个脉冲产生自动回到零时再次重新计数。在IC3的计数过程中,IC3每计10个脉冲时产生1个进位信号1,由于正常计时校时开关S2接高电平5V,于是IC2计数1次。当IC2计数到第2个脉冲、IC3数计到第4个脉冲,即IC2、IC3计数到第24个脉冲时,IC2的Q1和IC3的Q2同时为1,IC17-3与非门输出为0,产生一个清零信号,使IC2和IC3回到零。于是,IC2和IC3组合起来完成小时的二十四进制计数。同样IC2、IC3的计数输出经IC8、IC9分别译码,最后由IC18、IC19分别显示出来。当电路需要校秒时,将开关S0接地,再将开关接5V高电平,则电路开始校秒;当需要校分时,将开关S1接地,则电路开始校分,校分完成后,再将开关S1接5V高电平;当需要校时时,将开关S2接地,则电路开始校时,校时完成后,再将开关S2接5V高电平。此电路走时的准确性取决于秒脉冲。

2.器件、器材

实训需要设备包括5V直流电源、数字电路实验装置、万用表和电烙铁,所需器件(材)明细如表6-9所示。

表6-9 计数、译码和显示电路元器件(材)明细表

3.元器件识别与测试

识读各元器件的引脚与功能;在数字实验装置上按各集成电路的检测条件搭建检测电路,检测其功能,判别其好坏;用万用表检测拨动开关S0~S2,要求通、断良好。

(1)十进制加法计数器74LS160的识别与测试

74LS160是常用的可预置的同步十进制加法计数器,其引脚图如图6-25所示,1脚为复位端(清零端),2脚为时钟脉冲端,3~6脚为数据输入端,7脚和10脚为计数保持控制端,8脚为电源接地端,9脚为预置控制端,11~14脚为计数输出端,15脚为进位输出端,16脚为电源正端。其功能表如表6-10所示。

为低电平时,不管时钟端CP信号状态如何,都可以完成清零功能;74LS160为同步预置数,即当

为低电平时,不管时钟端CP信号状态如何,都可以完成清零功能;74LS160为同步预置数,即当 为高电平,且预置控制端

为高电平,且预置控制端 为低电平时,在CP上升沿作用下,输入端数据D3、D2、D1、D0分别送往输出端Q3、Q2、Q1、Q0;当

为低电平时,在CP上升沿作用下,输入端数据D3、D2、D1、D0分别送往输出端Q3、Q2、Q1、Q0;当 为高电平,且预置控制端

为高电平,且预置控制端 为高电平时,在时钟脉冲CP上升沿的作用下,计数输出端Q3Q2Q1Q0从0000到10001计数,实现计数功能。并且当计数溢出时,进位输出端(CO)输出一个高电平脉冲,即CO=1,其宽度为Q0的高电平部分。在不外加门电路的情况下,可级联成N位同步计数器。根据引脚图和功能表,在数字电路实验装置上搭建电路检测集成计数器74LS160逻辑功能,并判断其好坏。

为高电平时,在时钟脉冲CP上升沿的作用下,计数输出端Q3Q2Q1Q0从0000到10001计数,实现计数功能。并且当计数溢出时,进位输出端(CO)输出一个高电平脉冲,即CO=1,其宽度为Q0的高电平部分。在不外加门电路的情况下,可级联成N位同步计数器。根据引脚图和功能表,在数字电路实验装置上搭建电路检测集成计数器74LS160逻辑功能,并判断其好坏。

图6-25 74LS160引脚图

表6-10 74LS160的功能表

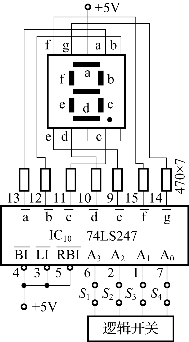

(2)74LS247和数码管5161BS的识别与检测

首先用数字万用表对数码管进行识别与检测,然后按图6-26连接好检测电路,对74LS247进行检测。检测的方法是:调节4个逻辑开关的输出电平,使74LS247输入端A3、A2、A1、A0从0000按二进制递增规律变化到1001。在调节逻辑开关的过程中,如果数码管5161BS能正常显示十进制数0~9,说明74LS247是完好的;否则74LS247是损坏的。

图6-26 74LS247的检测电路

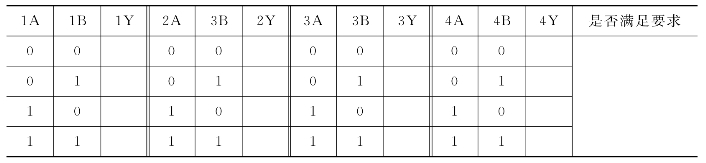

(3)与门74LS08的识别与检测

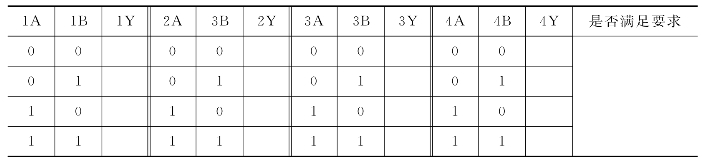

74LS08的引脚图如图6-27所示。按表6-11检测其逻辑功能。

图6-27 74LS08引脚图

表6-11 74LS08逻辑功能测试表

(4)与非门74LS00的识别与检测(https://www.xing528.com)

集成逻辑门74LS00的识别与检测按前面所学程序进行,自制表格完成数据记录。

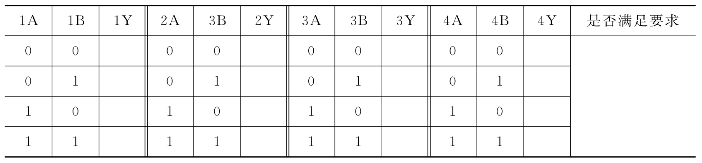

(5)或非门74LS02的识别与检测

74LS02的引脚图如图6-28所示。按表6-12检测其逻辑功能。

图6-28 74LS02引脚图

表6-12 74LS02逻辑功能测试表

(6)或门74LS32的识别与检测

74LS32的引脚图如图6-29所示。按表6-13检测其逻辑功能。

图6-29 74LS32引脚图

表6-13 74LS32逻辑功能测试表

(7)钽电解电容和瓷片电容的识别与检测

钽电解电容C和瓷片电容C1的识别与检测按前面所学程序进行,自制表格完成数据记录。

(8)色环电阻的识别与检测

色环电阻R1~R42的识别与检测按前面所学程序进行,自制表格完成数据记录。

4.电路组装

(1)元器件布局

根据图6-24所示的电路原理图,在印制电路板或单孔板上完成元器件布局。在布局时首先将数码管按人们读数习惯小时在左、分居中、秒在右的顺序两两并排在一起,且时、分、秒数码管的间距稍大于十位数与个位数的间距。再将各自的译码器、计数器依次排列在相应数码管的正下方。然后以计数器为中心对其他器件进行布局。校秒、校分、校时开关既要靠近各自计数电路,又要相对集中,且应处在PCB边缘易操作的位置。所有的集成电路标记方向应向左,整个电路布局应分布均匀美观。

(2)线路连接与焊接

布局完成后,按图6-24所示的原理图完成元器件焊接与线路连接,并将任务6.1制作的“秒振荡脉冲电路”信号输出端按图6-24进行连接。组装完成后,按原理图自检、互检有无短路、虚焊、漏焊、错焊及连线错误等情况。

5.功能检测与调试

该电路除了秒振荡脉冲电路需要调试信号频率外(任务6.1中已完成),其他部分无须调试,只要按以下要求检测电路功能即可。

(1)接通电源,检查电路计时功能。

(2)将开关S0接地,再将开关接5V高电平,检查电路校秒功能。

(3)将开关S1接地,检查电路校分功能。

(4)将开关S2接地,检查电路校时功能。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。