【摘要】:所以,在一些信号捷变速度、带宽,频谱质量要求相对折中的电路中,结合PLL频率合成技术与DDS技术的结合,将是一种解决DDS杂散的理想解决方案。在PLL+DDS系统中,应根据DDS的原理选择适当的时钟频率和输出信号频率,使DDS输出信号与边端的杂散处于相对理想状态,从而提高系统的频谱纯度。采用DDS激励PLL频率合成技术,克服了宽带系统中DDS输出频率较低和PLL频率分辨率低的缺点。

如前所述,DDS技术具有频率分辨率高、频率捷变速度快、变频相位连续等优点,但带宽和杂波抑制较差,而PLL(锁相环)频率合成技术具有宽带、高频率、频谱质量好、对杂散抑制较强等优点,但其频率捷变速度较慢。所以,在一些信号捷变速度、带宽,频谱质量要求相对折中的电路中,结合PLL频率合成技术与DDS技术的结合,将是一种解决DDS杂散的理想解决方案。

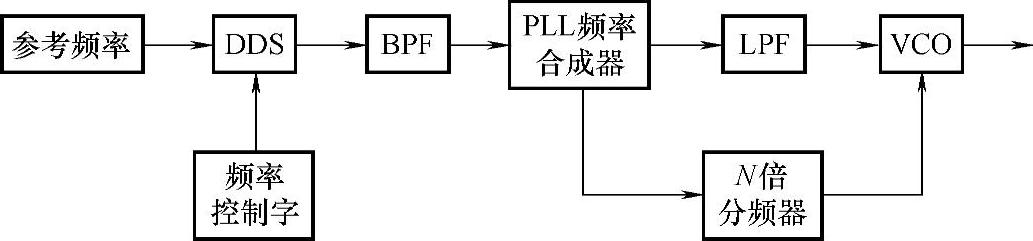

将DDS技术和PLL频率合成技术结合起来,用一个低频的DDS源激励一个PLL系统,用PLL环路将DDS信号倍频到高频信号,用滤波器滤除DDS输出信号杂波干扰,从而使系统同时具有PLL频率合成技术和DDS技术的优点,使输出的信号满足电路的需要。系统组成如图2-5所示。

图2-5 PLL+DDS系统原理图(https://www.xing528.com)

当DDS源驱动PLL时,因为PLL相当于一个高Q值的跟踪滤波器,其带宽一般不大于100kHz,所以DDS中的大部分杂散会被抑制得很好,从而使DDS输出信号中的杂散偏离主谱线距离,大于锁相环路带宽的杂散不会恶化。在PLL+DDS系统中,应根据DDS的原理选择适当的时钟频率和输出信号频率,使DDS输出信号与边端的杂散处于相对理想状态,从而提高系统的频谱纯度。

采用DDS激励PLL频率合成技术,克服了宽带系统中DDS输出频率较低和PLL频率分辨率低的缺点。通过合理设计环路低通滤波器,使相位噪声、环路稳定性等性能得到提高。同时可对电源采取滤波措施,以改善杂波抑制,这样就可设计出高性能频率合成器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。