1.设计思路

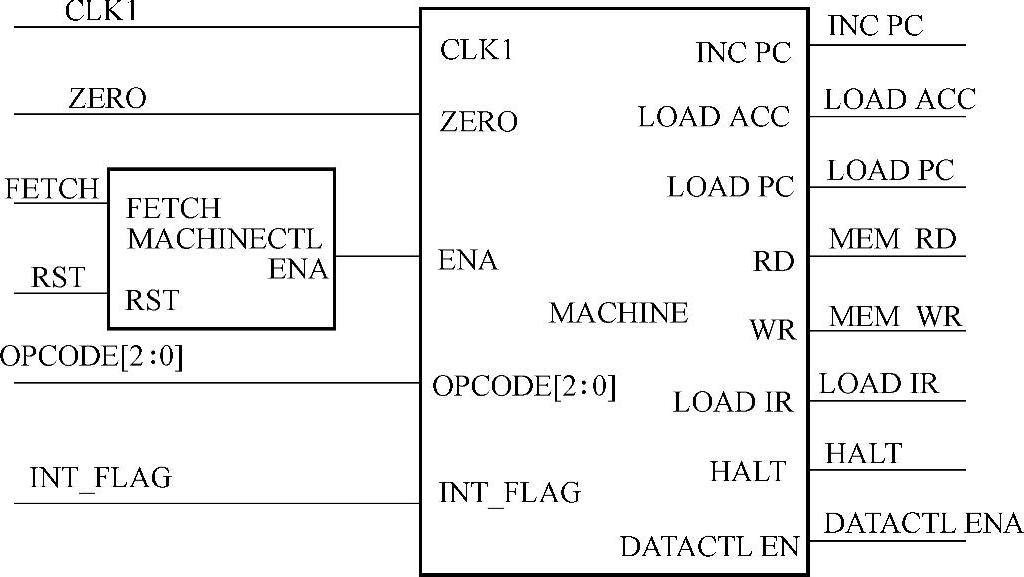

状态控制器的结构如图4-41所示,它由两部分组成:

(1)状态机(图4-41中的MACHINE部分)。

(2)状态控制器(图4-41中的MACHINECTL部分)。

图4-41 状态控制器的结构

状态机控制器接受复位信号RST,当RST有效时通过信号ENA使其为0,输入到状态机中停止状态机的工作。

状态机是CPU的控制核心,用于产生一系列的控制信号,启动或停止某些部件。状态机的当前状态由变量state记录,state的值就是当前这个指令周期中已经过的时钟数。

指令周期由8个时钟周期组成,每个时钟周期都要完成固定的操作。

(1)第1个时钟 CPU状态控制器输出—RD和LOAD-IR为高电平,其余均为低电平。指令寄存器寄存由ROM送来的高8位指令代码。

(2)第2个时钟 与第一个时钟相比只是INC_PC从0变为1,故PC增1。ROM送来低8位指令代码,指令寄存器寄存该8位代码。

(3)第3个时钟 空操作。

(4)第4个时钟 PC增1,指向下一条指令。若操作符为HLT,则输出信号HLT为高。如果操作符不为HLT,除了PC增1外(指向下一条指令),其他各控制线输出为0。

(5)第5个时钟 若操作符为AND、ADD、XOR或LDA,读相应地址的数据;若为JMP,将目的地址送给程序计数器;若为STO,输出累加器数据。(https://www.xing528.com)

(6)第6个时钟 若操作符为AND、ADD或XOR,ALC就进行相应的运算;若为LDA,就把数据通过算术运算器送给累加器;若为SKZ,先判断累加器的值是否为0,如果为0,PC就增1,否则保持原值;若为JMP,锁存目的地址;若为STO,将数据写入地址处。

(7)第7个时钟 空操作。

(8)第8个时钟 若操作符为SKZ且累加器值为0,则PC值再增1,跳过一条指令,否则PC无变化。

2.实现与仿真

(1)状态控制器 状态控制器的Verilog HDL实现代码如下:

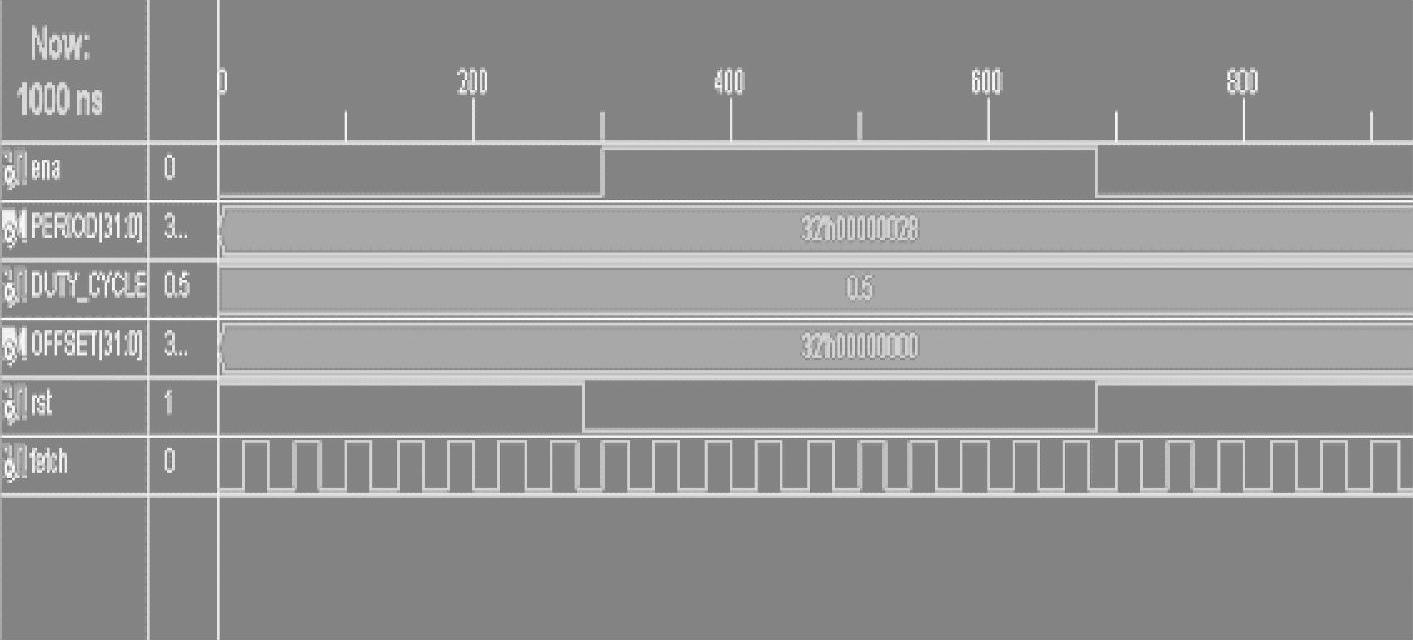

在ISE软件中进行综合仿真,状态控制器的仿真结果如图4-42所示。

(2)状态机 状态机的Verilog HDL实现代码详见光盘附件4-5。

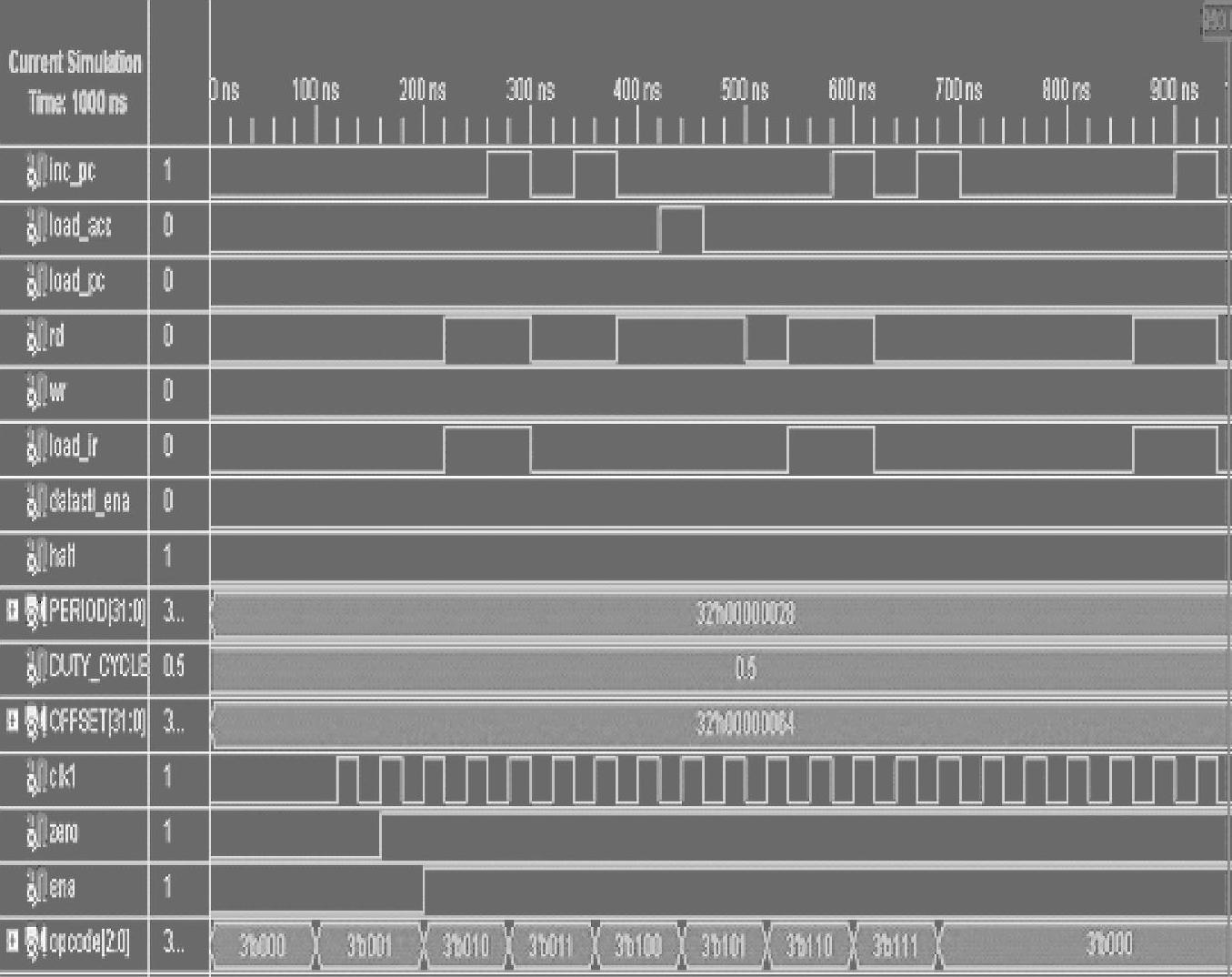

在ISE软件中进行综合仿真,状态机的结果如图4-43所示。

图4-42 状态控制器的仿真结果

图4-43 状态机的仿真结果

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。