1.基本RS触发器

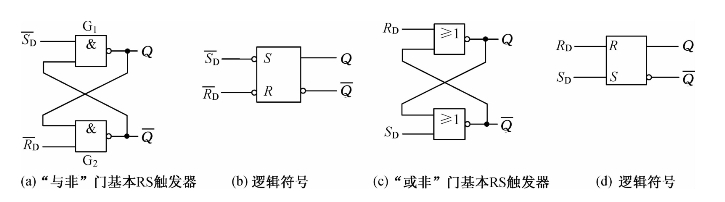

基本RS触发器是其他各种触发器的基本单元,结构最为简单,它有“与非”门和“或非”门两种组成形式.

(1)由“与非”门组成的基本RS触发器.

图8-1(a)所示是由两个“与非”门组成的基本RS触发器,它由两个“与非”门电路交叉连接而成.其中 D和

D和 D是两个输入端,Q和

D是两个输入端,Q和 是两个互补的输出端,通常规定Q端的状态为触发器的状态.例如,当Q=0、

是两个互补的输出端,通常规定Q端的状态为触发器的状态.例如,当Q=0、 =1时,表示触发器处于0状态;反之,当Q=1、

=1时,表示触发器处于0状态;反之,当Q=1、 =0时,触发器处于1状态.其工作原理如下:

=0时,触发器处于1状态.其工作原理如下:

图8-1 基本RS触发器的逻辑电路及逻辑符号

①当 =1

=1 =0时,触发器置1.因

=0时,触发器置1.因 =0,“与非”门G1的输出Q=1,“与非”门G2的输入都为高电平1,使输出

=0,“与非”门G1的输出Q=1,“与非”门G2的输入都为高电平1,使输出 =0,即触发器被置1.这时,即使

=0,即触发器被置1.这时,即使 =0的信号消失,因

=0的信号消失,因 =0反馈到G1的输入端,Q端仍保持1状态.因为是在

=0反馈到G1的输入端,Q端仍保持1状态.因为是在 端输入低电平,将触发器置1,所以称

端输入低电平,将触发器置1,所以称 端为置1端,也称置位端

端为置1端,也称置位端 端是输入低电平有效.

端是输入低电平有效.

②当 =0、

=0、 =1时,触发器置0.因

=1时,触发器置0.因 =0,“与非”门G2的输出

=0,“与非”门G2的输出 =1,“与非”门G1的输入都为高电平1,使输出Q=0,即触发器被置0.这时,即使

=1,“与非”门G1的输入都为高电平1,使输出Q=0,即触发器被置0.这时,即使 =0的信号消失,因

=0的信号消失,因 =1反馈到G1的输入端,Q端仍保持0状态.因为是在

=1反馈到G1的输入端,Q端仍保持0状态.因为是在 端输入低电平,将触发器置0,所以称

端输入低电平,将触发器置0,所以称 端为置0端,也称清零端或复位端

端为置0端,也称清零端或复位端 端也是输入低电平有效.?

端也是输入低电平有效.?

③当 =

= =1时,触发器保持原状态不变.若触发器原处于Q=0

=1时,触发器保持原状态不变.若触发器原处于Q=0 =1的0状态时,Q=0反馈到G2的输入端,使“与非”门G2的输出

=1的0状态时,Q=0反馈到G2的输入端,使“与非”门G2的输出 =1

=1 =1又反馈到G1的输入端,这样,“与非”门G1的输入都为高电平,输出Q=0,即电路保持0状态;若触发器原处于Q=1

=1又反馈到G1的输入端,这样,“与非”门G1的输入都为高电平,输出Q=0,即电路保持0状态;若触发器原处于Q=1 =0的1状态时,电路同样保持1状态.

=0的1状态时,电路同样保持1状态.

④当 =

= =0时,触发器状态不定.当

=0时,触发器状态不定.当 =

= =0时,输出Q=

=0时,输出Q= =1,这不符合Q与

=1,这不符合Q与 互补的关系.而且,当

互补的关系.而且,当 =

= =0的信号同时消失或同时变为1时,Q与

=0的信号同时消失或同时变为1时,Q与 的状态将是不定状态,可能是0状态,也可能是1状态.因此正常工作时,不允许

的状态将是不定状态,可能是0状态,也可能是1状态.因此正常工作时,不允许 和

和 同时为0.

同时为0.

基本RS触发器的逻辑符号如图8-1(b)所示,图中 端的小圆圈以及表示

端的小圆圈以及表示 、

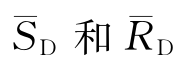

、 上面的“非”号均表示低电平有效.表8-1是由“与非”门组成的基本RS触发器的逻辑状态表.表中Qn表示触发器在接收信号之前所处的状态,称为初态;Qn+1表示触发器在接收信号后建立的新的稳定状态,称为次态.“×”号表示不定状态,即输入信号消失后触发器状态可能是“0”,也可能是“1”.

上面的“非”号均表示低电平有效.表8-1是由“与非”门组成的基本RS触发器的逻辑状态表.表中Qn表示触发器在接收信号之前所处的状态,称为初态;Qn+1表示触发器在接收信号后建立的新的稳定状态,称为次态.“×”号表示不定状态,即输入信号消失后触发器状态可能是“0”,也可能是“1”.

表8-1 由“与非”门组成的基本RS触发器逻辑状态表

由以上分析可知:基本RS触发器有两个状态,它可以直接置“0”或置“1”,并具有保持即记忆功能.

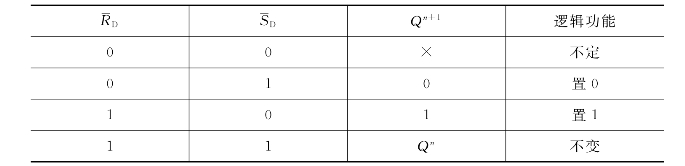

(2)由“或非”门组成的基本RS触发器.

由两个“或非”门交叉耦合而成的基本RS触发器的电路结构如图8-1(c)所示.图8-1(d)是其逻辑符号图.由图8-1(c)可以看出,此电路是高电平有效,所以用SD和RD表示,Q和 为输出端.

为输出端.

由图8-1(c)不难得出如下结论:当RD=0,SD=1时,触发器置1;当RD=1,SD=0时,触发器置0;当SD=RD=0时,触发器保持原状态不变;当SD=RD=1时,则Q= =0,这是不定状态.因为当RD和SD高电平同时消失时,触发器的输出状态是不确定的,所以这种情况是不允许的.由“或非”门组成的基本RS触发器逻辑状态见表8-2.

=0,这是不定状态.因为当RD和SD高电平同时消失时,触发器的输出状态是不确定的,所以这种情况是不允许的.由“或非”门组成的基本RS触发器逻辑状态见表8-2.

表8-2 由“或非”门组成的基本RS触发器逻辑状态表

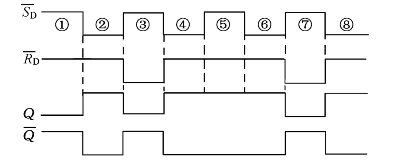

例8-1 设由“与非”门组成的基本RS触发器的输入信号波形如图8-2所示,试画出Q、 端的输出波形.设触发器初态Q=0.

端的输出波形.设触发器初态Q=0.

解 根据“与非”门组成的基本RS触发器的逻辑功能,可直接画出Q、 端的输出波形,其输出波形如图8-2所示.

端的输出波形,其输出波形如图8-2所示.

(https://www.xing528.com)

(https://www.xing528.com)

图8-2 例8-1图

为了便于说明,将图8-2分成①~⑧共八个时间段,设初态Q=0,则 =1.

=1.

2.同步RS触发器

基本RS触发器的特点是:输入信号 和

和 或SD和RD可以直接控制触发器状态的翻转.而在数字系统中,往往要求某些触发器按一定节拍同步动作,为此,产生了由时钟脉冲CP控制的触发器,只有在CP脉冲到达时,触发器才能按输入信号改变输出状态,此类触发器称为同步RS触发器,又称可控RS触发器或钟控RS触发器.

或SD和RD可以直接控制触发器状态的翻转.而在数字系统中,往往要求某些触发器按一定节拍同步动作,为此,产生了由时钟脉冲CP控制的触发器,只有在CP脉冲到达时,触发器才能按输入信号改变输出状态,此类触发器称为同步RS触发器,又称可控RS触发器或钟控RS触发器.

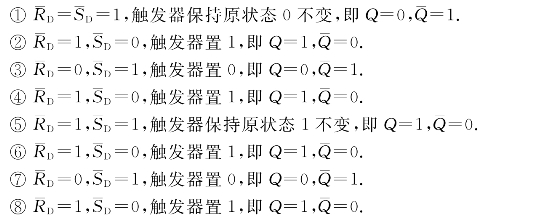

(1)电路组成.

同步RS触发器是在基本RS触发器的基础上增加了两个控制门G3、G4和一个时钟脉冲CP.图8-3(a)和(b)分别为同步RS触发器的逻辑电路和逻辑符号.R、S为输入信号端,Q和 为输出信号端.

为输出信号端.

图8-3 同步RS触发器的逻辑电路及逻辑符号

(2)工作原理.

当CP=0时,“与非”门G3和G4被封锁而输出高电平,不管S和R端的信号如何变化,触发器的状态始终保持不变,即Qn+1=Qn.

当CP=1时,“与非”门G3和G4被解除封锁,S和R端的信号可以通过G3和G4作用到基本RS触发器的输入端,使触发器的状态随S和R的状态而变.

不难分析出:若S=R=0,则Qn+1=Qn,即触发器保持原状态不变;若S=1,R=0,则Qn+1=1,即触发器置1;若S=0,R=1,则Qn+1=0,即触发器置0;若S=R=1,CP由1变为0时,触发器可能是1状态,也可能是0状态,即触发器状态不定,这种情况应避免.

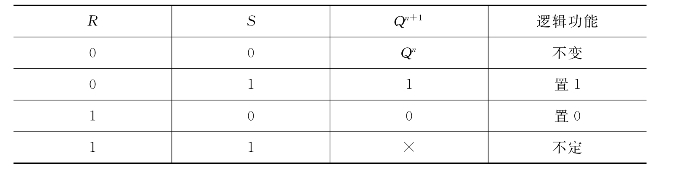

可见,当CP=1时,同步RS触发器的逻辑状态如表8-3所示.

表8-3 同步RS触发器逻辑状态表

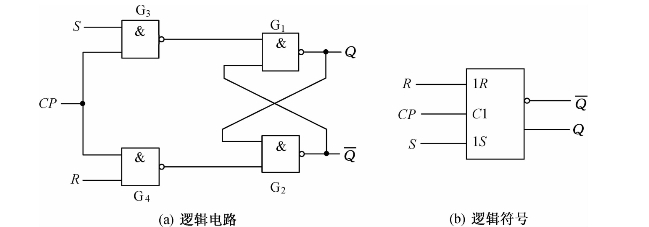

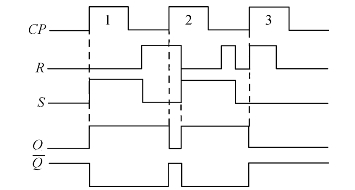

例8-2 如图8-3所示的同步RS触发器中,若CP和R、S的输入信号的波形如图8-4所示,试画出Q和 的输出波形,假定触发器的初态为0.

的输出波形,假定触发器的初态为0.

图8-4 例8-2图

解 由CP、R、S的输入波形,根据状态表可画出Q和 的输出波形,如图8-4所示.

的输出波形,如图8-4所示.

在第一个CP脉冲到来之前,即CP1=0时,R=0,S=0,触发器保持初始的0态.CP1=1时,R=0,S=1,触发器置1;CP1=0时,无论输入信号R、S如何变化,触发器维持1态不变.当第二个CP2脉冲到来时,即CP2=1,R=1,S=0,触发器置0;接着R=0,S=1,触发器又置1;当CP2=0时,无论输入信号R、S如何变化,触发器维持1态不变.当第三个脉冲CP3=1时,R=1,S=0,触发器置0;接着R=0,S=0,触发器维持0态不变;当CP3=0时,触发器维持0态不变.

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。