S7提供了8个独立的硬件中断,每一中断都具有自己的组织块。硬件中断组织块是对具有中断能力的数字量信号模块(SM)、通信处理器(CP)和功能模块(FM)信号变化进行中断响应。

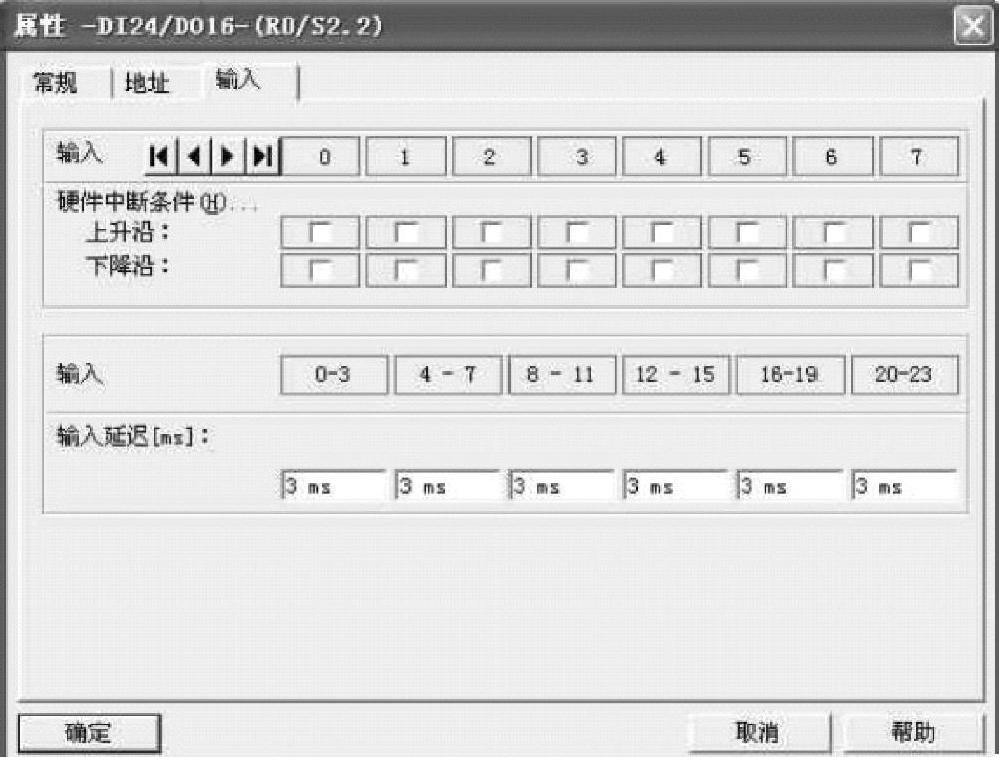

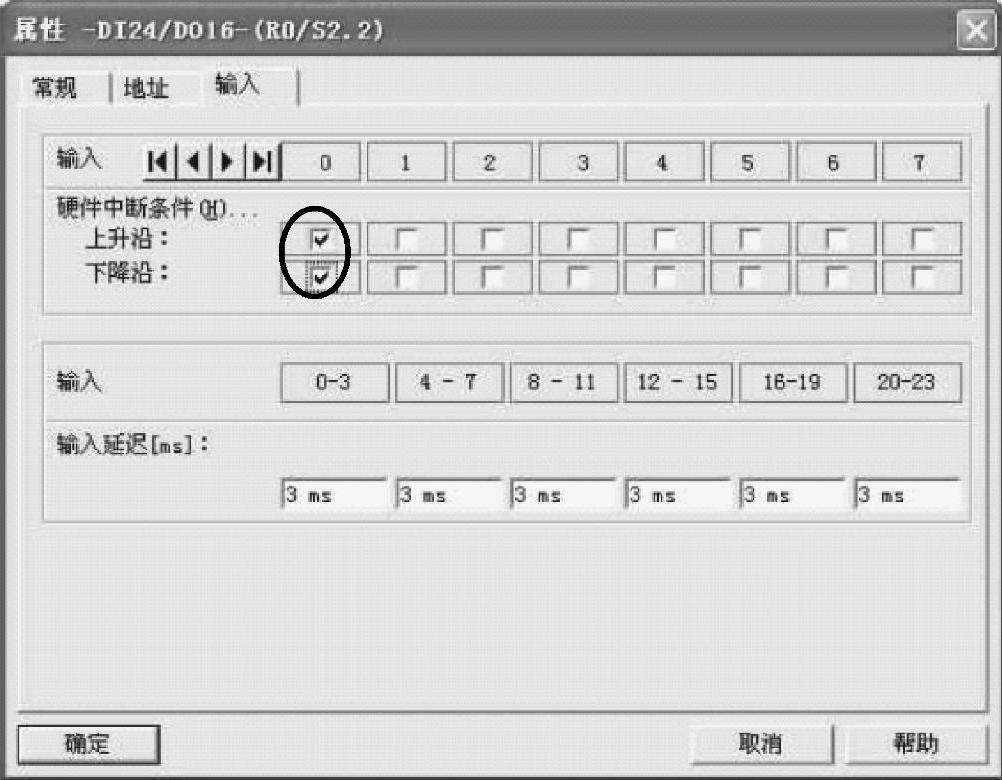

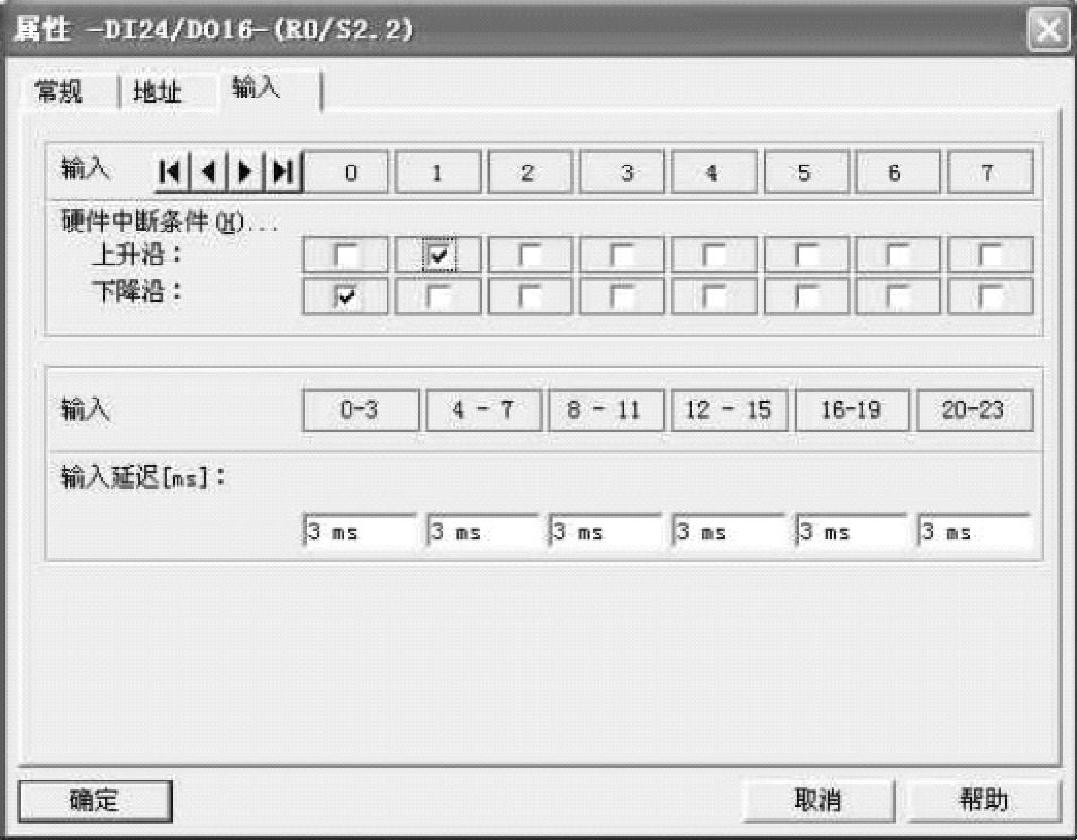

对于具有中断能力的数字量信号模块(SM),可以使用STEP 7软件在硬件组态时设置硬件中断,也可以使用SFC55~SFC57为模块的硬件中断分配参数来实现设置硬件中断。对于具有中断能力的通信处理器(CP)和功能模块(FM),可以使用STEP 7软件在硬件组态时按照向导的对话框设置相应的参数来实现设置中断。对于具有中断能力的数字量信号模块(SM)使用STEP 7软件在硬件组态时,可选择在输入信号的上升沿或下降沿触发硬件中断。如果不激活两个复选框中的任何一个,硬件中断就不会被各自的输入信号所触发,如图5-25所示;如果同时激活这两个复选框,模块会在上升沿和下降沿均产生一个硬件中断,如图5-26所示,图中选择0通道的上升沿和下降沿。

图5-25 不激活复选框

图5-26 同时激活两个复选框

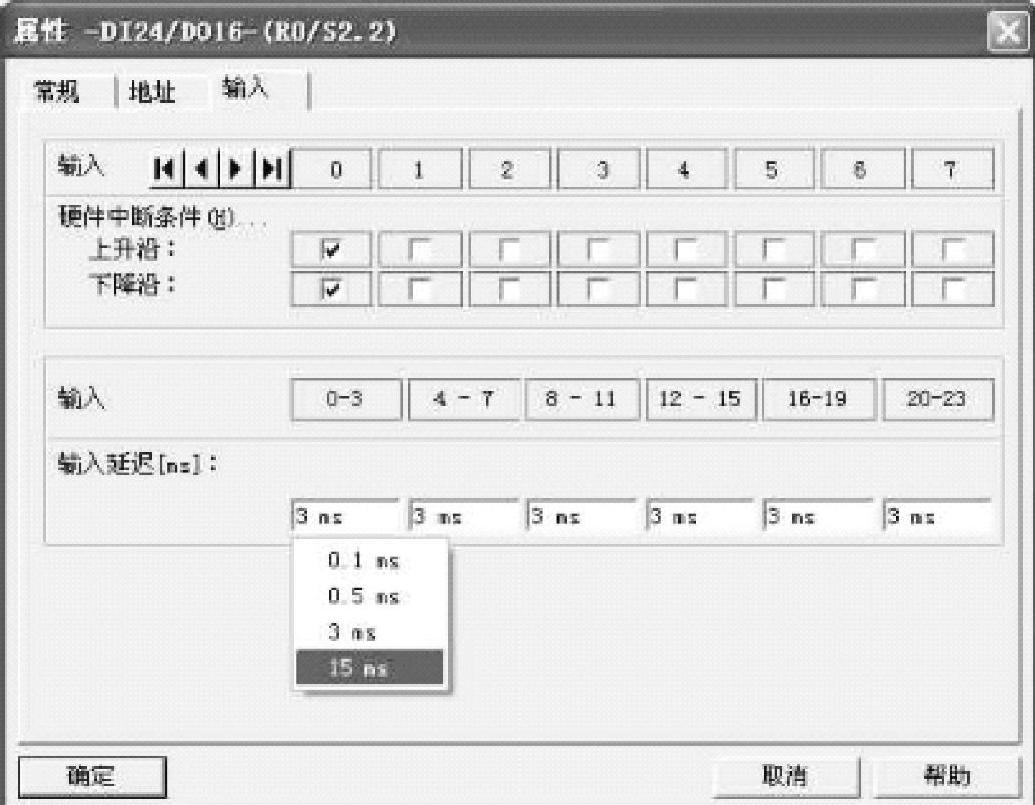

在设置数字量信号模块信号变化响应中断时,在4个通道组成的组中,可为每个通道设定一个输入延迟。方法是在输入域中单击鼠标左键,然后在打开的相关选择菜单中选择所需的延迟值,如图5-27所示,图中选择0~3通道延时时间是15ms。

硬件中断被模块触发后,操作系统将标识哪一个槽的模块以及与之相应的硬件中断OB。如果此OB的优先级高于当前激活的优先级,则将启动该OB,当执行完此硬件中断OB后,将发送通道确认信号。

图5-27 选择输入延时

如果在对硬件中断进行标识和确认的这段时间内,发生了触发硬件中断的事件时:

1)如果该事件发生在先前触发硬件中断的通道中(比如同一个输入的上升沿),则新中断丢失;

2)如果该事件发生在同一模块的另一通道中,通常不会立即触发任何硬件中断,但是此中断不会丢失,而是在确认当前激活的硬件中断后被触发;

3)如果因来自另一模块中的硬件中断而使某一硬件中断被触发,并且其OB当前处于激活状态,则将记录新请求(相当于把请求排队)并且在OB空闲时对其进行处理。

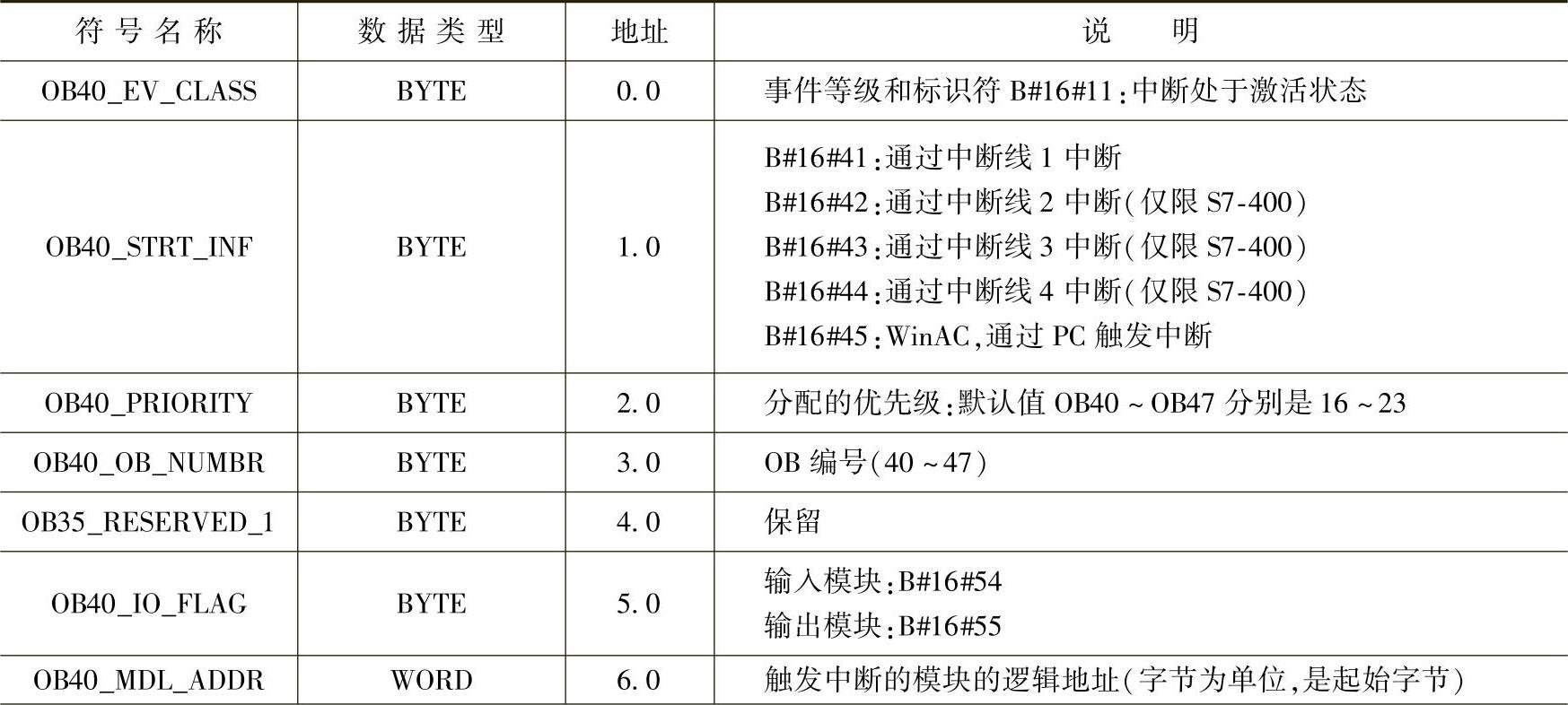

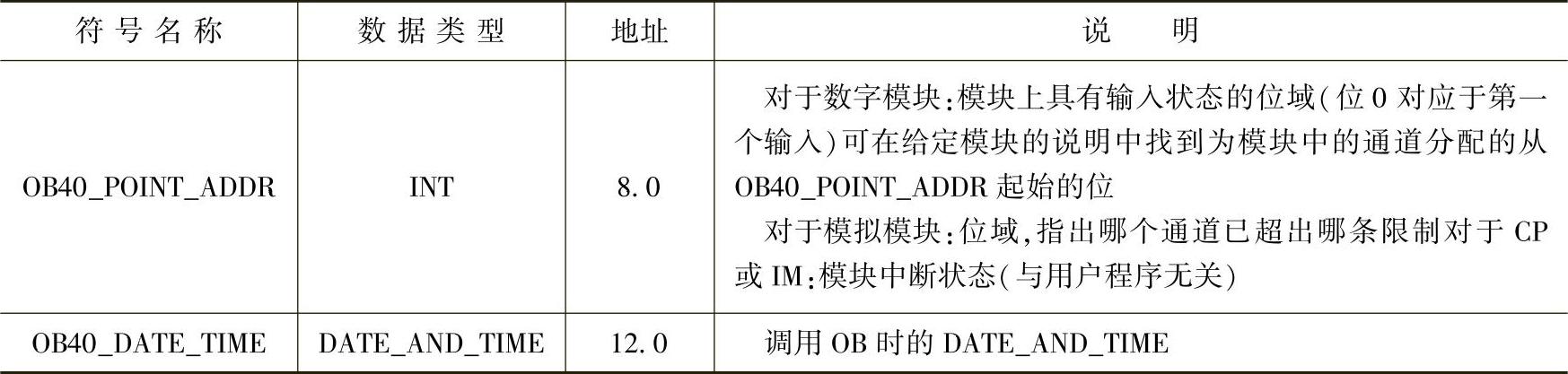

可以使用SFC39~SFC42来禁用或延迟,并重新启用硬件中断。在OB40~OB47中系统定义了如表5-6所示的本地数据,其地址从L0.0~L19.7,地址从L20.0以上的本地数据允许用户定义。表5-6中的符号以OB40为例。

表5-6 OB40中系统定义的本地数据

(续)

【例】 硬件中断组织块例子。

要求:使用CPU314C-2DP集成的I/O设置硬件中断,当I124.0下降沿时而且此时OB40被激活,则置位Q124.0;当I124.1上升沿时而且此时OB40被激活,则复位Q124.0。当I124.2上升沿时,取消激活OB40;当I124.3上升沿时,激活OB40。

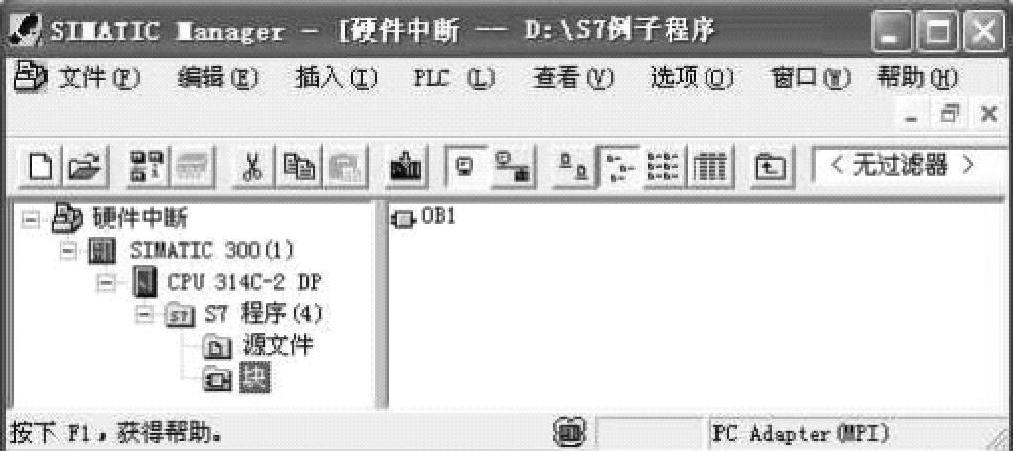

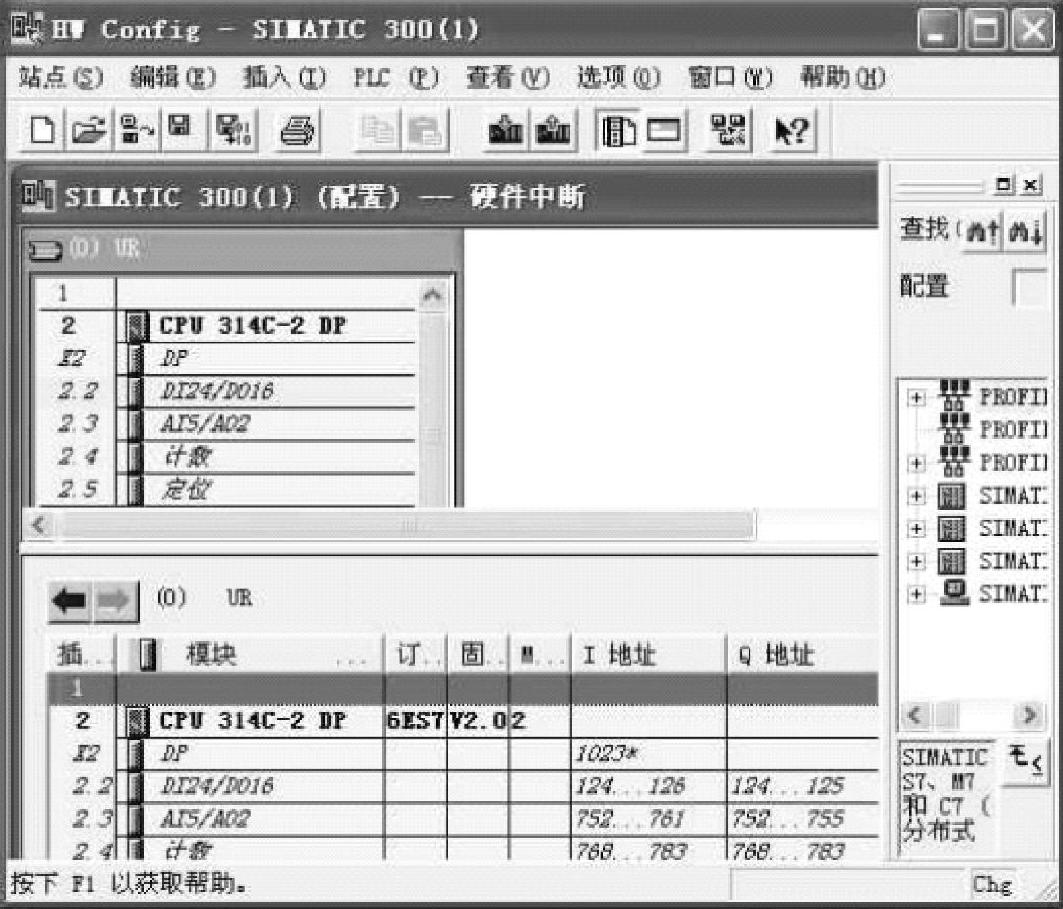

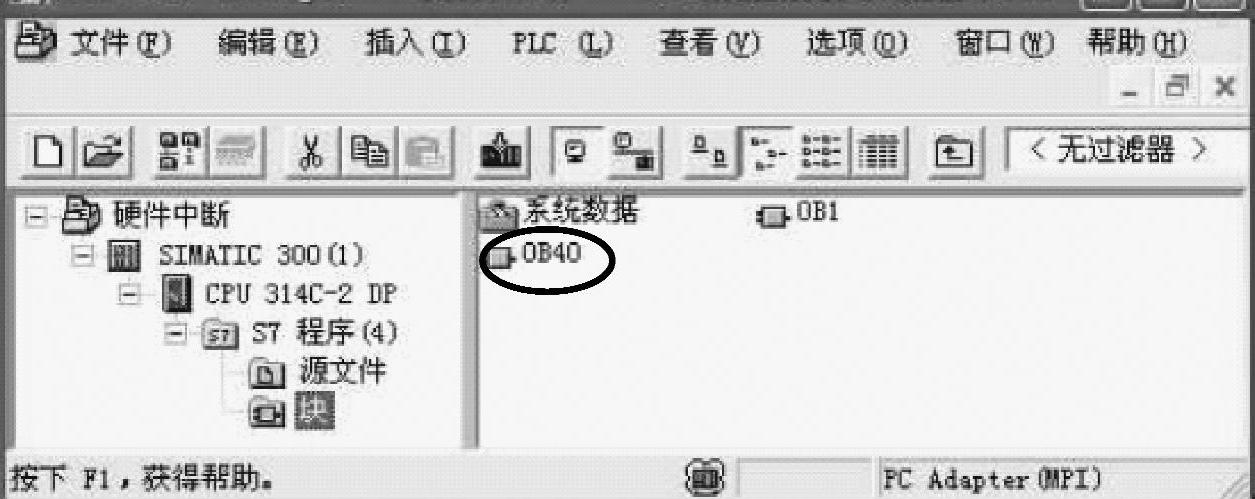

1)首先建立一个项目,并完成项目的目录配置,如图5-28所示。然后选中SIMATIC300(1),双击硬件图标打开硬件组态画面并完成硬件配置,如图5-29所示。

图5-28 新建硬件中断项目(https://www.xing528.com)

图5-29 组态硬件配置

2)在图5-29中,双击机架上CPU集成的“DI24/DO16”,打开DI24/DO16属性组态画面,如图5-30所示,使用默认地址配置输入地址是IB124~IB126,输出地址是QB124~QB125。

图5-30 选择中断条件

3)在图5-30中,选择0通道下降沿和1通道上升沿,也就是I124.0的下降沿和I124.1的上升沿触发中断事件,默认的中断组织块是OB40,然后单击“确定”。最后编译保存,生成系统数据,如图5-31所示。

4)在管理画面的块目录里插入OB40,并打开OB40,在OB40中编写如图5-32所示的程序并保存。

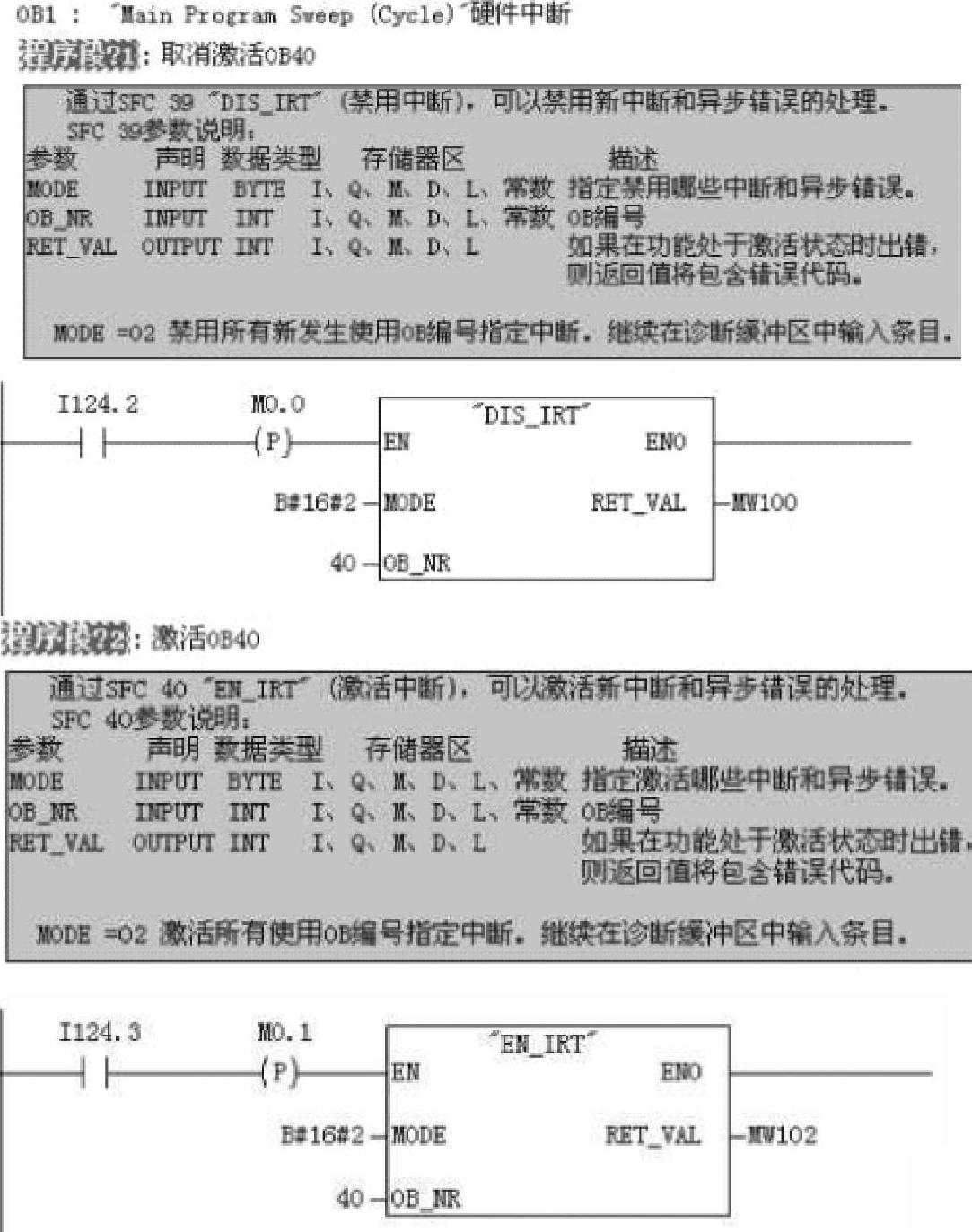

5)为了能够取消激活和重新激活中断,在管理画面的块目录打开OB1,在OB1中编写如图5-33所示程序并保存。

图5-31 完成块目录里出现OB40

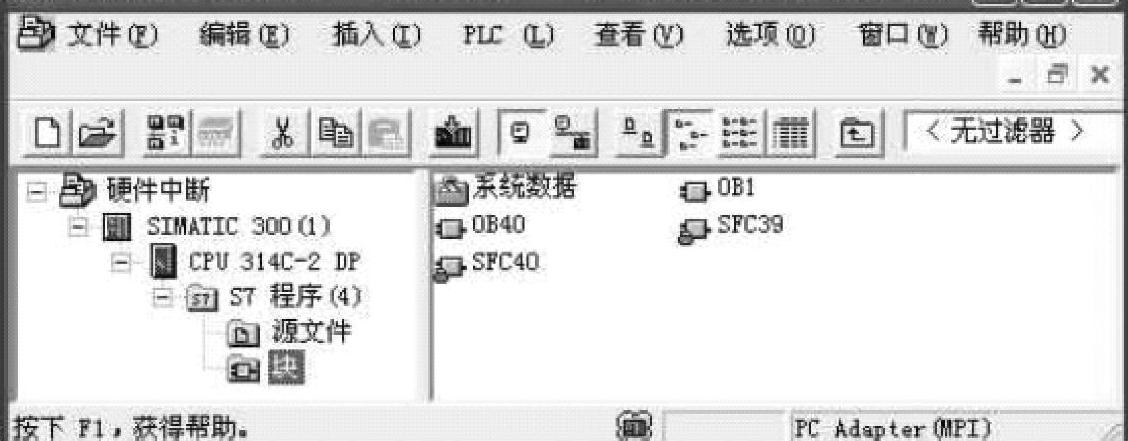

6)在管理画面把整个项目(如图5-34所示)的信息下载到CPU,然后运行CPU。

当在I124.0断开瞬间,可以看到Q124.0接通了;当在I124.1接通瞬间,可以看到Q124.0复位了。当I124.2出现上升沿后,使I124.0断开,这时Q0.0不会接通,说明OB40被取消激活了;当I124.3出现上升沿后,使I124.0断开,可以看到Q0.0会接通。当在I124.1接通瞬间,可以看到Q124.0复位了,说明OB40重新被激活了。

图5-32 在OB40里编写的程序

【例】 利用仿真软件,进行硬件中断组织块。

在管理画面把整个项目(见图5-34)的信息下载到PLCSIM仿真CPU。

1)首先把PLCSIM仿真CPU扳动到运行模式,然后单击“Execute”→“Trigger Error OB”→“Hardware Interrupt(OB40-OB47)”,在PLCSIM仿真CPU中打开硬件中断组织块,同时插入IB124和QB124的I/O面板,如图5-36所示。

2)在Hardware Interrupt OB(40-47)面板上的“Module address”栏写上124,在“Module status(POINT_ADDR)”栏写上0,然后单击“Apply”,意思是模拟I124.0产生一个脉冲信号,这时可以看到Q124.0接通了,表明OB40已经被激活并执行,这时监看Hard-ware Interrupt OB(40-47)面板上的“Interrupt OB”栏出现40字样,说明该中断执行OB40;然后在“Module address”栏保留124,在“Module status(POINT_ADDR)”栏写上1,然后单击“Apply”,意思是模拟I124.1产生一个脉冲信号,这时可以看到Q124.0复位了,表明OB40已经被激活并执行。当在IB124面板中接通I124.2,在“Module address”栏写上124,在“Module status(POINT_ADDR)”栏写上0,然后单击“Apply”,这时可以看到Q124.0不会接通,表明OB40已经被取消激活。

在IB124面板中接通I124.3,在“Module address”栏写上124,在“Module status(POINT_ADDR)”栏写上0,然后单击“Apply”,这时可以看到Q124.0接通了,表明OB40已经被重新激活了。

图5-33 在OB1里编写的程序

图5-34 完成OB1和OB40程序后管理界面出现的块目录

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。