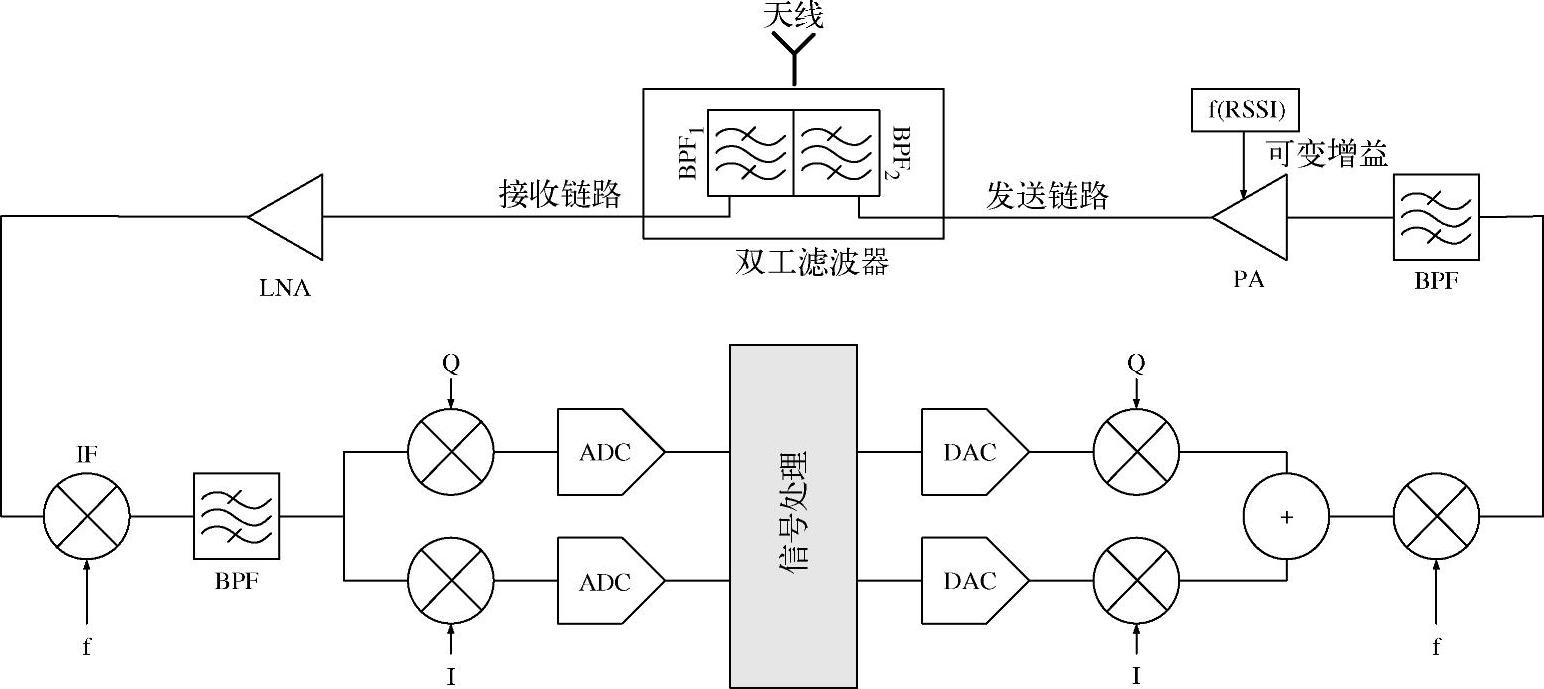

如图5.4所示,下面将首先介绍数字硬件结构的一些重要的射频组件,在上一节模拟硬件结构中讨论过的内容在此将不再重复介绍。

●中频(IF)。在恢复两路正交信号的相位之前,接收信号通常会首先下变频到一个中间临时频率。这个中间频率一般选择为几百兆赫兹。

●I/Q分路器。为了恢复两路正交信号的特征,即I/Q分量的相位,必须使用I/Q分路器。I/Q分路器一般由正弦振荡器和余弦振荡器组成,它们分别与两路信号相乘后,输出两路相互正交的信号并被进一步处理。

●模/数与数/模转换器。模/数转换器(ADC)将接收到的模拟信号转换为数字信号,数字信号的精度主要取决于量化的位数,高的量化精度将减少量化噪声,但相应的成本也较高。同样,在发送之前,数字信号需要通过数/模转换器(DAC)转换为模拟信号。

●数字信号处理。实际信号一般以数字的方式进行处理,但也需要相应的硬件配置支持,如:匹配滤波器、微处理器、内存、时钟等。采用什么样的数字结构是很重要的,如可以采用FPGA、DSP或ASIC等。现场可编程门阵列(FPGA)是一种通用的可编程器件,近些年来,FPGA在处理速度和复杂性方面的进步使得它很有竞争优势。数字信号处理器(DSP)可以以适当的运行速度和功耗执行复杂的数字信号处理任务。专用集成电路(ASIC)是针对特定目的设计的集成电路,所以不仅有合理的功耗和较低的复杂度,同时能提供很高的处理速度。一般的收发机硬件结构中,通常选择FPGA来处理采样阶段比较计算量比较大的过程,如匹配滤波、多径延迟估计、去扰和解扩频、积分、偶尔也用于信道估计;选择一片或多片DSP来执行符号级的处理,如检测、Rake合并、傅里叶变换等。(https://www.xing528.com)

另外选择定点还是浮点处理结构同样很重要。定点处理通常用固定的比特数来表示每一个数值。例如,用16 bit来表示有符号数,其范围为-32768~32767。浮点处理结构一般使用最少32 bit来存储每个数值,因此可以达4294967296个量程。浮点运算的关键问题是所表示的数值不是等间隔的,一般来说,两个极值间的数值不是均匀分布的,这导致任意两个数值间的差值比数值本身小约1亿倍。定点结构的优势是成本稍低些,浮点结构则具有高精度、宽动态范围、更短开发时间的优势。但不论定点还是浮点结构,数字信号处理单元总是再生中继结构中最昂贵的器件之一。下面我们将采用上述组件实现数字硬件结构的中继。

图5.4 数字中继硬件结构实现:再生译码和转发(DF)中继协议

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。