首先简要说明应用场景、接入方法、物理层协议的选择,这些因素影响了数字调制解调器的设计。

5.5.1.1 场景选择

下面我们比较辅助中继和协同中继在分别使用AF和DF中继协议、纯模拟硬件和数字硬件结构时的实现复杂性。因此有如下4种中继场景:

●辅助性AF协议的模拟硬件实现(s-AFa):这种简单的放大转发协议不需要进行复杂性和内存量估计,不过,射频电路的功耗是需要单独考虑的。

●辅助性AF协议的数字硬件实现(s-AFd):这里将对以数字硬件实现AF协议的功耗、内存需求进行量化分析。

●辅助性DF协议的数字硬件实现(s-DFd):这个场景下的分析要考虑到复杂的译码和转发协议的影响,因此复杂度、内存与功率消耗的分析过程将会考虑UMTS PHY协议中一些重要因素。

●协同性DF协议的数字硬件实现(c-DFd):在此场景下,中继节点本身就是一个终端,需发送自身业务。与上述场景相比,这样的中继需要电池供电,但电池电压是随着时间而非线性降低的,因此对其进行复杂性分析更为重要。

在此,我们假设模拟硬件方式的中继设备由5.2.1节中介绍的组件组成,而数字硬件方式的中继设备由5.3.1节中介绍的组件组成。

5.5.1.2 接入方式的选择

这里采用了3G UMTS系统UTRA FDD模式,上下行通信分别在不同的频段,通过直接序列CDMA来保证上行的多用户接入。

由于FDD上下行分别采用不同的频段,因此运营商一般分配1~3个5 MHz的载波频段。正如1.6.2节中讨论的,这意味着中继的双工必须严格限定与原FDD系统设计相符合。图1.21给出了一个CDMA实现的例子,还有一种方法是,中继可以采用另外一个专用下行信道来重传信号。

发射功率对于接入协议的性能有很大的影响。基站(BS)的下行发射功率一般限定在43 dBm(单载波20 W),中继不能采用如此大的功率,否则会对距离较近的终端产生很大的干扰。也正因为如此,中继发射虽然是在下行链路,但发射功率应该参照终端(MS)的上行最大发射功率。当前,只有2级(最大发射功率27 dBm)、3级(24 dBm)和4级(21 dBm)的终端(MS)发射功率是被许可的,在这里选择了4级发射功率。

5.5.1.3 链路层协议的选择

UMTS系统中的数据由物理信道来承载,物理信道具有特定载波频率、扰码、信号编码(可选)和起始时间(或持续时间),持续时间通常为0.26 μs码片的整数倍。标准中采用码片的倍数有:①时隙(一个时隙相当于2560个码片);②HSDPA数据传输子帧(一个子帧相当于3个时隙,或7680个码片);③无线子帧(相当于15个时隙,或38400个码片,或10 ms);④语音或数据传输时间间隔(TTI)(长度由具体实现决定,但只可取10、20、40或80 ms)。

下行专用物理信道(DPCH)专门用来传输数据和/或语音。对每一个TTI,即10、20、40或80 ms,DPCH的数据以传输块的方式被送到编码和复用单元。在链路层帧结构中下述处理是非常重要的:循环冗余校验(CRC)、信道编码、交织和调制;更多的相关内容在文献[516]中可以找到。专用信道采用用户指定的可变扩频序列(牺牲数据速率换取可靠性)和四相相移键控(QPSK)调制。

HSDPA中大量数据的传输则是由高速物理下行共享信道(HS-PDSCH)承载的。HS-PDSCH采用固定扩频因子16,从预留的码集中分配一个码字给一个HS-PDSCH信道。多码传输是允许的,可以分配给多个不同的码字供用户并行使用。调制方式可采用QPSK或16QAM。

最后,位于UMTS系统频段中间位置的信道是公共导频信道(CPICH)。通过改变CPICI信道的发射功率可以控制小区的覆盖范围。另外,CPICH信道也可以用做信道估计。采用SF=256和预定义的比特序列,传输速率为30 kbit/s。(https://www.xing528.com)

5.5.1.4 数字调制解调器设计

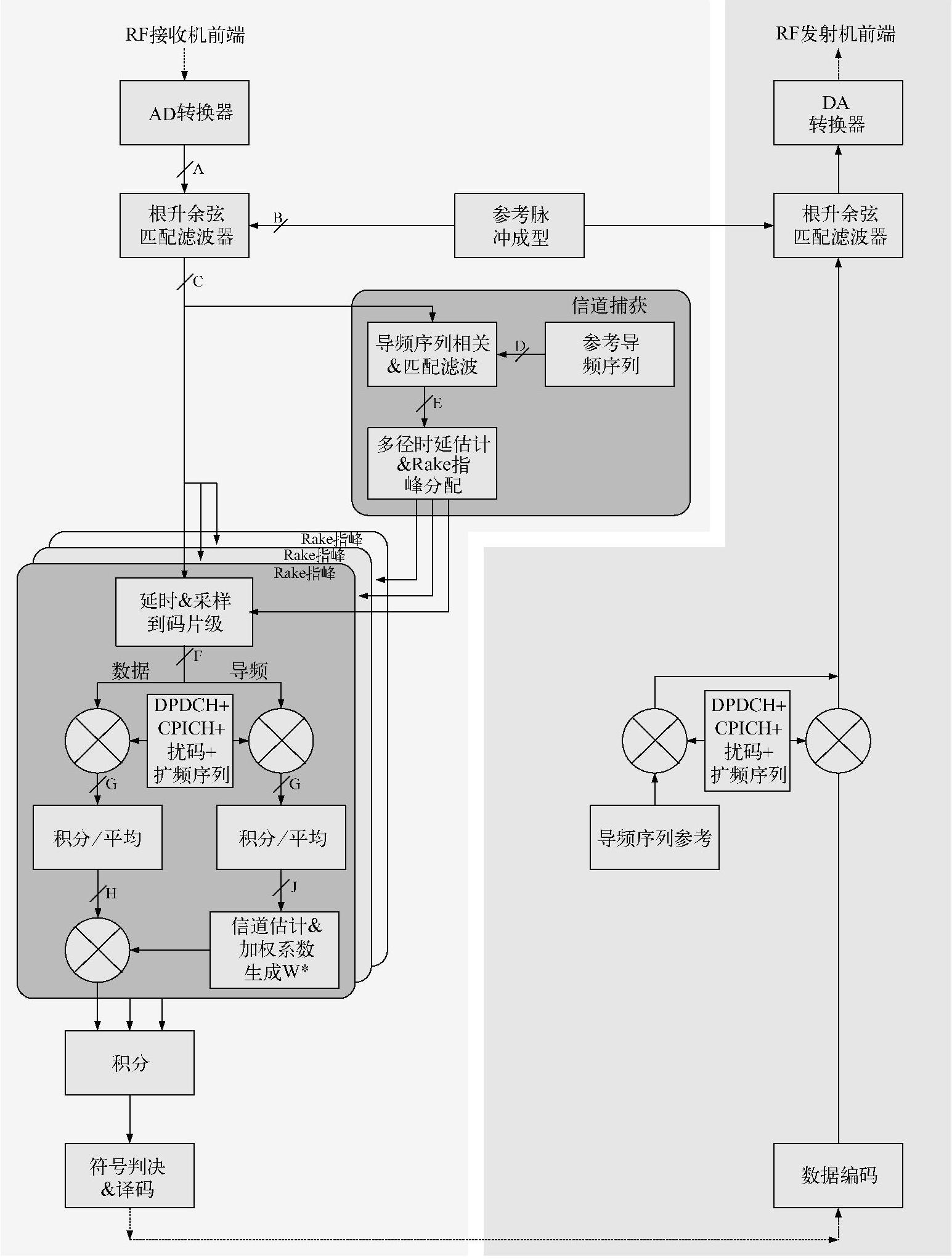

基于上述关于链路层的分析,图5.6给出了一个典型的数字中继的实现。接收端的处理单元包括:模数转换、匹配根升余弦滤波器、信道捕获(部分或全部)、信道估计、不同的检测算法、Turbo或格型信道译码器、解交织等。在图中,检测过程采用了基于最大比合并的Rake接收机和一个具有信道迭代编解码功能的复杂的多径干扰消除器[518]。

图5.6 UMTS数字中继,采用Rake接收机和MRC检测器

就复杂度计算而言,与调制解调模块工作的采样速率有着很大的关系。采样比特与码片级的处理过程无疑是复杂的,因此设计的首要目标是尽量减少以下这些过程:

●模拟信号。射频(天线收发,中频,低噪放,模拟滤波器,A/D输入和D/A转换输出)的输入和输出信号都是模拟信号。

●采样速率。工作在采样速率的处理过程包括:RRC(根升余弦)滤波器(A/D转换器输出的数据送匹配滤波器中;采样速率因为大于码片速率,可使得捕获单元能获得更好的时间分辩率)、捕获(基于CPICH进行相关运算来估计多径延迟,并且应该避免在灾里实现信道估计)和采样/保持(RAKE指峰上的输入信号必须延迟适当的样值,然后以码片速率进行采样)。

●码片速率。工作在码片速率的处理过程包括:扩频和加扰、合并(解扩器的输出必须在一个符号长度上进行平均或合并)。

●符号速率。工作在符号速率的处理过程包括:信道估计、接收信号流的合并操作。例如不同的Rake指峰、部分交织器。

●比特速率。工作在比特速率的处理过程包括:信道编码、速率匹配、交织与CRC操作

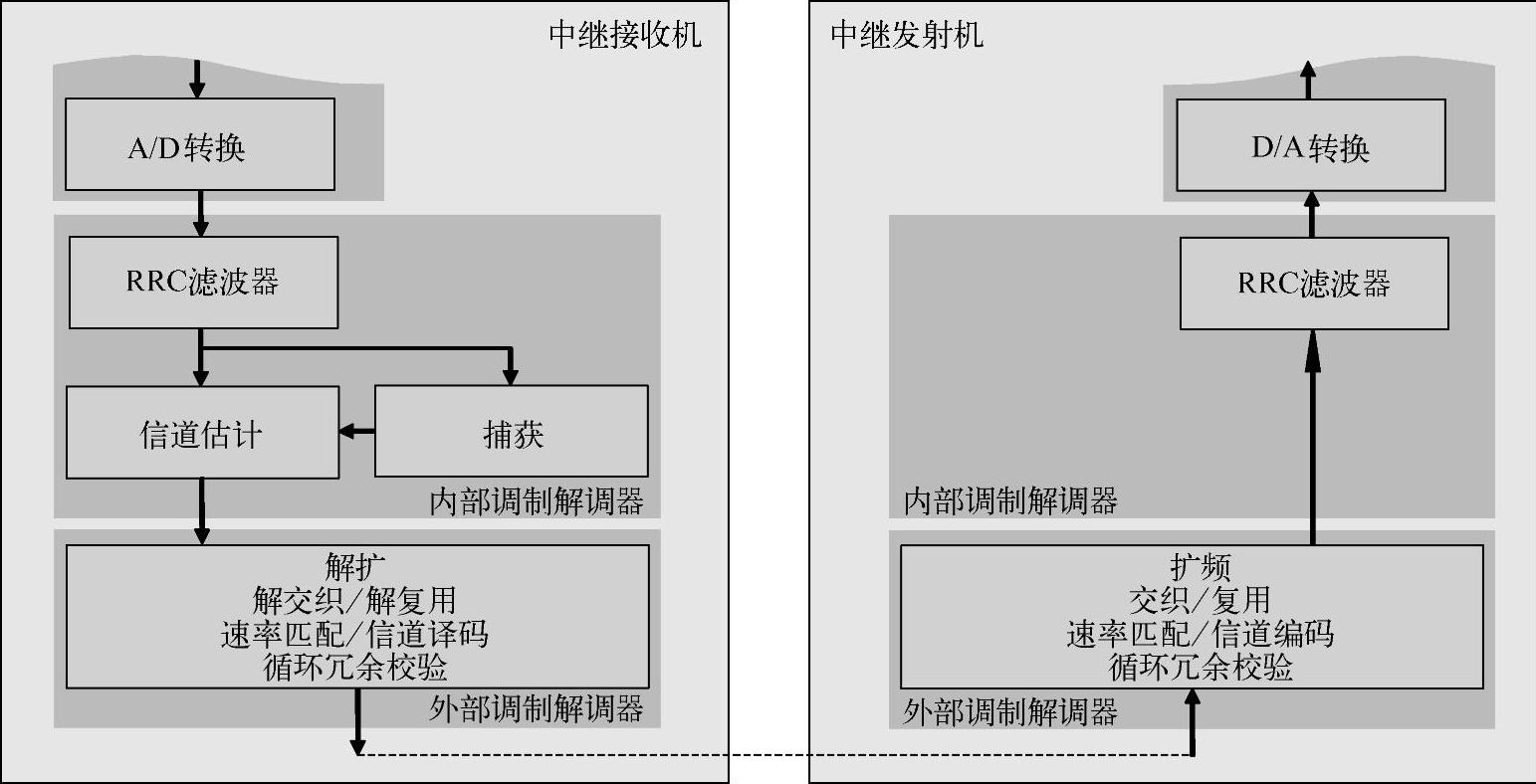

基于这些信号速率,可以将一个调制解调器从结构上划分为内部调制解调器和外部调制解调器。前者一般工作在符号速率以下,而后者通常工作在符号速率及以上。典型的数字调制解调器的模块设计如图5.7所示。

图5.7 典型的数字调制解调器模块设计:基于UMTS的中继

●内部调制解调器:包括根升余弦匹配滤波器、接收端的多径延迟估计与Rake指峰分配,以及信道估计。

●外部调制解调器:包括(解)交织器、(解)复用器、速率匹配器、信道编码译码(Viterbi或Turbo)和CRC。

对于数字硬件结构,假设信号处理板上的逻辑运算单元(ALU)可在每个时钟周期内执行4条指令,记为4 ALU。另外,数据表示为16位复数,加法和乘法也应具有适当的复杂度[1]。为了便于分析,假定这样一个单独的数字硬件结构中不包含用于移动终端的专门电路部分。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。