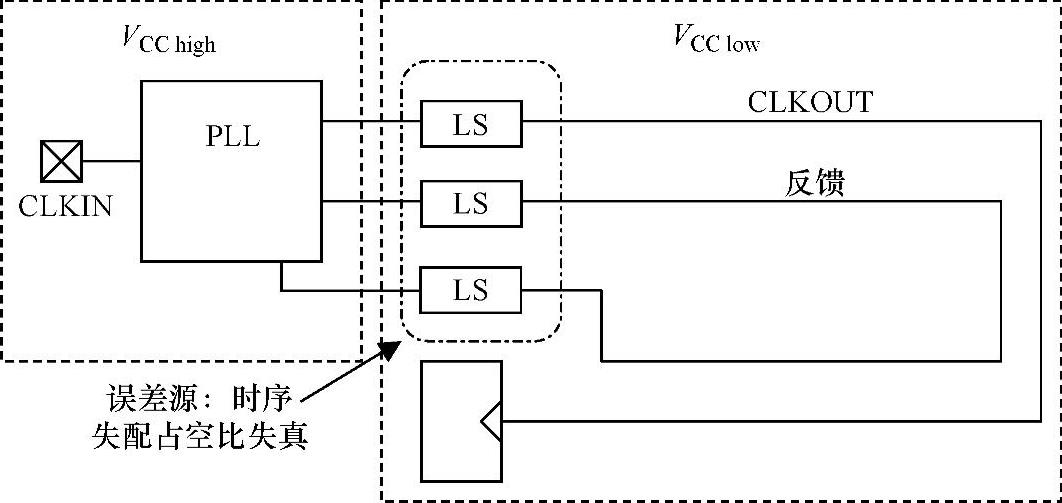

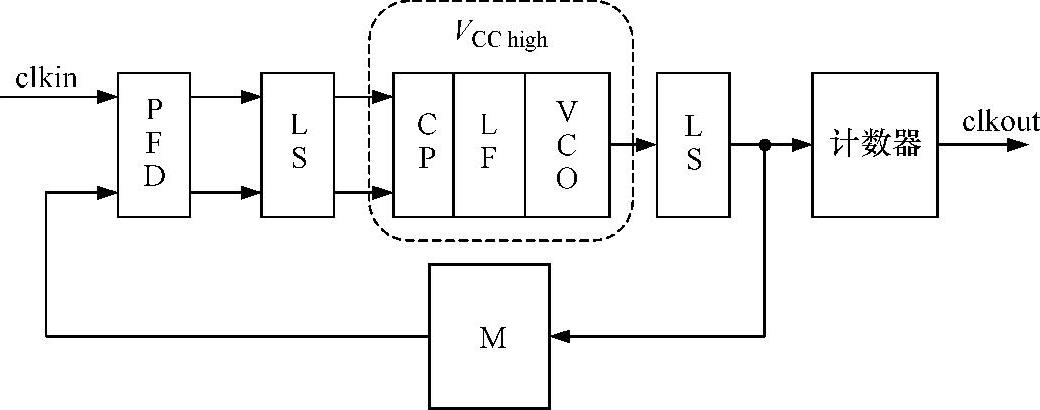

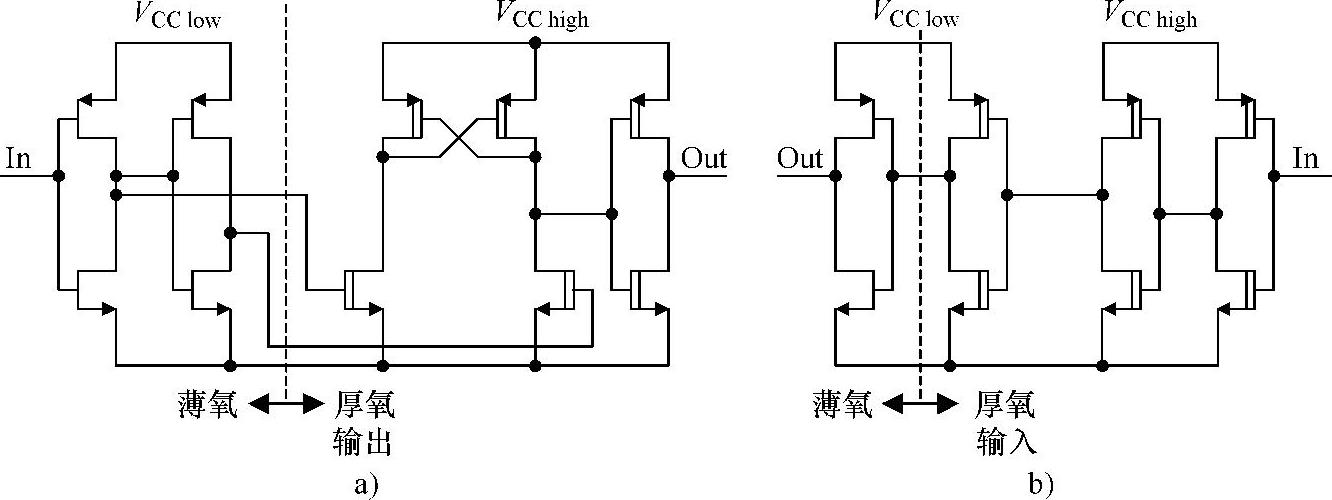

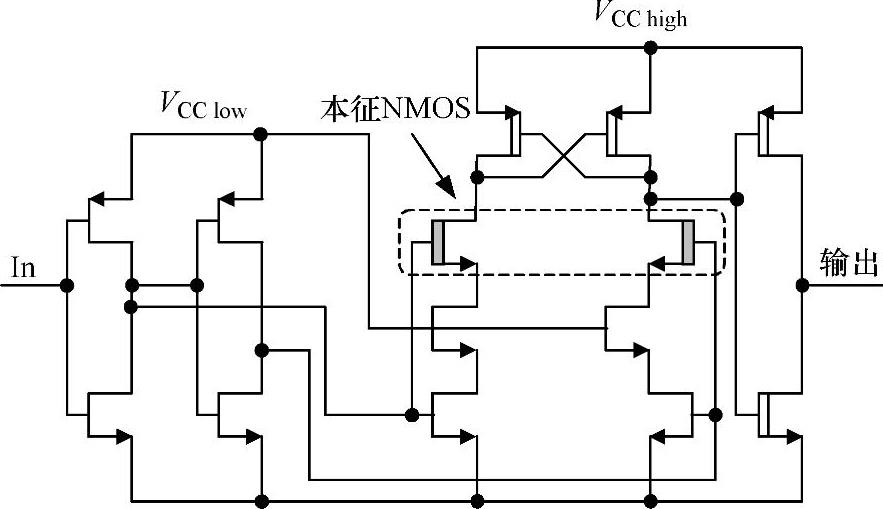

第二种选择是在模拟模块和一些可能的数字模块中使用氧化层较厚的器件,然后将电平转换到较低的核心电压电平值。这种方式的优点是能增加模拟电路的裕度,可以采用电流镜和增益级的级联连接以增加抗噪声能力。栅泄漏问题会急剧减小,源漏泄漏电流也同样会减小。但是采取这种方法会带来两个问题。首先,模拟或混合信号模块可能在某点与核心部分连接,这就要求采用一个电平转换器。对数据转换器,这些电平转换器本身不会存在问题,但是需要从整个系统的角度考虑问题。数据转换器的参考时钟可能来自于另一个时钟信号。如果这个时钟来自于核心部分的电源,则必须进行电平转换。该电平转换又会带来一个额外的噪声点,增加了参考时钟的抖动或使占空比退化,这会减小数据转换器的精确度,尤其是当占空比对设计非常重要时。如前面已经讨论过的,相似的问题也会在PLL电路中出现。图4-10所示为一个可能的PLL结构图,其中PLL使用了厚氧器件并且电平转换(LB模块)将输出时钟转换到核心电路的电压电平。图4-11所示为第二种PLL架构,其中仅核心模拟单元采用厚氧器件,当这些核心单元和PLL中其他数字部分之间转换时,使用电平转换。这个架构仍然有问题,因为电平转换会引起占空比问题。图4-12所示为一个在许多应用中采用的传统的电平转换器,图4-13所示为一个最近开发的先进电平转换器,它采用厚氧本征NMOS器件从而避免了电压较高的VCC电源对薄氧器件的影响。这个厚氧本征NMOS器件有一个非常低的阈值电压,一般接近于0,使得薄氧器件可以作为两个电源域之间的转换点,这有助于减小厚氧器件的阈值电压问题。

图4-10 可能的PLL架构(整个PLL由较高电压的电源供电而核心部分由较低电压的电源供电)

图4-11 可能的PLL架构(仅PLL核心部分由较高电源电压供电而其余逻辑部分由较低电源电压供电)

(https://www.xing528.com)

(https://www.xing528.com)

图4-12 传统的电平转换器

a)电平抬高 b)电平降低

图4-13 新的电平转换器,能对1.2V器件提供较大的保护(来源于参考文献[17])

从全局设计的观点来说,最好是所有电路都与核心电压匹配,特别是如果可能的话,锁相环也应该这样。这一目标的实现一方面取决于特定的应用情况,还要考虑应该如何调整架构以缓解每一种方式存在的问题。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。