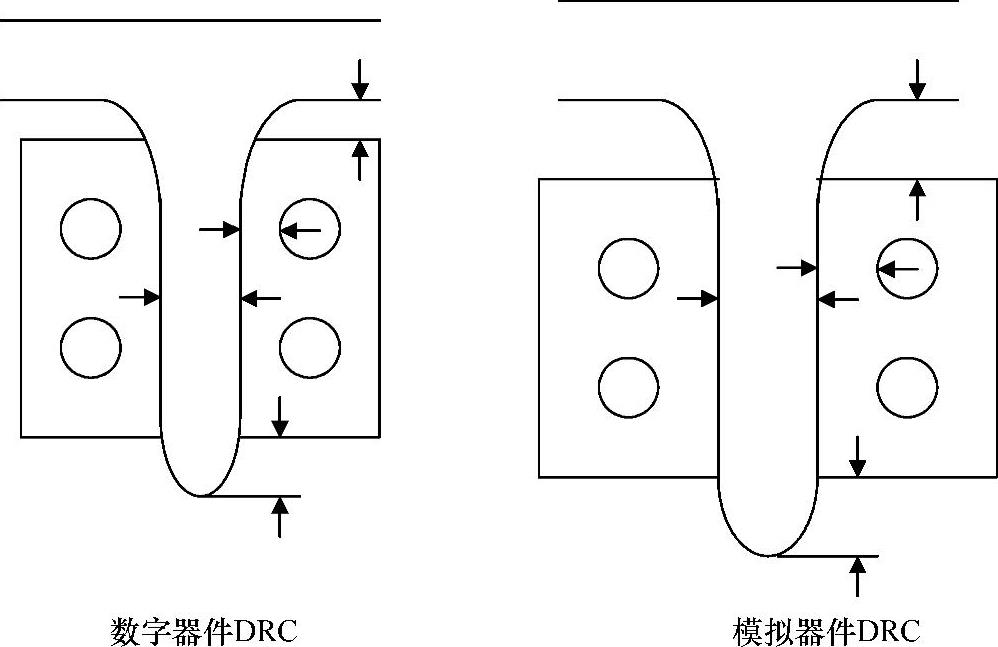

纳米CMOS工艺中以数字为中心的优化,给模拟电路设计带来很大的困难。为了确保能成功制造模拟电路,必须考虑相关的关键问题。必须尽早考虑的一个问题是,是否要针对模拟电路开发特殊的设计规则来检查,以保证在存在波动的情况下可实现模拟电路的重复生产。一些应该被考虑的规则实例如图10-12所示。该图总结了数字和模拟器件之间的版图差异。模拟器件很少有过于严格的设计规则,这会使器件芯片面积更大。这些过于严格的规则具有的优点是模拟器件比数字单元对工艺波动的敏感性更小。掩膜对准程度会严重影响模拟单元的性能。使套刻误差对模拟电路的影响最小化的技术将在第11章深入讨论。增加间距和覆盖要求可以减小有效栅长的分散性,这是由于多晶图形光刻后直角弧化能减少因为多晶掩膜未对准所产生的变化,如图10-12所示。相似地,增加接触孔与栅以及接触孔到扩散区的间距,在接触孔掩膜出现偏移时,也能减小电阻的分散性以及接触孔与栅之间电容的分散性。避免使用最小栅长也将减小模拟器件的分散性。选择栅长时必须多加小心,因为大多数的工艺都是按照数字电路的要求进行调整。为了达到数字电路的高密度,一般基于最小沟道长度确定节距。由此确定的节距,对模拟电路模块来说,很可能波动性较大。如果没有正确地应用OPC算法,也可以完成版图设计,但是却会产生成品率问题。强烈建议模拟电路设计人员与集成电路制造方或生产线协商,以确定作为长度函数的波动性,从而能避免使用节距和沟道长度落入“禁区”。为了更好控制poly-CD,在设计中添加亚分辨率辅助图形(SRAF或散射条),形成节距“禁区”。纳米CMOS技术光学方面的内容和这些效应的详细解释可参见第3章。为了更好地实现poly-CD控制以及使Vth的波动最小,使所有的模拟晶体管同向排列非常重要,详细内容见第11章。

图10-12 模拟精度规则(https://www.xing528.com)

有些模拟电路,特别是锁相环(PLL),使用大量的电容作为去耦电容和环形滤波器电容。这些密集的电容阵列增加了扩散区密度,使得浅槽隔离(STI)刻蚀后很难清理扩散区上的氮化层。因此必须将这些阵列分开,以保持扩散区密度低于制造方设定的工艺阈值之下。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。