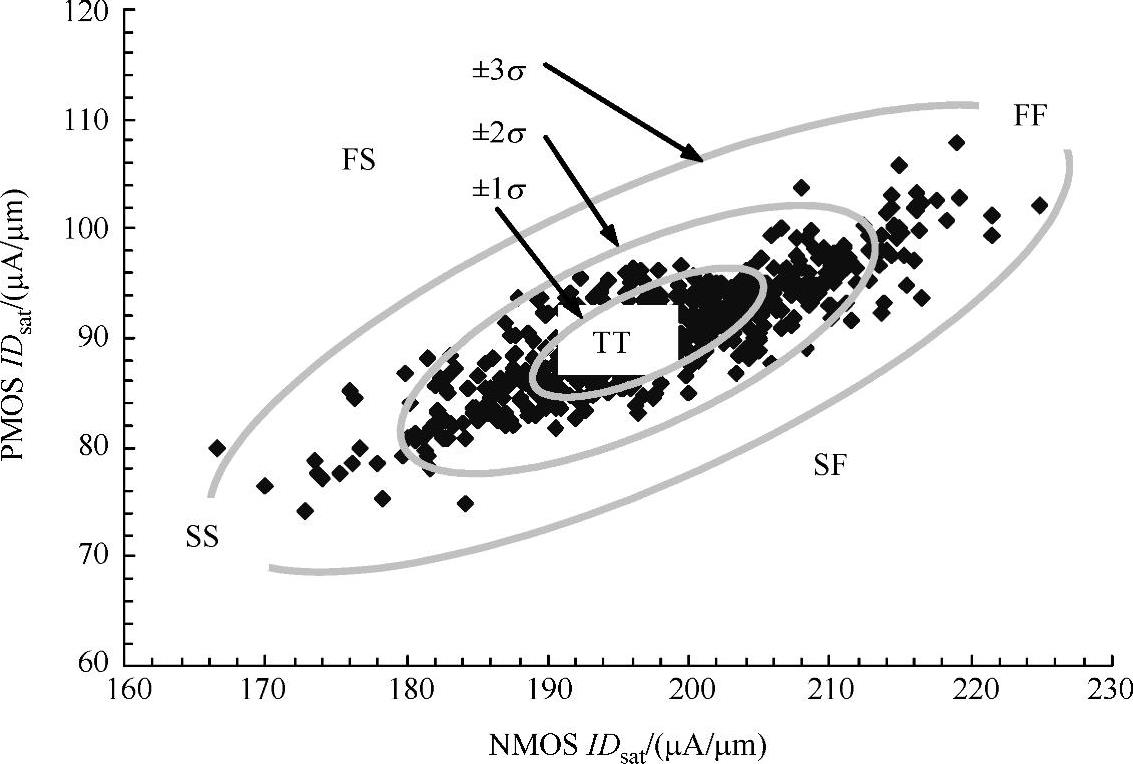

采用工艺角模型方法考虑的工艺组合与实际情况不相符合,会导致“过于保守的设计”,特别是当设计裕量变得更小时。这一点可以参见图11-33,图11-33所示为从多个晶园批得到的NMOS和PMOS的ID sat测量数据的散点图。其中,快——慢和慢——快(FS和SF)拐点很少出现。这从工艺的角度看是可以理解的,因为PMOS与NMOS器件仅局部相关。例如,如果我们考虑具有波动性的各种参数,像氧化层厚度、栅长度、栅宽度、沟道掺杂和halo注入等,它们中间一些参数(如氧化层厚度和沟道长度)的波动对PMOS和NMOS器件是相似的,而其他参数并不相关并且会独立的波动。另外,工艺的波动包括局部范围波动和全局范围波动两个成分,而工艺角并不能区分这两个分量,因此基于拐角模型不可能确定器件之间局部范围波动性的影响。

图11-33 PMOS和NMOS器件的工艺波动图

对模拟电路而言,很难确定最坏情况的拐角。快/慢的概念不一定适用。对运算放大器,高增益/低增益可能很有意义,但是很难确定哪个数字工艺拐角对应于放大器的高增益情况,因为它依赖于放大器的结构特点。当子模块被组合成像数据转换器那样更复杂的系统时,确定哪个工艺拐角代表最坏拐角变得更加困难。如果模拟电路仿真中,特别是已经给定了有限的模拟电路设计空间的情况下,采用数字工艺拐角将导致模拟电路的“过设计”。电路的过设计会导致复杂度增加、晶片尺寸更大、并且可能会失去市场窗口,因此如果有可能的话应该尽量避免。如果我们考虑工艺中几种可变参数的波动性,总的方差可以表示为(https://www.xing528.com)

如果必须满足这些极端情况下的性能要求,采用上式表示的总方差会导致电路严重“过设计”。

采用统计建模可以使设计者在制造前就能估计给定设计的功能成品率。这个信息对于在设计阶段而不是在制造后进行的参数权衡设计非常重要。设计者可以分析设计中的子模块以确定每个部分对整个系统成品率的贡献,从而使设计重点可以被放在设计最关键的部分。设计者也可以评估器件尺寸对功能性成品率的影响。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。