一、填空题 (每空0.5分,共20分)

1.两个与非门构成的基本RS 触发器的功能有___________、___________和__________。电路中不允许两个输入端同时为___________,否则将出现逻辑混乱。

2.通常把一个CP 脉冲引起触发器多次翻转的现象称为___________,有这种现象的触发器是_________________触发器,此类触发器的工作属于___________触发方式。

3.为有效地抑制“空翻”,人们研制出了___________触发方式的__________________触发器和_________________触发器。

4.JK 触发器具有___________、___________、___________和___________四种功能。欲使JK触发器实现Qn+1= 的功能,则输入端J应接___________,K应接___________。

的功能,则输入端J应接___________,K应接___________。

5.D触发器的输入端子有___________个,具有___________和___________的功能。

6.触发器的逻辑功能通常可用___________、__________、__________和___________等多种方法进行描述。

7.组合逻辑电路的基本单元是___________,时序逻辑电路的基本单元是___________。

8.JK触发器的次态方程为___________;D触发器的次态方程为___________。

9.触发器有两个互非的输出端Q 和 ,通常规定Q=1,

,通常规定Q=1, =0时为触发器的___________状态;Q=0,Q=1时为触发器的___________状态。

=0时为触发器的___________状态;Q=0,Q=1时为触发器的___________状态。

10.两个与非门组成的基本RS触发器,在正常工作时,不允许 =__________,其特征方程为__________________,约束条件为__________________。

=__________,其特征方程为__________________,约束条件为__________________。

11.钟控的RS触发器,在正常工作时,不允许输入端R=S=__________,其特征方程为__________________,约束条件为__________________。

12.把JK 触发器______________________就构成了T触发器,T触发器具有的逻辑功能是___________和___________。

13.让___________触发器恒输入 “1”就构成了T′触发器,这种触发器仅具有___________功能。

二、判断题 (每小题1分,共10分)

1.仅具有保持和翻转功能的触发器是RS触发器。( )

2.基本的RS触发器具有“空翻”现象。( )

3.钟控的RS触发器的约束条件是:R+S=0。( )

4.JK触发器的特征方程是:Qn+1=JQn+KQn。( )

5.D触发器的输出总是跟随其输入的变化而变化。( )

6.CP=0时,由于JK触发器的导引门被封锁而触发器状态不变。( )

7.主从型JK触发器的从触发器开启时刻在CP下降沿到来时。( )

8.触发器和逻辑门一样,输出取决于输入现态。( )

9.维持阻塞D触发器状态变化在CP下降沿到来时。( )

10.凡采用电位触发方式的触发器,都存在“空翻”现象。( )

三、选择题 (每小题2分,共20分)

1.仅具有置“0”和置“1”功能的触发器是( )。

A、基本RS触发器 B、钟控RS触发器

C、D触发器 D、JK触发器

4.仅具有保持和翻转功能的触发器是( )。(https://www.xing528.com)

A、JK触发器 B、T触发器 C、D触发器 D、T′触发器

5.触发器由门电路构成,但它不同于门电路功能,主要特点是( )

A、具有翻转功能 B、具有保持功能

C、具有记忆功能 D、具有禁止功能

7.按触发器触发方式的不同,双稳态触发器可分为( )

A、高电平触发和低电平触发 B、上升沿触发和下降沿触发

C、电平触发或边沿触发 D、输入触发或时钟触发

8.按逻辑功能的不同,双稳态触发器可分为( )。

A、RS、JK、D、T等 B、主从型和维持阻塞型

C、TTL型和MOS型 D、上述均包括

9.为避免“空翻”现象,应采用( )方式的触发器。

A、高电平触发 B、边沿触发 C、电位触发 D、低电平触发

10.为防止“空翻”,应采用( )结构的触发器。

A、TTL B、MOS C、主从或维持阻塞 D、CMOS

四、简答题 (每小题3分,共15分)

1.时序逻辑电路的基本单元是什么?组合逻辑电路的基本单元又是什么?

2.何谓“空翻”现象?抑制“空翻”可采取什么措施?

3.触发器有哪几种常见的电路结构形式?它们各有什么样的动作特点?

4.试分别写出钟控RS触发器、JK触发器和D触发器的特征方程。

5.你能否推出由两个或非门组成的基本RS触发器的功能?写出其真值表。

五、分析题 (共35分)

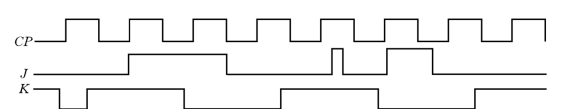

1.已知TTL主从型JK触发器的输入控制端J和K 及CP 脉冲波形如图6.18所示,试根据它们的波形画出相应输出端Q的波形。(8分)

图6.18 检测题6.5.1波形图

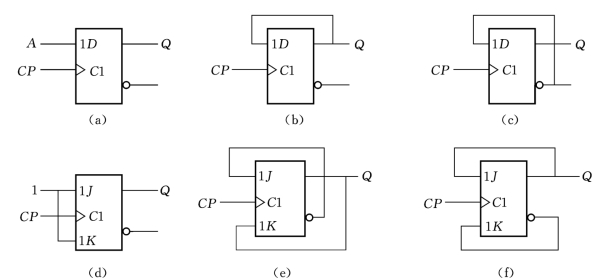

2.写出图6.19所示各逻辑电路的次态方程。(每图3分,共18分)

图6.19 检测题6.5.2逻辑图

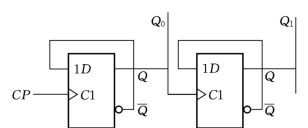

3.图6.20所示为维持阻塞D触发器构成的电路,试画出在CP脉冲下Q0和Q1的波形,设Q0、Q1初态为“0”。(9分)

图6.20 检测题6.5.3逻辑图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。