计数器在控制、分频、测量等电路中应用非常广泛,所以具有计数功能的集成电路型号也较多。常用的集成芯片有74LS161、74LS90、74LS197、74LS160、74LS92等。下面以74LS161、74LS90为例,介绍集成计数器电路的功能及正确使用方法。

1.集成芯片74LS90的引脚功能及正确使用

74LS90是一个14脚的集成电路芯片,其内部是一个二进制计数器和一个五进制计数器,下降沿触发。引脚排列及逻辑功能图如图7.10所示。

(1)引脚功能。

脚1——五进制计数器的时钟脉冲输入端。

图7.9 十进制加计数器状态图

图7.10 74LS90芯片的引脚排列图及逻辑功能示意图

(a)引脚排列图;(b)逻辑功能示意图

脚2和脚3——直接复位(清零)端。

脚4和脚13——空脚。

脚5——电源(+5V)。

脚6和脚7——直接置9端。

脚10——接地端。

脚9、脚8、脚11——五进制计数器的输出端。

脚12——二进制计数器的输出端。

脚14——二进制计数器的时钟脉冲输入端。

(2)计数电路的构成。

1)74LS90在使用时,若时钟脉冲端由管脚14即CPA输入,由管脚12QA输出时,即构成一个二进制计数器。

2)当74LS90的时钟脉冲端由管脚1CPB输入,由管脚9QB、8QC、11QD(由低位→高位排列)输出时,可构成一个五进制计数器。

3)74LS90还可构成十进制计数器。当计数脉冲由管脚14CPA输入,管脚12QA直接和管脚1CPB相连,输出端就构成8421BCD计数器。输出由高到低的排列顺序为11、8、9、12。当计数脉冲由管脚14CPB输入,管脚11QD和管脚14CPA直接相连,又可构成一个5421BCD计数器。输出由高到低的排列顺序为12、11、8、9。构成以上两种二—十进制计数器的连接方法如图7.11所示。

图7.11 74LS90构成十进制计数器的两种方法示意图

(a)8421BCD码二—十进制计数器;(b)5421BCD码二—十进制计数器

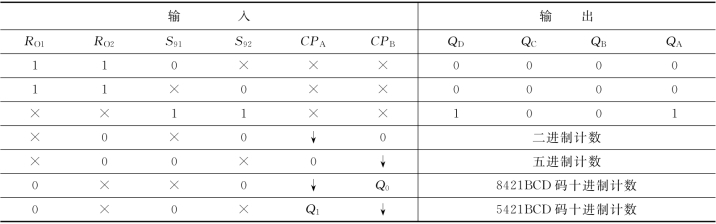

(3)74LS90的逻辑功能真值表见表7.6。

表7.6 74LS90集成芯片的功能真值表

由真值表可以看出,74LS90的两个复位端RO1和RO1同时为1时,计数器清零;两个置9端S91和S92在8421BCD码情况下同时为 “1”时,管脚11QD和管脚12QA输出为“1”,管脚8QC和管脚9QB输出为“0”,即电路直接置9。当计数器无论在计数情况下正常计数时,两个清零端和两个置9端中都必须至少有一个为低电平“0”。

2.集成芯片74LS161的引脚功能及正确使用

集成计数器74LS161是一个16脚的芯片,上升沿触发。具有异步清零、同步预置数、进位输出等功能,引脚排列如图7.12所示。

图7.12 74LS161引脚排列图

(1)引脚功能。

脚1——直接清零端 。

。

脚2——时钟脉冲输入端CP。

脚3、脚4、脚5、脚6——预置数据信号输入端A、B、C、D。

脚7、脚10——输入使能端P和T。

脚8—— “地”端GND。

脚9——同步预置数控制端 。

。

脚11、脚12、脚13、脚14——数据输出端QD、QC、QB、QA,由高位→低位。

脚15——进位输出端CO。

脚16——电源端+UCC。

(2)功能真值表见表7.7。

表7.7 74LS161功能真值表

由功能真值表可看出,74LS161集成芯片的控制输入端与电路功能之间的关系为:

(3)构成任意进制的计数器。用集成74LS161芯片可构成任意进制的计数器。图7.13所示为构成任意进制时的两种连接方法。

图7.13 用74LS161构成任意进制的计数器

(a)反馈清零法连接图;(b)反馈预置法连接图

1)反馈清零法。

图7.12 (a)所示是反馈清零法构成十进制计数器的电路连接图。所谓反馈清零法,就是利用芯片的复位端和门电路,跳越M-N 个状态,从而获得N 进制计数器的。从图7.12 (a)可看出,当计数至1001时,通过与非门引出一个 “0”信号直接进入清零端 ,使计数器归零。

,使计数器归零。

2)反馈预置数法。用反馈预置法构成其他进制计数器时,要根据预置数和计数器的进制大小来选择反馈信号。要构成N 进制计数器,则应将 (预置数+N-1)所对应二进制代码中的“1”取出送入与非门的输入端,与非门的输出接74LS161的 端,而预置数接至DCBA 端。图7.12 (b)是用反馈预置法构成的十进制计数器。其中预置数为0000,反馈信号为1001。利用反馈预置数法构成的同步预置数计数器不存在无效态。

端,而预置数接至DCBA 端。图7.12 (b)是用反馈预置法构成的十进制计数器。其中预置数为0000,反馈信号为1001。利用反馈预置数法构成的同步预置数计数器不存在无效态。

3.集成芯片的扩展使用(https://www.xing528.com)

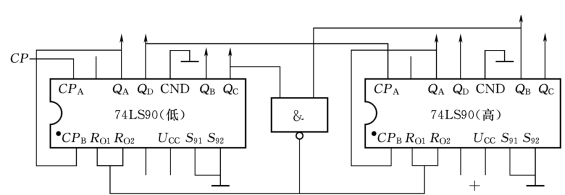

如果需要构成多位十进制计数器电路时,就要将两个 (或多个)集成计数器芯片级联。例如,将两个74LS90芯片级联后扩展使用构成24进制计数器的方法如图7.13所示。图7.14中,将高位芯片的时钟脉冲输入端CPA接至低位芯片的最高位信号输出端QD,低位芯片的CPA端作为电路时钟脉冲的输入端,两芯片的QA端子均直接和各自的CPB相连,使其形成三位二进制输出的十进制数进位关系;把两个芯片中的置9端直接与“地”相连,让低位片的输出QC和高位片的QB分别连接在与非门的输入端子上,而两芯片的清零端并在一起连接在与非门的输出端上,当高位片QB和低位片QC均为高电平“1”时,对应二进制数 “24”,使与非门全1出0,驱使清零端工作,电路归零。显然,这是利用反馈清零法达到24进制计数器的实例。

图7.14 74LS90构成8421BCD码24进制计数器

集成74LS161芯片的功能扩展实例如图7.15所示。当两个74LS161芯片构成8位同步二进制计数器时,可将低位片的两个使能端P和T 连在一起恒接“1”,CO端直接与高位片的使能端P相连;高位片的使能端T恒接高电平“1”;两个芯片的清零端和预置数端分别连在一起接高电平“1”,两端子CP连一起与时钟输入信号相连,从而构成同步二进制计数器。

图7.15 74LS161构成的同步8位二进制计数器

如果用反馈清零法或反馈预置数法将74LS161芯片构成任意进制的计数器时,其方法和74LS90所采用的方法相同,在此不再赘述。

本节重要知识点学习检测

1.何谓计数器的“自启动”能力?

2.试用74LS90集成计数器构成一个十二进制计数器,要求用反馈预置数法实现。

3.试用74LS161集成计数器构成一个六十进制计数器,要求用反馈清零法实现。

本节技能训练

实验七 计数器及其应用

一、实验目的

1.熟悉和掌握用集成触发器构成计数器的方法。

2.了解和初步掌握中规模集成计数器的使用方法及功能测试。

3.掌握用中规模集成计数器构成任意进制计数器的方法。

二、实验主要仪器设备

1.+5V直流电源。

2.单次时钟脉冲源和连续时钟脉冲源。

3.逻辑电平开关和逻辑电平显示器。

4.译码显示电路。

5.74LS74 (或CC4013)双D集成触发器芯片2只,74LS192 (或CC40192)集成计数器芯片3只,74LS00 (或CC4011)四2输入与非门集成电路1只,74LS20 (或CC4012)双四输入与非门1只。

6.相关实验设备及连接导线若干。

三、实验原理及相关知识要点

1.计数器是用以实现计数功能的时序逻辑部件,计数器不仅可用来脉冲计数,还可用作数字系统的定时、分频和执行数字运算以及其他特定的逻辑功能。

2.计数器的种类很多,按材料可分有TTL型和CMOS型;按工作方式可分为同步计数器和异步计数器;根据计数制的不同又可分为二进制计数器、十进制计数器和N 进制计数器;根据计数的增减趋势还可分为加计数器和减计数器等。

目前,无论是TTL集成计数器或CMOS集成计数器,品种都比较齐全。使用者只要借助于电子手册提供的功能表和工作波形图以及管脚排列图,即可正确地运用这些中规模集成计数器器件。

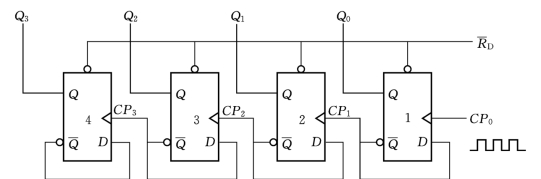

3.用四位D触发器构成的异步二进制加/减计数器如图7.16所示。

图7.16 用四位D触发器构成的异步二进制加/减计数器

图7.15由四位D触发器构成的异步二进制加计数器。

图7.16的连接特点是:把4只D触发器都接成T′触发器,使每只触发器的D输入端均与输出的 端相连,接于相邻高位触发器的CP端作为其时钟脉冲输入。

端相连,接于相邻高位触发器的CP端作为其时钟脉冲输入。

若把图7.15稍加改动,就可得到四位D触发器构成的二进制减法计数器。改动中只需把高位的CP端从与低位触发器 端相连改为与低位触发器的Q 端相连即可。

端相连改为与低位触发器的Q 端相连即可。

4.中规模的十进制计数器功能测试。

74LS192 (或CC40192)是16脚的同步集成计数器电路芯片,具有双时钟输入、清除和置数等功能,其管脚排列图及逻辑图符号如图7.17所示。

图7.17 74LS192管脚排列图及逻辑图符号

(a)管脚排列图;(b)逻辑图符号

CC40192与74LS192功能及管脚排列相同,二者可互换使用。测试方法按照表7.8进行,把测试结果与表7.8相对照。

表7.8 74LS192测试方法

图7.18 由CC40192构成的6进制计数器

5.实现任意进制的计数器

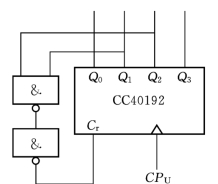

(1)用反馈清零法获得任意进制的计数器。若要获得某一个N 进制计数器,可采用M 进制计数器 (必须满足M>N)利用反馈清零法实现。例如,用一片CC40192获得一个6进制计数器,可按图7.18连接。

原理:当计数器计数至四位二进制数0110时,其两个为 “1”的端子连接于与非门,全1出0功能,再经过一个与非门有0出1,直接进入清零端Cr,计数器清零,重新从0开始循环,实现了6进制计数。

(2)用反馈预置法获得任意进制的计数器。由三个CC40192可获得421进制计数器,其连接如图7.19所示。

图7.19 由三个CC40192构成的421进制计数器

原理:只要高位片出现0100、次高位片出现0010、低位片出现0001时,三个 “1”被送入与非门全1出0,这个“0”被送入由两个与非门构成的RS触发器的置 “1”端,使Q端输出的“0”送入三个芯片的置数端LD,由于三个芯片的数据端均与 “地”相连,因此各计数器输出被 “反馈置零”。计数器重新从000000000000计数,直到再来一个010000100001回零重新循环计数。

(3)用两片CC40192集成电路构成一个特殊的12进制计数器。在数字钟里,时针的计数是以1~12进行循环计数的。显然这个计数中没有“0”,那么我们就无法用一片集成电路实现,用两片CC40192构成12进制计数器的电路图如图7.20所示。

图7.20 由两片CC40192构成的12进制计数器

原理:芯片1为低位片,芯片2为高位片,两个芯片级联,即让芯片1的进位输出端 作为高位芯片的时钟脉冲输入,接于高位片的加计数时钟脉冲端CPU上。低位片的预置数为0001,因此计数初始数为“1”,当低位片输出为8421BCD码的有效码最高数1001后,再来一个时钟脉冲就产生一个进位脉冲,这个进位脉冲进入高位片使其输出从0000翻转为0001,低位片继续计数,当又计数至0011时,与高位片的0001同时送入与非门,使与非门输出全1出0,这个 “0”进入两个芯片的置数端

作为高位芯片的时钟脉冲输入,接于高位片的加计数时钟脉冲端CPU上。低位片的预置数为0001,因此计数初始数为“1”,当低位片输出为8421BCD码的有效码最高数1001后,再来一个时钟脉冲就产生一个进位脉冲,这个进位脉冲进入高位片使其输出从0000翻转为0001,低位片继续计数,当又计数至0011时,与高位片的0001同时送入与非门,使与非门输出全1出0,这个 “0”进入两个芯片的置数端 ,于是计数器重新从0000 0001开始循环……

,于是计数器重新从0000 0001开始循环……

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。