乘法器/加法器(MAC)单元包括一个乘法器和一个专用加法器。乘法器/加法器单元具有强大的乘/累加运算功能,可以在一个流水线周期内完成1次乘法运算和1次加法运算。在数字信号处理的典型算法诸如数字滤波(FIR和IIR滤波)、卷积、FFT以及自相关等运算中,使用乘/累加运算指令可以大大提高系统的运算速度。

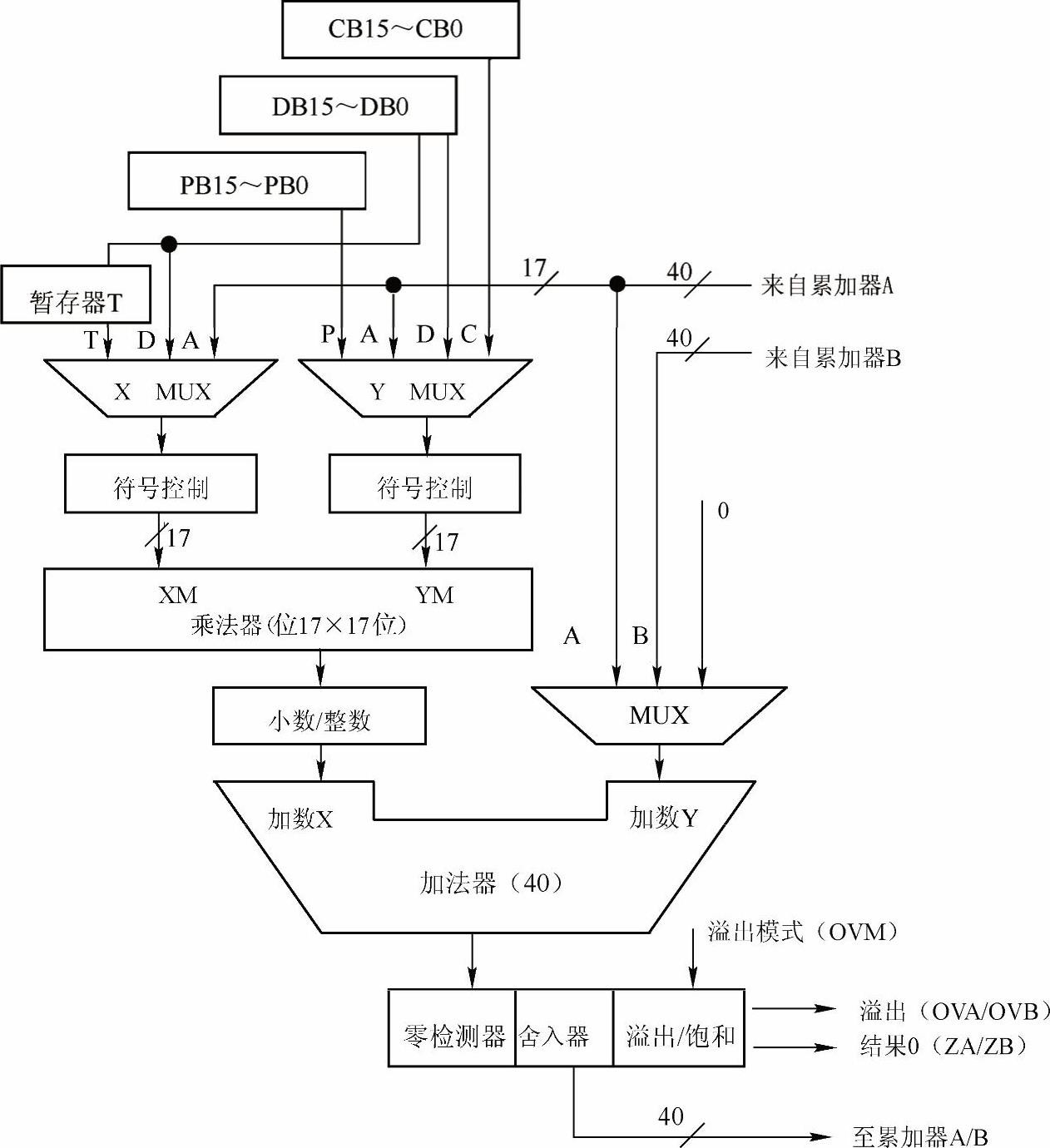

TMS320C54x CPU中的MAC单元有一个17位×17位的硬件乘法器,并且附带了一个40位的专用加法器,其功能框图如图3-6所示。其中硬件乘法器用来完成乘法运算,专用加法器用来完成累加、取整、饱和等操作。

图3-6 乘法器/加法器单元功能框图

1.乘法器

(1)乘法器的输入

乘法器有两个输入端,分别为XM和YM。

从XM端输入乘法器的数据来源有以下几种情况:

1)来自数据总线DB的数据存储器操作数。

2)来自暂存器T的操作数。

3)来自累加器A的第32~16位操作数。

从YM端输入乘法器的数据来源有以下几种情况:

1)来自数据总线DB的数据存储器操作数。

2)来自数据总线CB的数据存储器操作数。

3)来自程序总线PB的程序存储器操作数。

4)来自累加器A的第32~16位操作数。

(2)乘法器的输出

乘法器的输出经小数控制电路接至加法器的XA输入端。

(3)乘法器的操作(https://www.xing528.com)

MAC单元的乘法器能进行有符号数、无符号数以及有符号数与无符号数的乘法运算。根据操作数的不同情况需作以下3种处理:

1)如果是两个有符号数相乘,则在进行乘法运算之前,先对两个16位操作数进行符号位扩展,在最高位前添加1个符号位,其值由乘数的最高位决定(正数为0,负数为1),扩展为17位有符号数后再相乘。

2)如果是两个无符号数相乘,则在两个16位操作数的最高位前面添加“0”,扩展为17位操作数后再相乘。

3)如果是有符号数与无符号数相乘,则有符号数在最高位前添加1个符号位,其值由最高位决定,而无符号数在最高位前面添加“0”,然后两个操作数相乘。

由于乘法器在进行两个16位二进制补码相乘时会产生两个符号位,为提高运算精度,在状态寄存器ST1中设置小数方式控制位FRCT。当FRCT=1时,乘法器结果自动左移一位,消去多余的符号位,相应的定标值加1。

2.专用加法器

在MAC单元中,专用加法器用来完成乘积项的累加运算。专用加法器包括加法器、零检测器、舍入器(二进制补码)及溢出/饱和逻辑电路。

(1)加法器的输入

加法器有两个输入端,分别为XA和YA。其中XA端输入为来自乘法器的输出,YA端输入为来自累加器A或B的操作数。

(2)加法器的输出

加法器输出经零检测器、舍入器和溢出/饱和逻辑电路后,将产生的状态标志送入状态寄存器,并将运算结果送入累加器A或B。

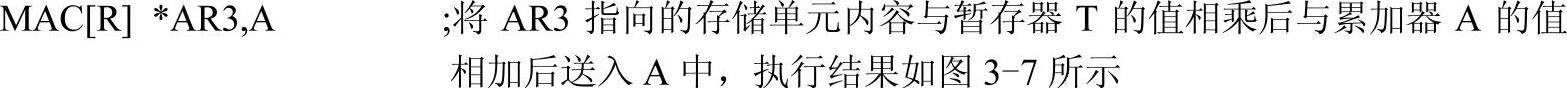

1)舍入处理。有些乘法指令,如MAC、MAS等指令,如果带扩展名R,就对结果进行四舍五入处理,即将215(8000h)加至结果,并将目的累加器的低16位清0。当执行LMS指令时,为了修正系数的量化误差,也要进行舍入处理。参见例3-4。

2)溢出/饱和处理。当OVM=1,并且FRCT=1时,PMST寄存器中的乘法饱和方式位SMUL决定是否在累加(MAC和MAS操作)前对乘法的结果进行饱和处理。

当乘法饱和方式位SMUL1=1时,执行后续的加(MAC)或减(MAS)前,在小数模式下,8000h×8000h被饱和处理为7FFFFFFFh。当乘法饱和方式位SMUL1=0时,仅仅MAC和MAS的最终结果被饱和处理,而乘法得到的结果不会被饱和处理。

【例3-4】 MAC指令和MAC[R]指令的执行情况分析。

图3-7 指令MAC[R]*AR3,A的执行情况

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。