时钟发生器用来为TMS320C54x提供时钟信号,它由内部振荡器和锁相环(PLL)电路组成。时钟发生器工作时需要一个参考时钟输入,它可以由以下两种方式提供:

1)内部晶体振荡器。将一个晶体跨接在TMS320C54x的X1和X2/CLKIN引脚两端,同时CLKMD引脚必须设置启动内部振荡器模式。

2)外部参考时钟源。直接将外部时钟接入X2/CLKIN引脚,X1引脚悬空。

TMS320C54x内部的锁相环(PLL)电路具有频率放大和信号提纯的功能。利用PLL可以锁定时钟发生器的振荡频率,为系统提供高稳定的时钟信号,对外部时钟可以进行倍频,使外部时钟的周期低于CPU机器周期,以降低因高速开关时钟引起的高频噪声。

目前,TMS320C54x有两种不同类型的PLL,即硬件配置的PLL和软件可编程PLL,下面分别讨论。

1.硬件配置的PLL

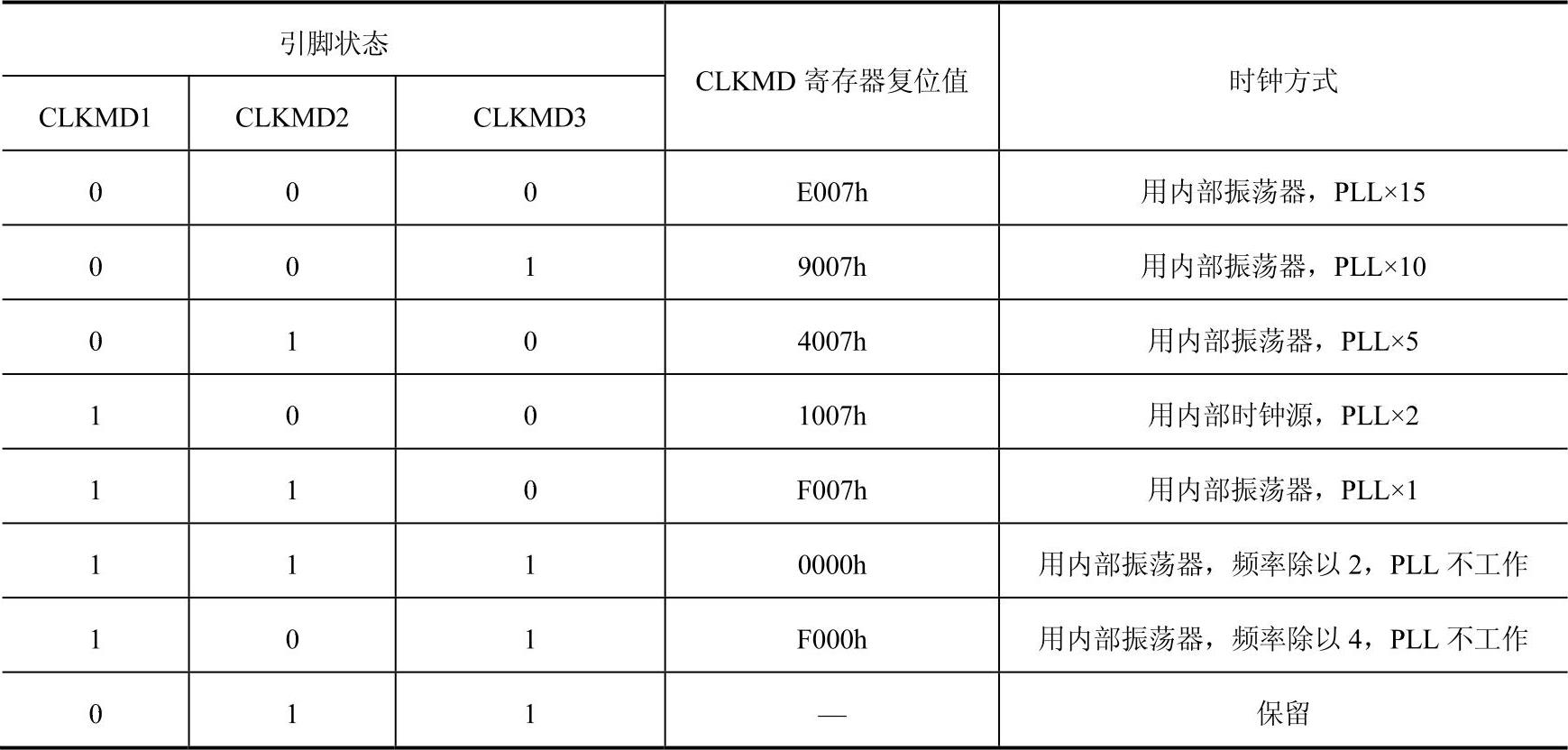

所谓硬件配置的PLL,就是通过设定TMS320C54x的3个时钟模式引脚CLKMD1、CLKMD2、CLKMD3的状态,选定时钟方式,即选择片内振动时钟与外部参考时钟的倍频。具体的配置方式见表3-15。

表3-15 时钟方式的配置

①时钟方式选择方案1或选择方案2依器件的不同而定。

②停止方式表示PLL被禁止,系统时钟不提供给CPU外设,其功能等效于IDLE3省电方式,但用该种方式要使时钟正常工作需要改变硬件连接。因此,要省电还是推荐使用IDLE3指令,因为用IDLE3可以使PLL停止工作,当复位或外部中断到来时可以恢复工作。

由表3-15可知,不用PLL时,CPU的时钟频率等于内部晶体振荡频率或外部时钟频率的一半;若用PLL,CPU的时钟频率等于晶体振荡器频率或外部时钟频率乘以系数N(PLL×N)。

2.软件可编程PLL

软件可编程PLL是一种高度灵活的时钟控制方式。它的时钟定标器提供各种时钟乘法器系数,并能直接接通和关断PLL。PLL的锁定定时器可以用于延迟转换PLL的时钟方式,直到锁定为止。

通过软件编程,可以选用以下两种时钟方式中的一种,即

1)PLL方式:即倍频方式,输入时钟CLKIN乘以31个可能的因子中的一个因子,这些因子的取值范围是0.25~15,它们可以通过PLL电路获得。

2)DIV方式:即分频方式,输入时钟CLKIN除以2或4。当使用分频模式时,所有的模拟电路,包括PLL电路都关断,以使功耗降到最小。

DSP复位后,时钟方式则由3个外部引脚(CLKMD1、CLKMD2和CLKMD3)的状态所决定。表3-16列出了TMS320VC5402复位时CLKMD1/2/3引脚和时钟方式寄存器(CLKMD,地址为58h)及时钟的关系。时钟方式决定DSP工作时钟与CLKIN输入时钟频率的比值。

表3-16 TMS320VC5402复位时设置的时钟方式

(https://www.xing528.com)

(https://www.xing528.com)

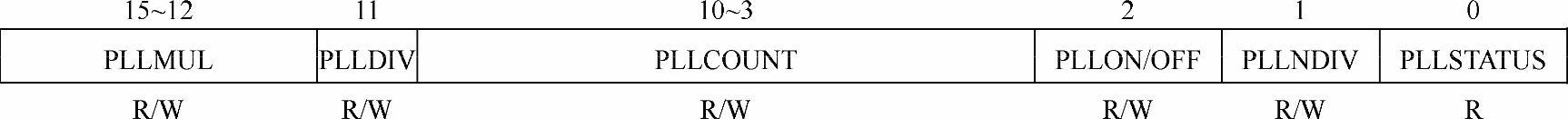

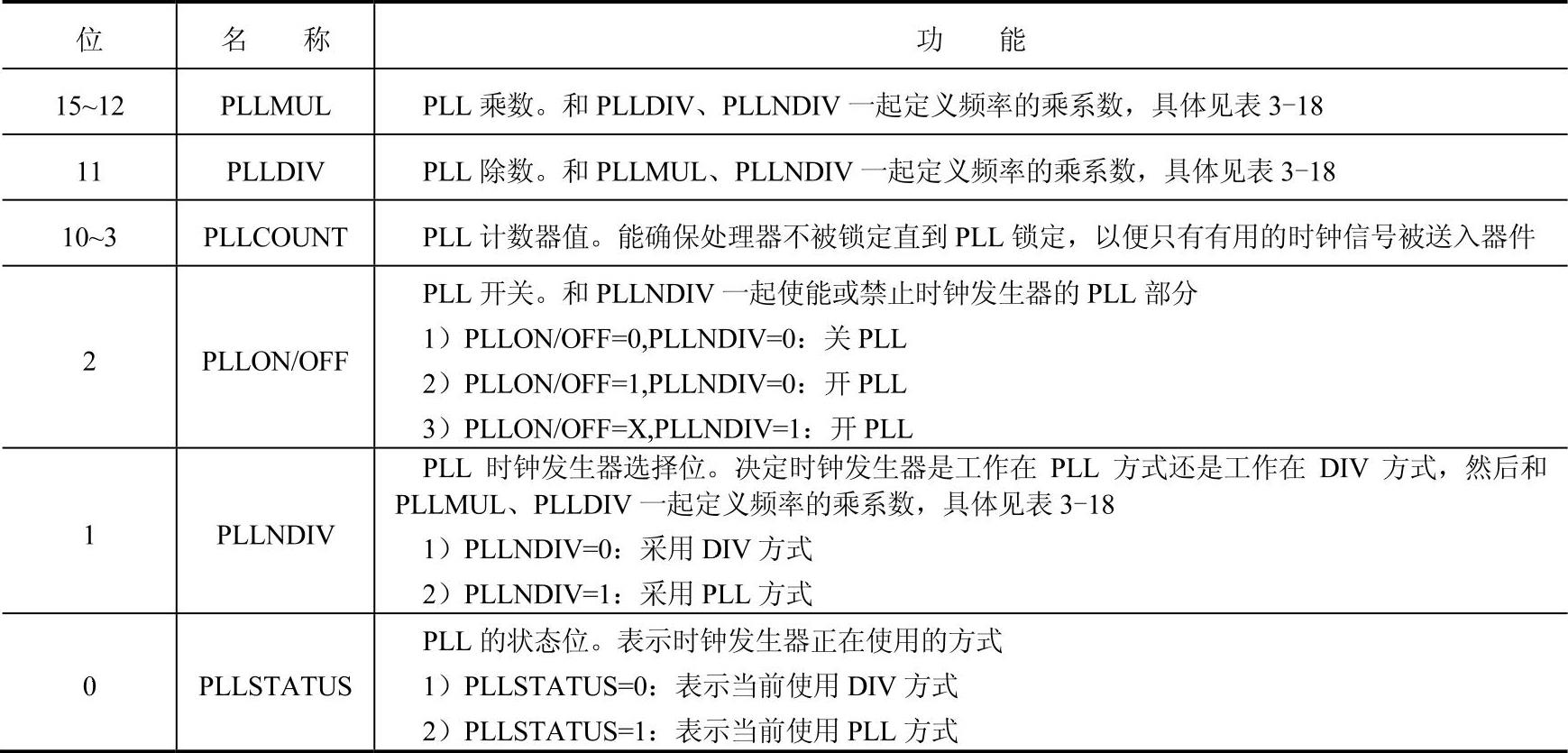

复位后,可以对CLKMD重新编程加载,以配置成所要求的时钟方式。CLKMD寄存器是用来定义PLL时钟模块中的时钟配置,其各位的定义如图3-21所示,各位的功能描述见表3-17,由CLKMD的PLLDIV和PLLMUL位所确定的PLL的乘系数见表3-18。

图3-21 时钟方式寄存器CLKMD各位的定义

表3-17 时钟方式寄存器CLKMD各位的功能

表3-18 PLL的乘系数

①CLKOUT=CLKIN×乘系数。

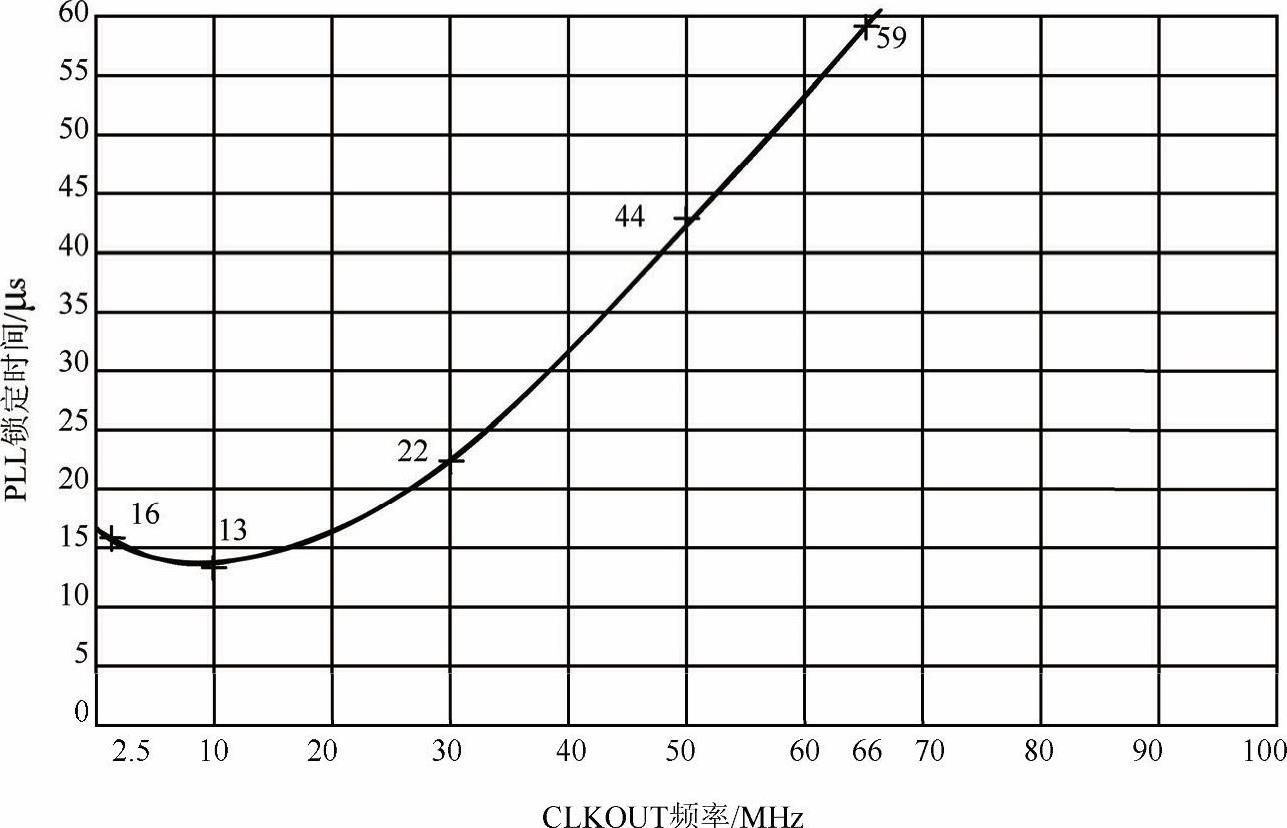

在PLL锁定之前,它是不能用做TMS320C54x时钟的。为此,通过对CLKMD寄存器中的PLLCOUNT位编程,就可以很方便地自动延迟定时,直到PLL锁定为止。这主要靠PLL中的锁定定时器,PLLCOUNT的数值(0~255)加载给它后,每来16个输入时钟(CLKIN),它就减1,一直减到0为止。因此,锁定延时时间的设定范围为0~255×16×CLKIN个周期的时间长度。

PLL锁定时间与CLKOUT频率之间的关系如图3-22所示。

图3-22 PLL锁定时间与CLKOUT频率之间的关系

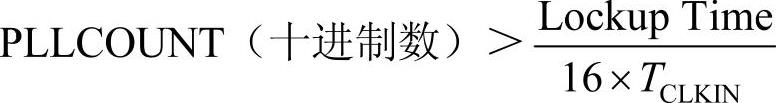

有了锁定时间Lockup Time,即可求得PLLCOUNT的数值:

式中,TCLKIN是输入时钟周期;Lockup Time是PLL的锁定时间。

当时钟发生器从DIV工作方式转移到PLL工作方式时,锁定定时器工作。在锁定期间,时钟发生器继续工作在DIV方式。PLL锁定定时器减到0后,PLL才开始对TMS320C54x定时,且CLKMD寄存器的PLLSTATUS位置1,表示定时器已工作在PLL方式。

如果要从DIV方式转到PLL×3方式,已知CLKIN的频率为13MHz,可以求得PLLCOUNT=41(十进制数),只要在程序中加入如下指令即可:

其中,PLLMUL=0010,PLLDIV=0,PLLNDIV=1,故乘系数为3;PLLON/OFF=1,PLL工作;PLLCOUNT=00101001,十进制计数值为41。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。