在一些外设扩展中,通用I/O(GPIO)使用非常方便。GPIO,即指能为外围设备提供信号输出和从外围设备输入信号到DSP的引脚,这些引脚能通过软件提供多用途的输入和输出信号。在TMS320C54x系列DSP中,通常有两类引脚可以用做GPIO,可以是TMS320C54x的XF和 ,或将HPI-8的硬件数据接口引脚配置为GPIO端口。

,或将HPI-8的硬件数据接口引脚配置为GPIO端口。

1.使用TMS320C54x通用I/O口XF和 TMS320C54x系列DSP提供的两个可编程控制通用I/O引脚XF和

TMS320C54x系列DSP提供的两个可编程控制通用I/O引脚XF和 ,可用做普通I/O口。

,可用做普通I/O口。

2.HPI-8配置为GPIO

TMS320VC54x系列提供了一个主机接口(HPI)。当HPI-8功能被禁止时(在启动复位时让HPIENA脚为0),其8位双向数据总线HD0~HD7引脚可以配置为GPIO。

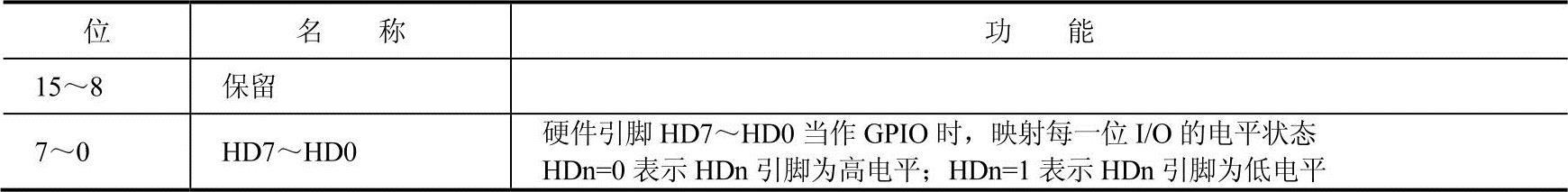

有两个存储器映射寄存器来控制HPI-8口的GPIO功能,它们是:通用I/O控制寄存器(GPIOCR)和通用I/O状态寄存器(GPIOSR)。GPIOCR和GPIOSR寄存器的各位功能说明见表8-23和表8-24。

表8-23 GPIOCR位结构定义(https://www.xing528.com)

表8-24 GPIOSR位结构定义

GPIOCR寄存器的TOUT1位是Timer1的输出使能位。当HPI-8功能被禁止后,TOUT1位允许或禁止Timer1从HINT脚输出。当系统只有一个定时器时,该位被保留。HDIR7~HDIR0控制8个I/O口的方向。当HDIR7~HDIR0的某位置为1时,GPIOSR的相应位的值输出到该引脚;同理,当某位为0时,相应引脚的逻辑电平被读入到GPIOSR的相应位。注意,当某个HD引脚用做输入功能时,对GPIOSR相应位的写操作将不起作用。GPIOSR中HD7~HD0的某位为0,表示在相应的HD引脚输出低电平,或者相应的HD引脚读入的外部信号为低。HD7~HD0的某位为1时,表示在相应的HD引脚输出高电平,或者相应的HD引脚读入的外部信号为高。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。