1.D锁存器和D触发器的相同之处

D锁存器和D触发器都具有相同的功能表、逻辑表达式、状态转换图,它们的符号和波形时序图有所不同。

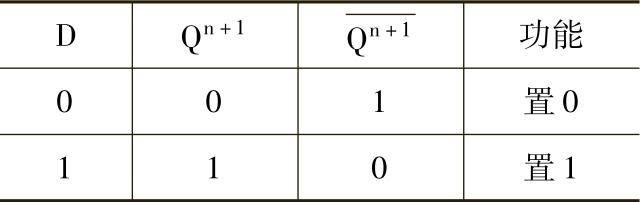

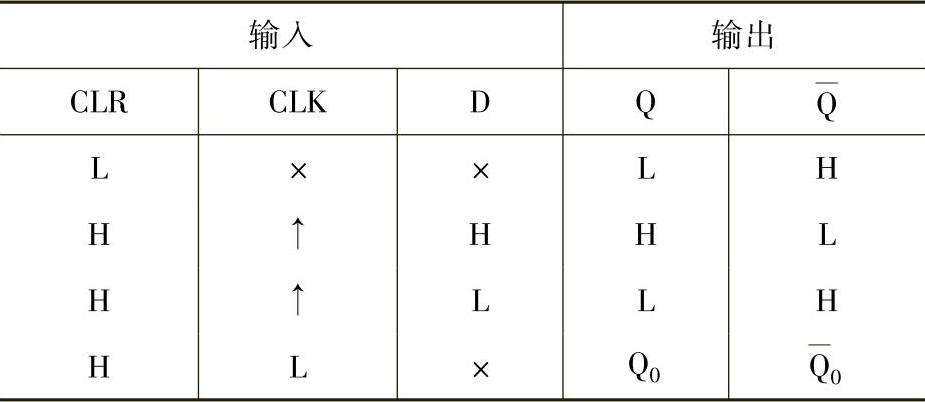

D锁存器和触发器都只有一个数据输入端,其功能表见表5-17。

需要特别指出的是,虽然功能表中没有提到记忆功能,但是,由于D锁存器和触发器都具有门控输入端或时钟脉冲输入端,在门控信号或时钟信号无效时,它们处于记忆状态,具有记忆功能;当门控信号或时钟信号有效时,它们执行表5-17中的置0、置1功能。

表5-17 D锁存器功能表

D锁存器和触发器的逻辑表达式为

Qn+1=D

逻辑表达式也是指门控信号或时钟信号有效时输出Q的新状态,若门控信号或时钟信号无效,则Qn+1=Qn。

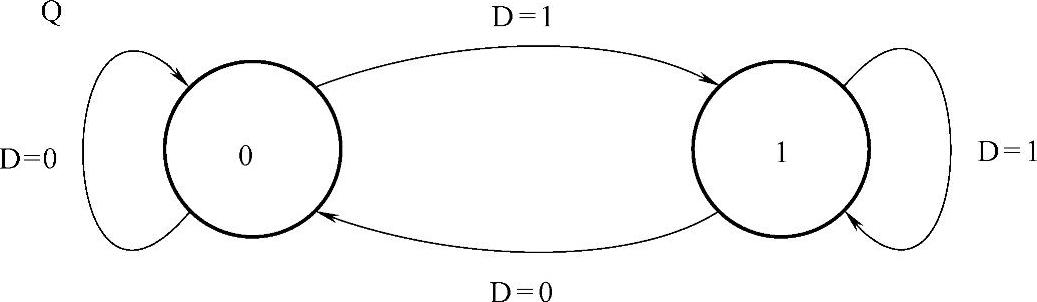

D锁存器和D触发器的状态转换图如图5-26所示。

图5-26 D锁存器和D触发器的状态转换图

2.D锁存器和D触发器的不同之处

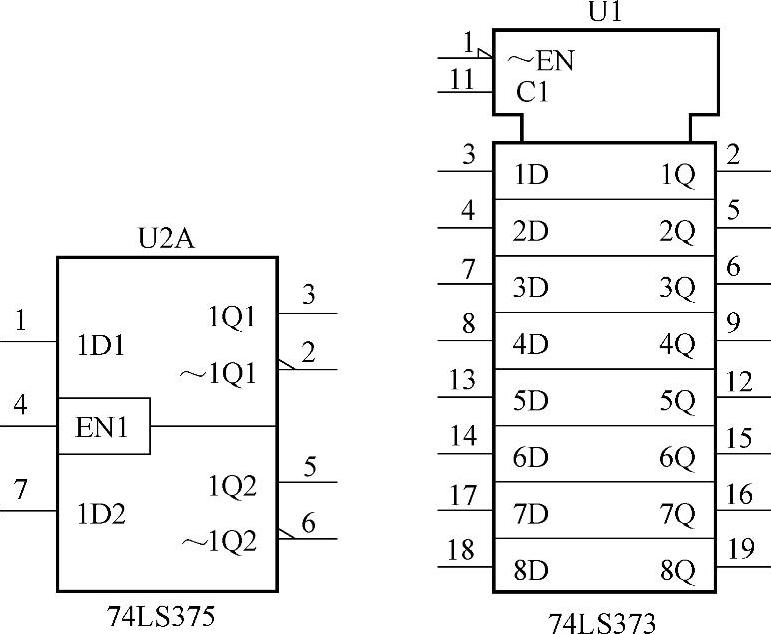

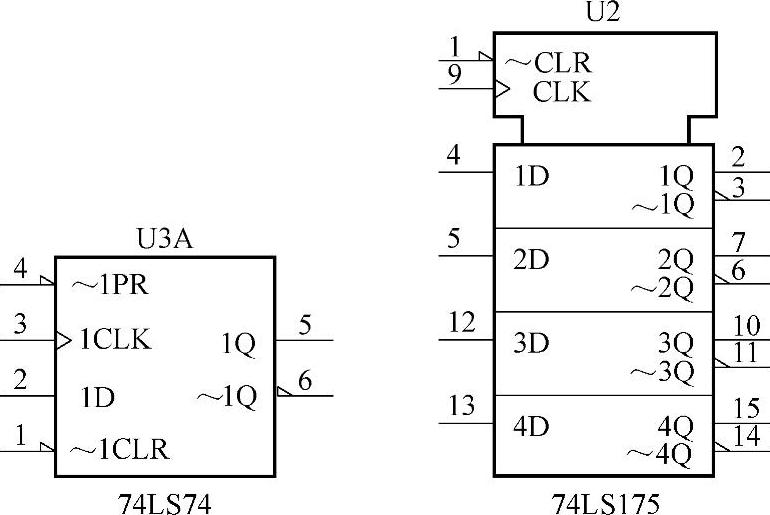

(1)逻辑符号的区别 两者的逻辑符号有所区别,其目的是通过符号的区别表现时序的不同。锁存器74LS375和74LS373的逻辑符号如图5-27所示。D触发器74LS74和74LS175的逻辑符号如图5-28所示。

图5-27 D锁存器的逻辑符号

图5-28 D触发器的逻辑符号

图5-27中,74LS375的门控信号为EN1(4号引脚),74LS373的门控信号为C1(11号管脚),可以看到,门控信号在方框内部是没有尖角的。(https://www.xing528.com)

图5-28中,74LS74的1CLK为时钟信号,74LS175的CLK为时钟信号,时钟信号在方框内部有尖角。输入端在方框内部有尖角表示该输入信号的边沿有效(上升沿或者下降沿),否则,表示输入信号的电平有效(高电平或者低电平)。由于脉冲信号边沿时间很短(上升时间或下降时间),故很少有干扰会恰巧落在这段时间中,不易产生错误,所以表现为抗干扰能力强。电平持续时间较长,对于占空比为50%的矩形波来说,高电平和低电平几乎各占半个周期,在其有效的这一段时间里,干扰很容易造成逻辑错误。也就是说,由于门控电平信号有效时间远长于时钟边沿信号,所以触发器的抗干扰能力比锁存器强很多。

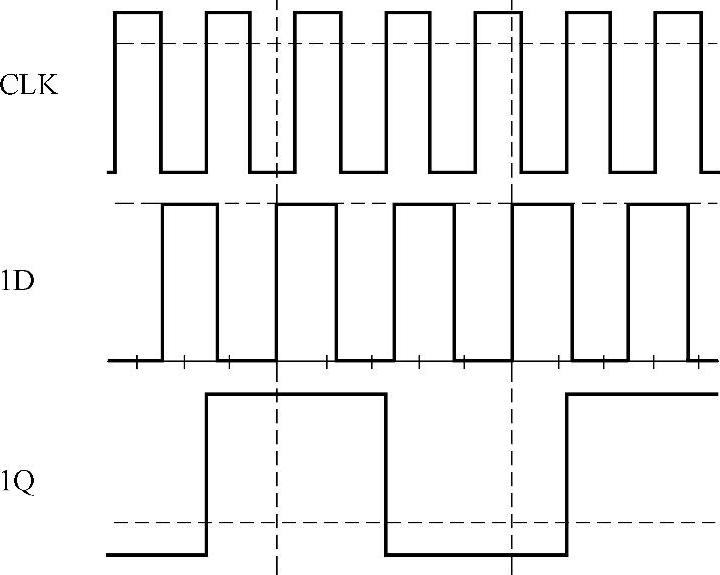

(2)时序图的区别 图5-29为D锁存器时序图,ENG为门控信号,当门控信号ENG为高电平时,输出1Q随时会根据输入1D发生变化,造成1Q的输出高电平有宽有窄,而且并不都是门控信号的整数倍,有时会窄到被别的电路误判为干扰脉冲的程度。因此,使用锁存器时,一般要求门控信号有效期间输入D不发生变化。

图5-30为D触发器时序图,在时钟脉冲CLK上升沿时,输出1Q随输入1D发生改变,而其他时间输出都不随输入发生改变,能够消除输入信号的毛刺。因此,触发器抗干扰能力比锁存器强。

图5-29 D锁存器时序图

3.触发器的控制端

常见D触发器除了74LS74和74LS175外,还有74LS174和74LS377等很多型号。通常触发器除了时钟信号(CLK或者C)输入端、数据输入端和输出端外,还会有一些控制端(即使能端)。有清除端的四D触发器74LS175的功能表见表5-18。

表5-18 74LS175的功能表

图5-30 D触发器时序图

清除端有时也称为清零端或复位端,该端输入信号有效时,触发器输出被置0。通过表5-18可知,74LS175的清除端CLR低电平有效,而且优先级别高于CLK(时钟信号),这种清除端也称为异步清除端,所谓“异步”是指不受时钟信号控制。表中最后一行表示了在清除端和时钟信号均无效的情况下,触发器执行记忆功能。

74LS175的逻辑符号如图5-28所示,在图中可以看到,清除端“~CLR”表示 ,方框外侧有半三角的箭头,表示该端子输入低电平有效。

,方框外侧有半三角的箭头,表示该端子输入低电平有效。

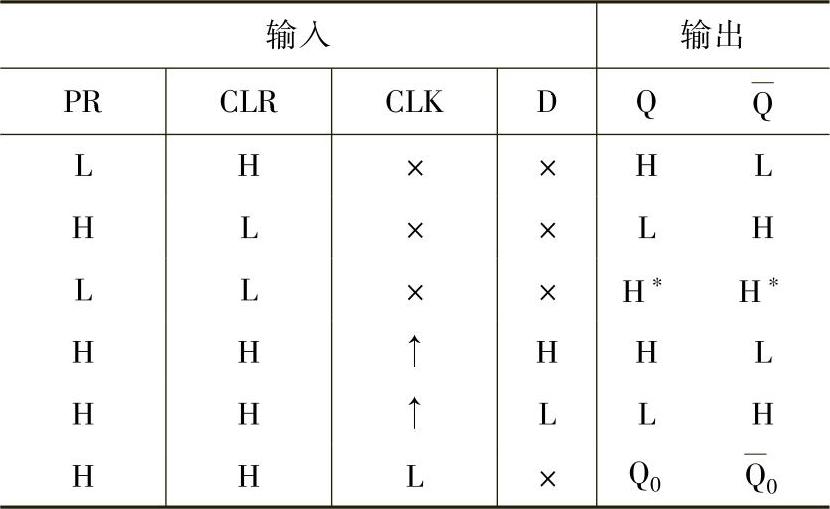

双上升沿D触发器74LS74的功能表见表5-19,逻辑符号如图5-28所示。

在表5-19中可以看到PR为低电平有效,在其有效期间,输出Q为1,其优先级别比时钟信号CLK高,是异步控制信号;CLR也是低电平有效,有效时输出Q为0,也是异步控制信号;PR和CLR不能同时有效,否则会出现Q的原变量等于反变量的错误。表中最后一行表示了D触发器的记忆功能。

表5-19 74LS74的功能表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。