我们需要非常低阻抗的电源分配网络(电源总线)以便为在PCB上的器件提供DC电压。从而使得IC和晶体管所要求的电源的波动不会引起电场或磁场的过度发射。这些电流的波动是由下列因素所引起的:

1)与信号负载有关的杂散寄生电容;

2)在图腾柱器件中的穿透电流;

3)核心(处理)噪声。

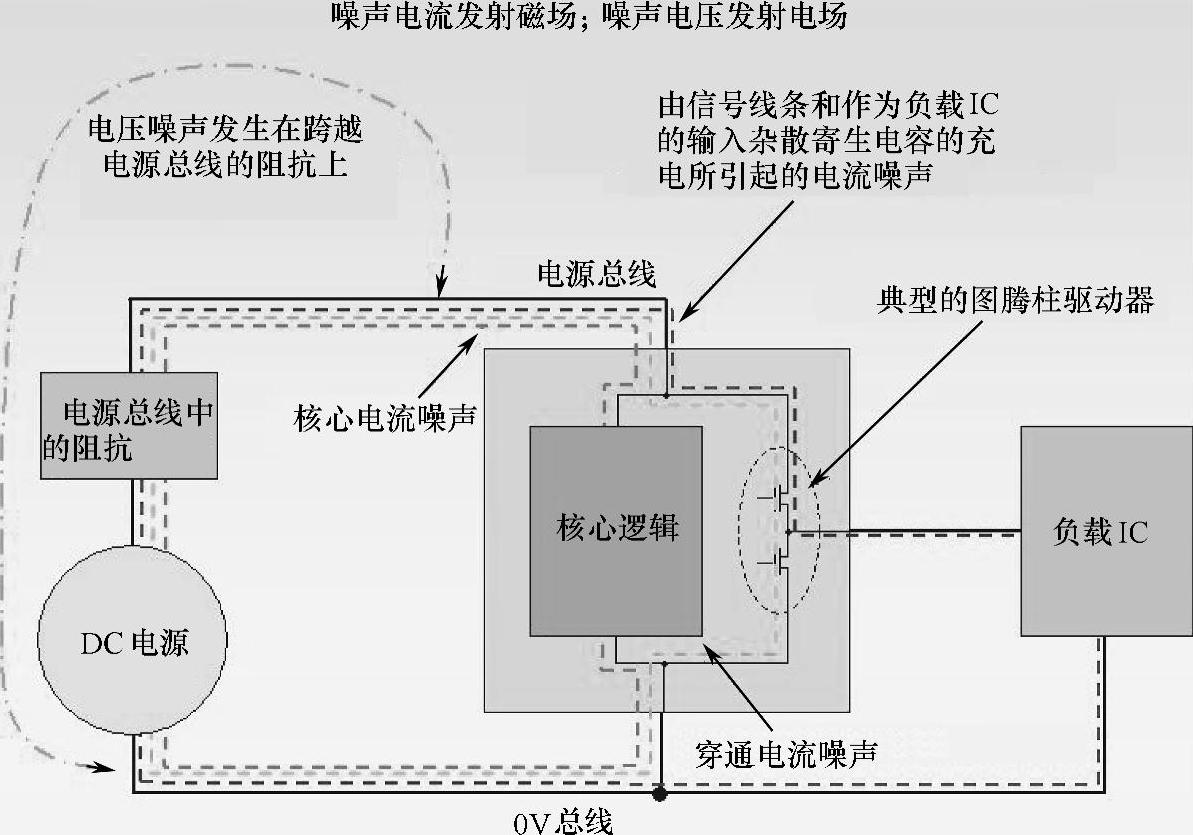

这三类电流噪声源以及由于它们在电源总线阻抗中流通时所造成的电压噪声示于图2-4-1中。

图2-4-1 电源总线噪声发射源

杂散寄生电容的存在是不可避免的。它们不仅与由器件终端、引线框架、搭接导线所形成的所有信号负载有关,而且还与半导体内部的本征电容有关。在计算时,这些电容必须计入到PCB本身的线条和焊盘所形成的杂散电容中去。虽然这些电容所涉及的电容总量非常小,经常仅为几十皮法而已,但当数字信号的过渡时间继续不断缩短的今天,由于这些电容的充放电所引起的瞬态电流与负载的增加有关,所以它们也会造成来自电源总线的发射电平。

在图腾柱类型驱动器电路开关的瞬间会引起穿透电流。这是因为在一个非常短暂的时间内,图腾柱中的上部和下部晶体管会同时导通,造成电源总线的短路。虽然完全可以设计出图腾柱驱动电路中的上部和下部元器件不具有重叠的导通时间,事实上,在大功率开关模式转换器中也经常是这样做的,从而防止在电源总线出现短路状态时所出现的非常大电流所造成元器件的实质性损坏。但这种做法在数字IC中并不典型。这是因为合成电流通路中的电感限制了穿透电流的上升速率。否则即便是在穿透期不那么短暂的场合也会引起非常高电平的穿透电流。

在频率超过30MHz的情况下,一个现代74HC集合逻辑器件的穿透电流可以超过由驱动它输出的信号所形成的电流变化高达15dB。尽管它的数据手册中规定的最大上升/下降时间为5ns(最大值),但在频率上升到(并且高于)600MHz时,这两类电流在电源总线中所形成的噪声都可以达到相当高的水平。(https://www.xing528.com)

在一个IC内部与电源总线有关的电感引起的电压噪声(相对于PCB而言)会出现在它的内部0V和电压参考上。这些噪声称之为“地起伏”和“限值起伏”(有时也称之为“限值崩塌”)。由于这些噪声会出现在IC的所有输入和输出插针上,所以,它们是来自一个器件和来自安装该器件的PCB的共模噪声发射的一个组成部分。为了获得一个PCB的良好EMC性能,重要的一点就是选择具有低地起伏和限值起伏的IC。但由于器件的选择并不属于本篇所讨论的范围,所以我们在这里不再就这个问题做进一步的讨论。有兴趣的读者可以参阅本书第1篇的有关章节。

核心噪声是诸如微处理器和大型现场(用户)可编程门阵列(FPGA)这类甚大规模集成(VLSI)IC的一个特征。它们通常都会有一个运行速度很高的核心半导体。这些必需驱动信号进入内部电容负载的内部电路也会遭受到穿透电流,所以它们对瞬态电流的要求也会加剧IC所要求的整体电流的波动。核心噪声电流的频率要比来自其他两个原因(杂散寄生电容和穿透电流)所形成的噪声电流频率高得多。例如,有些Xilinx公司的FPGA核心在一个50ps期间对电流的要求可以等效于一个至少扩展到13GHz的噪声频谱。

磁场发射是通过把DC电源电流环路的面积设计得尽可能小的方式来进行控制的。由线条提供0V和电源的地方,这些线条必须尽量的靠在一起。通常的做法是把0V和电源线条沿着它们的整个长度并排或沿着它们的宽面布线。

在本篇前面的第3章中已经讨论过,由于多种原因,一个PCB 0V平面的存在对EMC是至关重要的。假如我们有一个可用的0V参考面的话,我们就可以通过把DC电源总线线条(经常也称之为电源干线)在一个邻近于该0V参考面的PCB层面上布线来构成一个较小的电流环路。它们间的层距越小,环路面积就越小,从而形成的发射也就越低。

我们还曾提到过使用一个0V/电源参考面对的设计。在0V/电源参考面对设计中的0V和电源是使用在相邻两个层面上的平面来形成的。在PCB叠层中,使用这个技术可以获得最小可能的电流环路面积。0V/电源参考面越是靠近,就意味着具有越小的环路面积,也就表示具有越是低下的磁场发射。

电场发射是通过降低电源总线的阻抗方式来控制的。即在IC或晶体管汲取波动电流的连接点上,就所关心的频率范围尽可能降低电源总线的阻抗。这样做将有助于降低电流波动所形成的波动电压的幅值。我们知道,较小的电压波动所引起的电场发射也较低。在连接点上获得低阻抗的传统做法是在该点接入一个称之为去耦合电容的电容器,或简称去耦电容。同时,在一个给定的电源总线噪声电压条件下,减小电源总线和它的0V返回通路间距也会降低电场发射的程度。

借助于平面(相对于线条而言)的低DC阻抗和两个相邻平面之间的高互感来形成一个0V/电源平面对的分布电容是另一个获得电源总线低阻抗的方法。0V/电源参考面的层距越小,电源总线的阻抗也就越低。

不幸的是,去耦电容从来都不会是理想化的完善电容器。若设计不当,0V/电源参考面对也可以引起一些问题,特别是要对现代PCB进行有效的去耦往往更是一个相当困难的任务。本章接下来的其余部分就是要揭示这些问题以及目前可用来克服这些问题的措施。接着还要就掩埋电容技术以及HDI(请参阅本篇第6章)进行讨论。正像目前使用的FR4和通孔镀敷技术(THP)一样,这两种技术无可置疑的会在今后的几年中会在PCB设计和制造领域中变得无处不在和完全普及化。

旁路是去耦合的同义词。所以,旁路电容是去耦电容的另一种表述。在EMC领域中,并不经常采用旁路这个词,部分是因为去耦电容这个词比旁路电容更能确切表达它的含义和用途。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。