DMA是基于事件的模块,因此需要有一个外设中断触发才开始DMA数据传输。6个DMA通道的中断触发源可以独立配置,并且每一个通道都拥有各自独立的PIE中断,当DMA传送开始或结束时,可通过PIE中断告知CPU。6个通道中,有5个通道具有相同的性能,而通道1具有一个附加特性:其优先级可以配置成比其他通道的优先级高。DMA模块的核心是一状态机并与地址控制逻辑总线联系在一起。正是这个地址控制逻辑总线允许对传输过程中的数据块包括缓冲器间的“乒—乓”数据重新排列。

1.DMA的基本特征

DMA具有以下基本特征:

●具有独立PIE中断的6个通道。

●外设中断触发源:ADC模块排序器1和2、多通道缓冲串口A和B(McBSP-A,McBSP-B)的发送和接收、XINT1~7和XINT13、CPU定时器、ePWM1~6的AD-SOCA和ADSOCB信号以及软件强制触发。

●数据源/目的:L4~L7 16KSARAM、所有XINT区域、ADC模块存储器总线映射结果

寄存器、McBSP-A和McBSP-B发送和接收缓冲器、ePWM1~6/HRPWM1~6外设帧3映射的寄存器。

●字长度:16位或32位(McBSPs限制为16位)。

●吞吐量:4个时钟周期/字(对于McBSP读操作,5个时钟周期/字)。

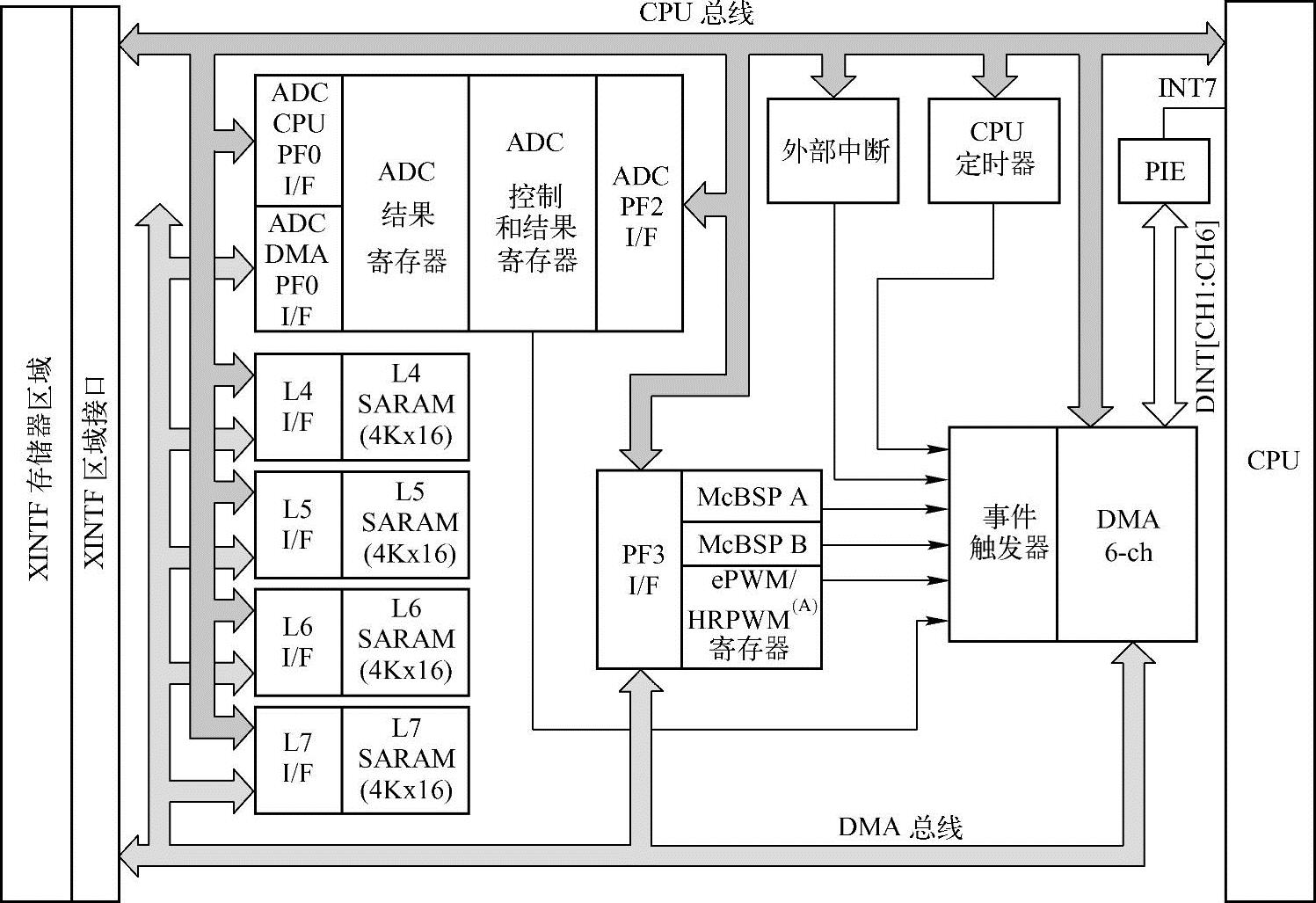

图5-17给出了DMA的结构框图。

图5-17 DMA结构图

2.外设中断事件触发源

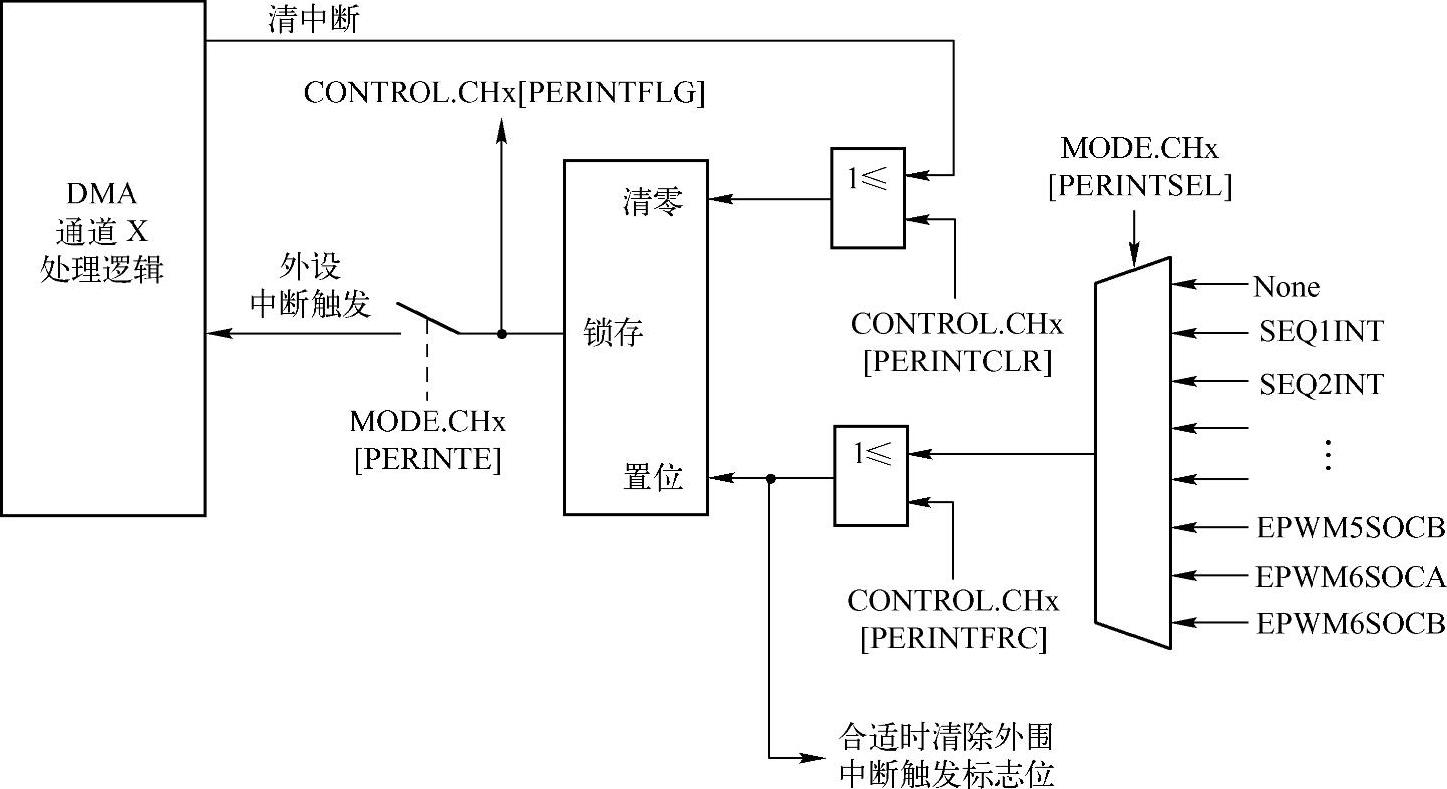

外设中断事件触发器可以为每个DMA通道独立配置18个触发源中的一个。在这些中断触发源中,有8个外部中断信号,这些信号可以连接到GPIO引脚上,这就大大增加了触发事件的灵活性。每个通道MODE寄存器中的PERINTSEL位用来选择该通道的中断触发源。一个有效的外设中断触发事件将锁存至CONTROL寄存器的PERINTFLG位,并且如果相应的中断和DMA通道被使能(MODE.CHx[PERINTE]和CONTROL.CHx[RUNSTS]位),则DMA通道将会响应中断事件。一旦接收到外设中断事件信号,DMA会自动向中断源发送清零信号,以保证后续中断事件的发生。

无论MODE.CHx [PERINTSEL]位的值是什么,软件总是可以通过PERINTFRC位给通道一个强制触发事件。同样,软件也可以通过CONTROL.CHx[PERINTCLR]位清除一个悬挂的DMA触发源。

一旦特定的中断触发源将通道的PERINTFLG位置位后,该位将保持悬挂状态直到状态机的优先逻辑启动该通道的数据传送;当数据传送开始后,该标志位将被清零。数据传送过程中,又产生了一个新的中断触发事件时,DMA通道将在当前数据传送完毕后,再按适当的优先次序,去响应这个新的中断触发源。若当前悬挂的中断响应结束前,第3个中断触发源产生,则错误标志CONTROL.CHx[OVRFLG]将被置位。如果外设中断触发事件与清除ERINTFLG标志位同时发生,外设中断触发事件有优先权,且PERINTFLG位仍保持置位。

图5-18给出了触发选择电路的结构图。

图5-18 外设中断触发选择电路结构图(https://www.xing528.com)

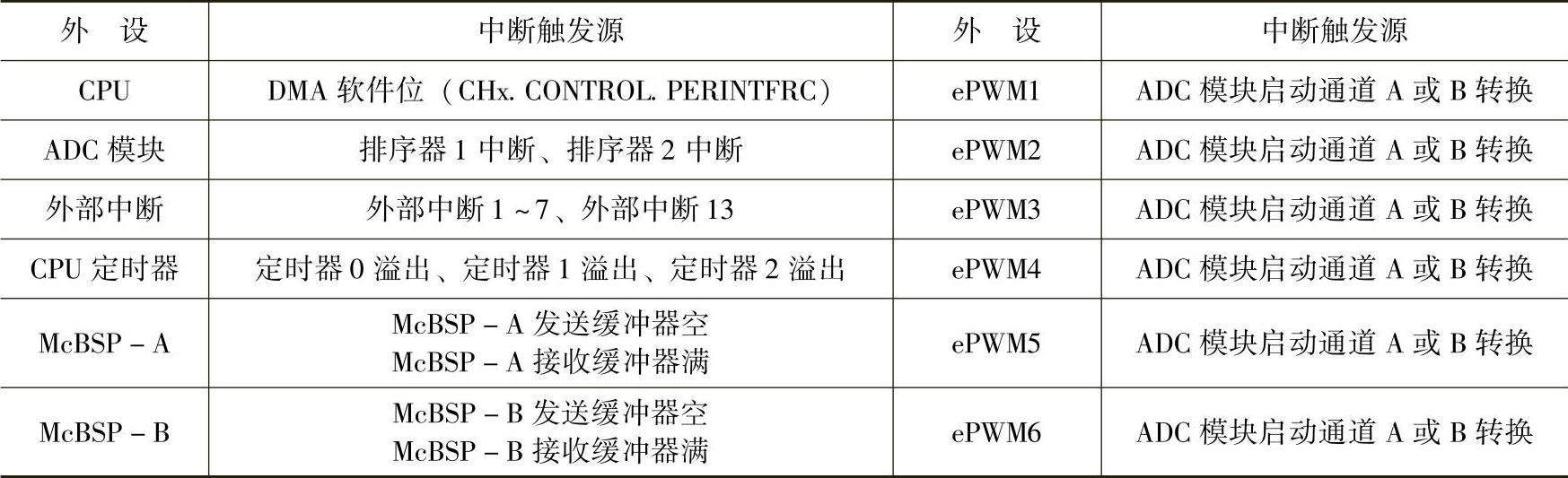

表5-29列出了可供每个通道选择的外设中断触发源。

表5-29 外设中断触发源选择

3.DMA总线

DMA总线包含22位的地址线、32位的读总线和32位的写总线。连接到DMA总线上的存储器和寄存器通过接口与CPU存储器或外设总线共享资源。与DMA总线相连的资源有:XINTF区域0,6,7、L4~L7SARAM、ADC模块存储器映射结果寄存器、McBSP-A和McBSP-B数据接收寄存器(DRR2/DRR1)和数据发送寄存器(DXR2/DXR1)、ePWM1~6/HRPEM1~6映射到外设帧3的寄存器

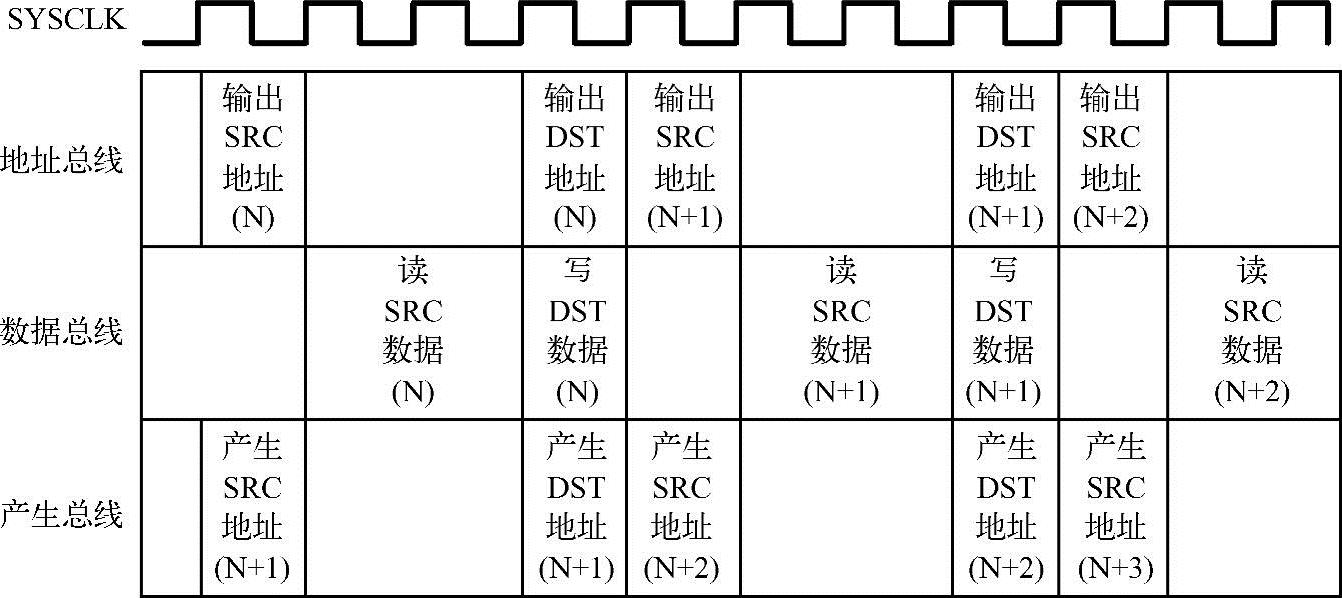

4.流水线时序和吞吐量

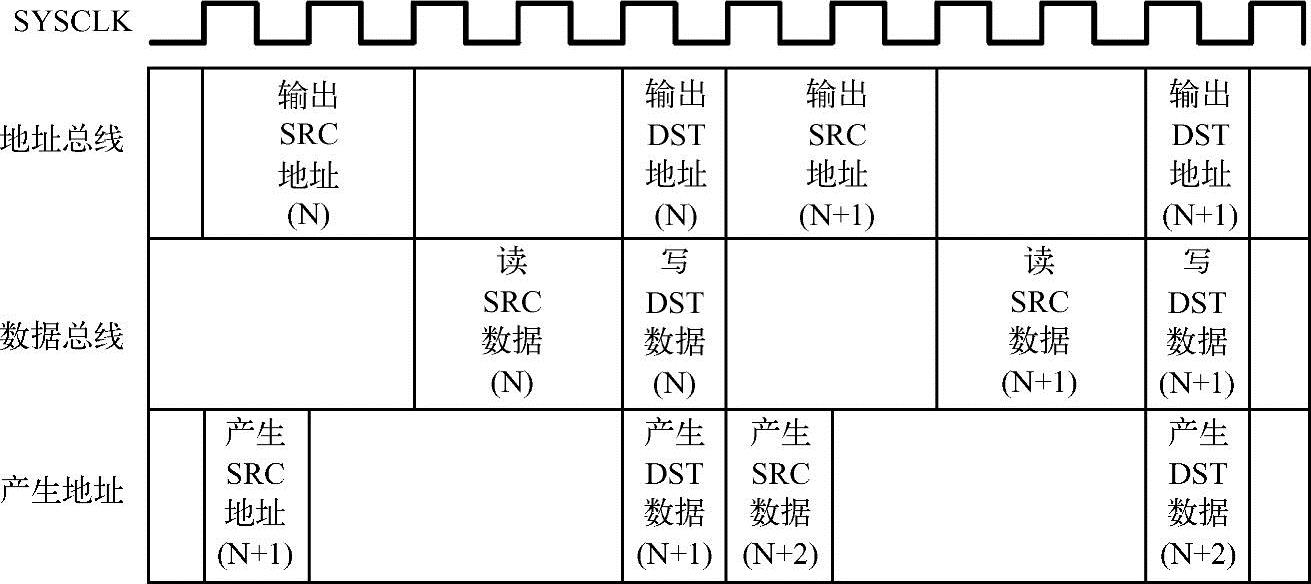

DMA包含了4级流水线操作,如图5-19所示。当DMA配置成使用McBSPs作为其数据源时,在传送数据过程中,读DRR寄存器会使DMA总线暂停一个时钟周期,如图5-20所示。

除了流水线操作外,还有以下性能会影响DMA的整体吞吐量:

●在每个数据帧(burst)传输的开始会附加一个时钟周期的延迟。

图5-19 DMA传输4级流水线

图5-20 带一个时钟暂停的读操作的4级流水线(McBSP为事件源)

●当从通道1高优先级中断返回时会附加一个时钟周期的延迟。

●32位的传输速度是16位传输速度的两倍(32位字和16位字的传输时间相等)。

●和CPU发生冲突时会产生附加延迟。

例如,从ADC模块中传送128个16位字至RAM,通道可以配置成传输8个16字的数据帧。便得到传送需要8帧×[(4时钟周期/字×16字/帧)+1]=520时钟周期;若通道配置成传送32位字,则传送将需要8帧×[(4时钟周期/字×8字/帧)+1]=264时钟周期。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。