1)逻辑门 逻辑电平 逻辑约定

逻辑门就是实现一些基本逻辑关系的电路。分立元件门电路目前已很少使用,但所有的集成门电路都是在分立元件门电路的基础上发展、演变而来的,所以有必要了解它们的工作原理。

在数字电路中,用高电平和低电平来描述两个逻辑状态,被称为逻辑电平,它们对应两个不同而具有确定范围的高、低电压,高电平对应相对较高的电压,而低电平则对应相对较低的电压,它们表示的都是一定的电压范围,而不是一个固定不变的数值。

在数字电路中,有两种逻辑约定。一种是正逻辑约定,即将高电平用“1”表示,低电平用“0”表示;另一种是负逻辑约定:高电平用“0”表示,低电平用“1”表示。本书如果不特殊声明,均采用正逻辑约定。

2)二极管门电路

(1)二极管与门

实现与逻辑关系的电路称为与门。一个硅二极管与门的电路和二输入与门的图形符号见图3.28。图中A、B是输入信号,F是输出信号,当两个输入信号进行四种不同情况的输入时,相应的输出电压可以估算求出(见表3.3)。显然,这里的3 V、3.7 V为高电平,而0 V、0.7 V为低电平。若采用正逻辑,状态赋值后,则可得到表3.4所示的逻辑真值表。由表3.4可以看出,输入信号A、B和输出信号F之间的关系为“与”逻辑,逻辑表达式为F=A·B。

图3.28 二极管与门

表3.3 图3.28电路电压功能表

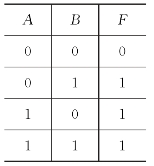

表3.4 与门真值表

(2)二极管或门

实现或逻辑关系的电路称为或门。一个硅二极管或门的电路和二输入或门的图形符号见图3.29。通过分析估算可列出表3.5所示的电压功能表。同样采用正逻辑约定,则可得到表3.6所示的逻辑真值表,因此,输入A、B和输出F之间的关系为“或”逻辑关系,其逻辑表达式为F=A+B。

图3.29 二极管或门

表3.5 图3.29电路的电压功能表(https://www.xing528.com)

表3.6 或门的真值表

(3)三极管非门(反相器)

实现非逻辑关系的电路称为非门。一个三极管非门的电路和非门的图形符号见图3.30。当输入A为高电平时,选择合适的RB、RC,使三极管工作在饱和区,则输出F为低电平;当输入A为低电平时,三极管工作在截止区,则输出F为高电平。因此,该电路的电压功能表应为表3.7。当采用正逻辑约定时,即可得表3.8所示的逻辑真值表。显然,输入A与输出F之间的关系为“非”逻辑关系,其逻辑表达式为F=A。

图3.30 三极管非门

表3.7 图3.30电路的电压功能表

表3.8 非门真值表

(4)MOS管非门

图3.31 MOS管非门

MOS管非门(反相器)的电路如图3.31所示,其中VT1为N沟道增强型MOS,VT2为P沟道增强型MOS。VT1和VT2的栅极接在一起作为反相器的输入端,漏极连在一起作为输出端,工作时VT2的源极接电源正端,VT1的源极接地。一般取VDD>UGS(th)1+|UGS(th)2|,UGS(th)1和UGS(th)2分别为VT1和VT2的开启电压。

当uI=0时,uGS1=0,此时VT1截止,相当于在D1、S1之间有一个开关断开。而uGS2=-VDD,即|uGS2|>|UGS(th)2|,使VT2导通,相当于在D2、S2之间有一个开关闭合。所以uO≈VDD,输出为高电平。

当uI=VDD时,uGS1=VDD>UGS(th)1,VT1导通,相当于在D1、S1之间有一个开关闭合。uGS2=0,VT2截止,相当于在D2、S2之间有一个开关断开。所以uO≈0,输出为低电平。

以上分析表明,该电路具有非逻辑功能。由于电路采用互补的NMOS和PMOS管,称为CMOS电路,工作时两只管子一个导通,另一个截止,电路内部工作电流几乎为0,功耗很小。因此CMOS结构的电路在集成电路中得到广泛应用。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。