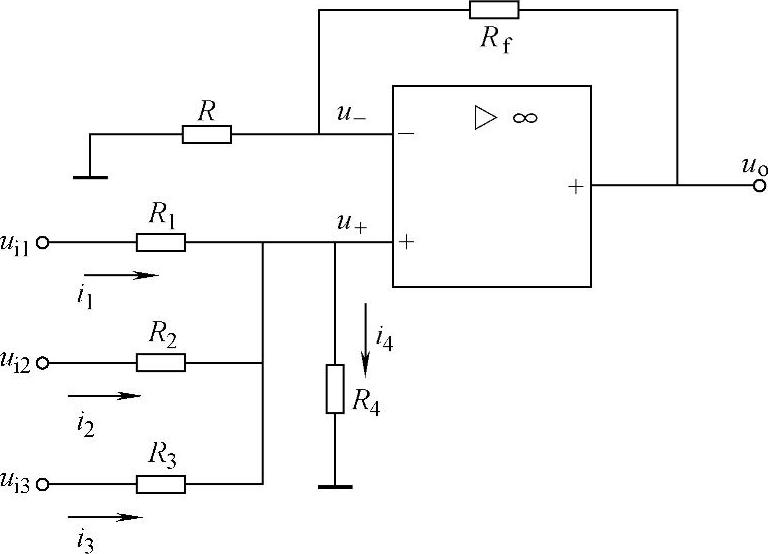

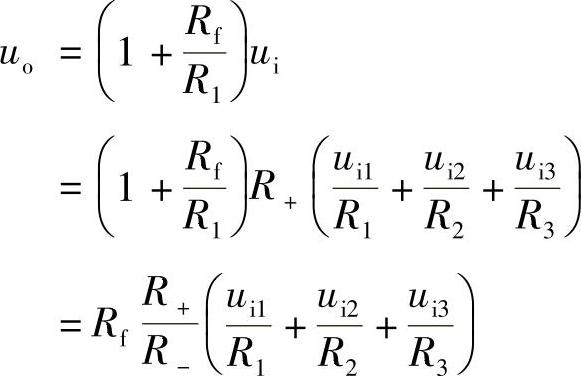

1.加法运算电路

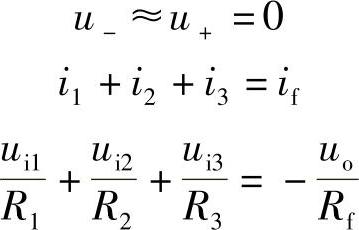

(1)反相输入加法运算电路

反相输入加法运算电路如图7-8所示,输入信号ui1、ui2和ui3均加在集成运放的反相输入端。根据“虚短”和“虚断”的概念可得

则输出电压为

若令R1=R2=R3=Rf,电路输出端再接一个反相器,则输出电压为

uo=ui1+ui2+ui3 (7-17)

反相输入端等效电阻R-和同相输入端等效电阻R+相等,则R4=R1∥R2∥R3∥Rf。

图7-8 反相输入加法运算电路

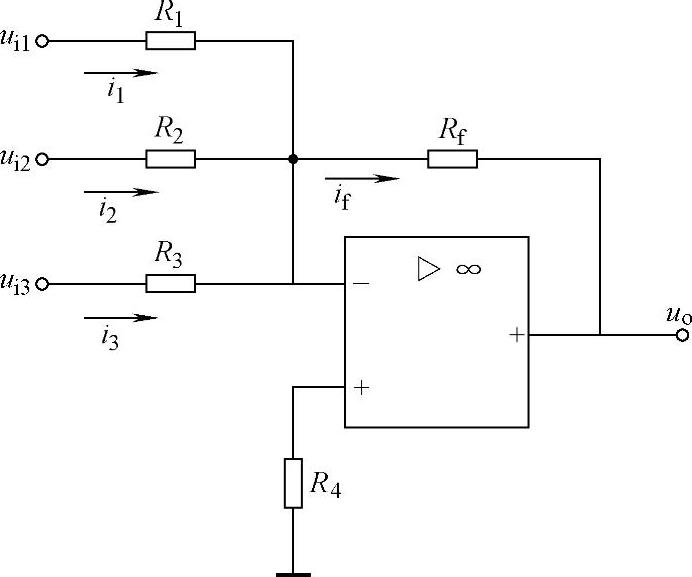

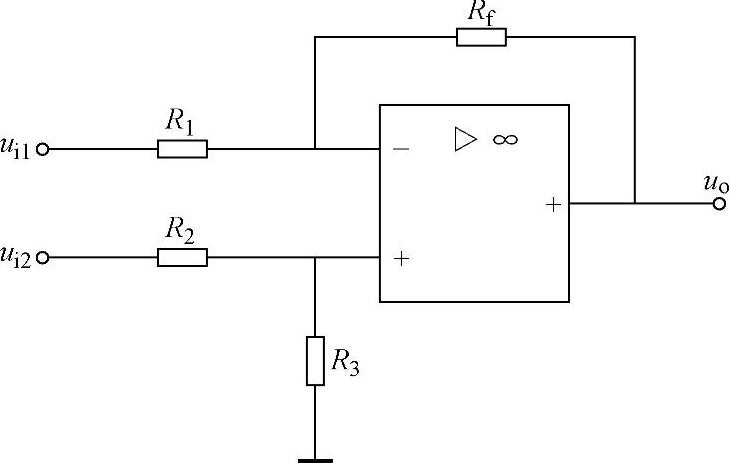

图7-9 同相输入加法运算电路

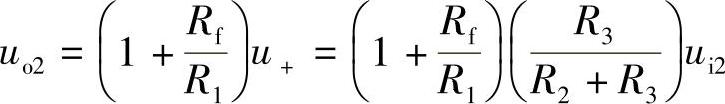

(2)同相输入加法运算电路

同相输入加法运算电路如图7-9所示,输入信号ui1、ui2和ui3均加在集成运放的同相输入端。根据“虚断”的概念可得

整理可得同相输入端电位u+为

式中,R+为同相输入端等效电阻,R+=R1∥R2∥R3∥R4。

根据式(7-9)和式(7-18)可得

式中,R-为反相输入端等效电阻,R-=R∥R f。若R-=R+,则

2.减法运算电路

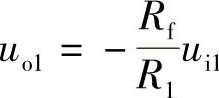

(1)差动输入减法电路

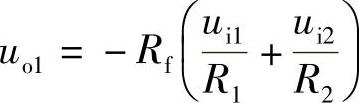

差动输入减法电路如图7-10所示,将两个输入信号分别加到集成运放的反相输入端和同相输入端,选择适当的电路参数,可以使输出电压正比于两个输入信号之差。利用叠加原理可求解该减法电路uo的表达式。

图7-10 差动输入减法电路

当ui2=0,ui1单独作用时,电路为反相比例运算电路,其输出电压为(https://www.xing528.com)

当ui1=0,ui2单独作用时,电路为同相比例运算电路,其输出电压为

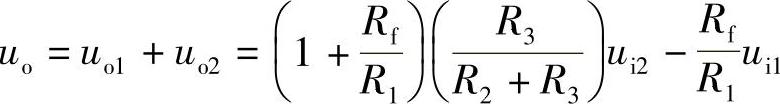

根据叠加原理可得两个输入信号作用时的输出电压为

若R1=R2,R3=Rf,则uo为

电路的差模输入电阻Rid=2R1,电路的共模抑制能力较差。

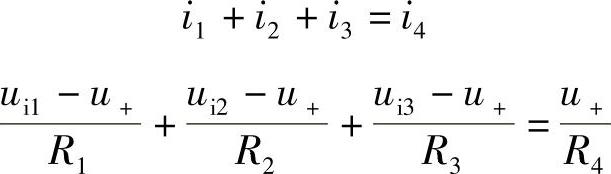

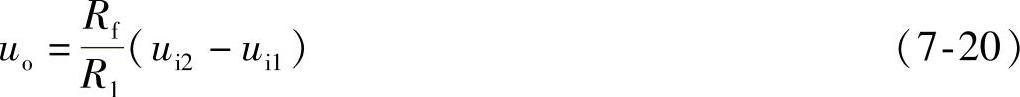

当多个信号同时作用于集成运放的反相输入端和同相输入端时,就可能形成如图7-11所示的差动输入加减法电路。若R-=R+,即R1∥R2∥Rf=R3∥R4∥R5。利用叠加原理可求解该加减法电路uo的表达式。

当ui3=ui4=0,ui1和ui2作用时,电路为反相加法运算电路,其输出电压为

当ui1=ui2=0,ui3和ui4作用时,电路为同相加法运算电路,其输出电压为

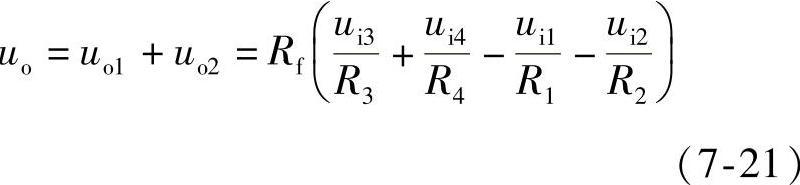

根据叠加原理可得所有输入信号作用时的输出电压为

图7-11 差动输入加减法电路

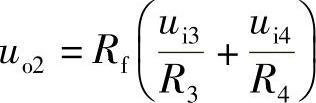

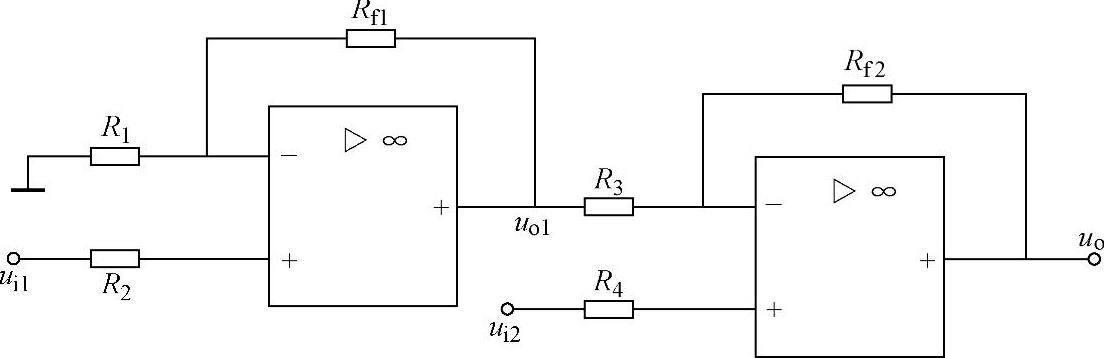

(2)双运放减法电路

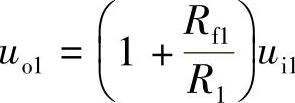

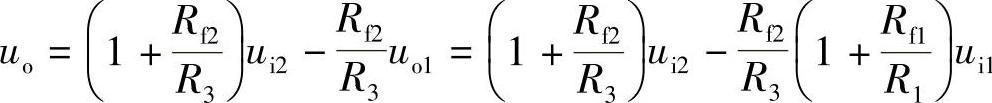

在单个集成运放构成的差动输入减法电路中,其输入信号同时加到集成运放的反相输入端和同相输入端,对于每个信号源,输入电阻均较小。为了提高输入电阻,可采用如图7-12所示的由集成运放构成的两级电路。第一级电路为同相比例运算电路,输出电压为

第二级电路的输出电压为

若R1=Rf2,R3=Rf1,则uo为

对于输入信号ui1或ui2来说,该电路的输入电阻均为无穷大。

图7-12 双运放减法电路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。