PXI-11154中采样模块主要功能是将每个通道中输入的模拟信号(电压)调理到A/D元件接收的范围并且将输入信号转换成为数字信号。采样模块主要由信号/地输入切换、交流/直流(AC/DC)耦合切换、功率驱动元件、程控放大器、A/D转换器和数字隔离元件组成。工作流程如下:电压模拟信号首先经过信号/地输入切换、交流/直流(AC/DC)耦合切换两个开关,然后在程控放大器作用下对信号进行放大以将信号调节到合适的范围,经过程控放大器后信号进入A/D转换器,最后A/D将电压模拟信号转换为数字信号,通过数字隔离元件直接进入到FPGA中进行数据处理。流程框图如图3-6所示。

图3-6采样模块流程框图

1.信号/地输入切换

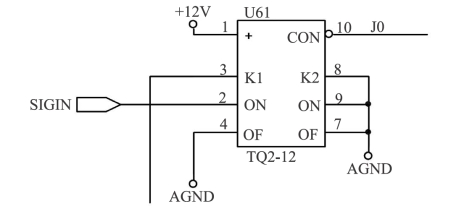

信号/地输入切换通过控制继电器TQ2-12实现。TQ2-12线圈的通断电就可以实现开关的通断,将信号和地两路信号分别连接到TQ2-12两端后控制其开关就可以实现在信号和地之间的切换。当进行正常采集时,输入端连接信号端,这样就可以采集到由传感器系统传送过来的电压信号。当系统进行校正零点时,需要除去噪声干扰,这时就可以将输入端接地(参考地)从而测得每个通道的零点值。信号/地控制继电器原理图如图3-7所示。

图3-7 信号/地控制继电器原理图

2.AC/DC切换

采样模块中能够实现AC/DC切换,即交流/直流切换。当选择交流时,信号中的直流成分将被去除;当选择直流时,实质上就是直通,信号中的交直流成分都能够通过。AC/DC控制继电器原理图如图3-8所示。

图3-8 AC/DC控制继电器原理图

3.功率放大器

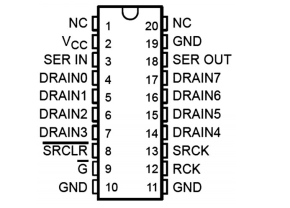

继电器TQ2属于低电流高电压负载,FPGA中的I/O引脚无法直接驱动继电器TQ2。因此必须在FPGA与继电器之间连接上功率放大器件——TPIC6B595。它是美国德州仪器公司生产带功率驱动的8位移位寄存器,能够用于驱动相对较高负载功率的元件,它的引脚图如图3-9所示。其工作原理是在串行时钟SRCK(第13引脚)上升沿时,将由FPGA发送的串行数据锁存在8位内部移位寄存器中。然后通过寄存器时钟RCK(第12引脚)将内部移位寄存器中的数据并行输出,一次可以输出8位数据,即一个TPIC6B595可以驱动8个TQ2继电器。TPIC6B595能够持续提供150mA的电流,瞬时最大电流可以达到500mA。它可以直接驱动继电器或者功率管等元件。

图3-9 TPIC6B595功能引脚图

4.程控放大器(https://www.xing528.com)

程控放大器选用PGA103,它是一款具有可编程增益功能的仪表放大器。PGA103特别适合应用于信号动态范围较大的电路中。它能够通过两路数字信号A1和A0对输入信号按照指定增益进行放大。A0和A1数字信号可直接与FPGA引脚相连接,这样就可以通过FPGA控制每个通道的增益放大倍数。PGA103可将增益设置为1、10和100,A0和A1与增益设置之间的关系和原理框图如图3-10和图3-11所示。

图3-10 PGA103原理框图

图3-11 PGA103增益设置

5.A/D转换器

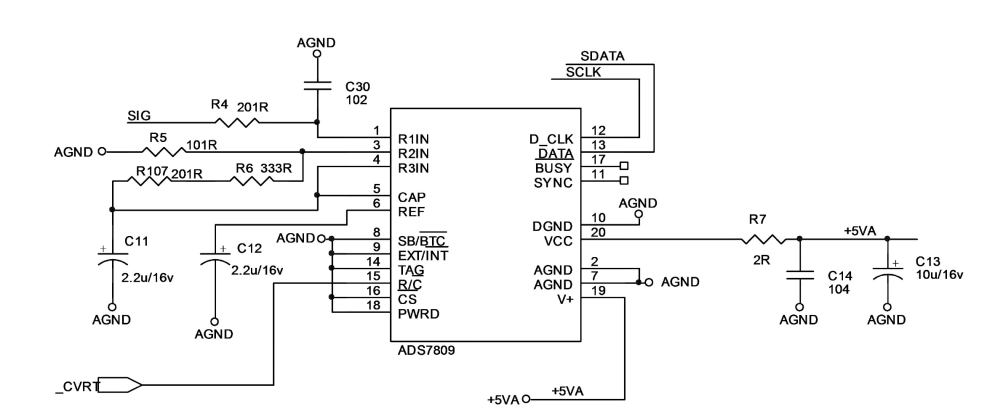

PXI-11154中采用ADS7809逐次逼近型A/D转换器,它的最高采样频率为100kHz,A/D分辨率为16位。ADS7809的主要功能是将在时间和幅值变化连续的模拟量(电压信号)转换成为离散的数字信号。在它内部完成了取样、保持、量化、编码四个步骤。在设计A/D电路时有三个重要问题需要考虑:电压量程范围、串行数据的生成和串并数据转换。

ADS7809输入电压的量程可以分为6档。通过R1IN、R2IN和R3IN个不同的连接方式能够选择其中一档。一旦模拟量的输入范围确定,程控放大器PGA103就要将信号调理与A/D模拟量相对应的输入范围之内。系统选择的是±10V的输入范围,在这种输入模式下R1IN通过一个200Ω的电阻与地相接,R2IN通过一个100Ω的电阻与地相接,R3IN通过一个1000pF的电容相连接。ADS7809及其外围电路原理图如图3-11所示。

图3-11 ADS7809连接原理图

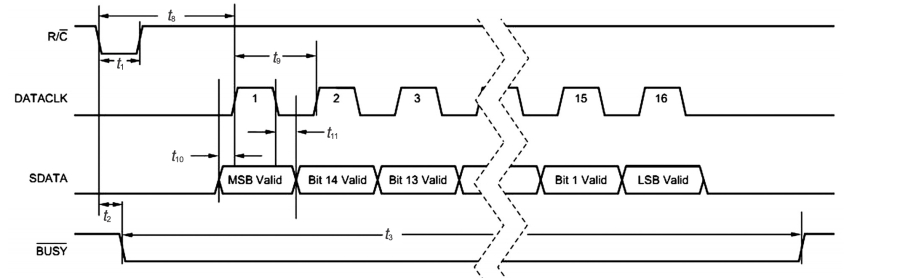

图3-12 串行数据转换的时序图

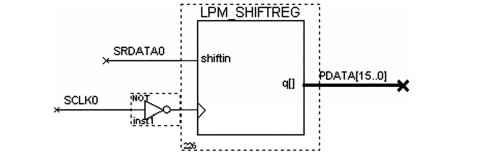

ADS7809能够产生16位串行数据,但是计算机进行分析处理时需要并行数据。因此串行数据在进入计算机前要转换为并行数据,整个工作由FPGA完成。串并转换过程类似于前面介绍的TPIC6B595元件。在EP1C6Q240C6N内部设计一个16位的移位寄存器,它的功能就是串入并出。在串行时钟作用下,16位串行数据分别依次传送到FPGA内部的移位寄存器中保存。等到16位的移位寄存器写满后,一次性将移位寄存器的16位数据传送出去,完成串并转换。整个过程的FPGA设计如图3-13所示。

图3-13 串并数据转换数字逻辑设计图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。