经过采样模块后,连续模拟信号转换为离散数字信号进入控制逻辑单元FPGA。FPGA主要完成数字逻辑电路功能,逻辑电路分为组合逻辑电路和时序逻辑电路,时序逻辑电路又可分为同步时序逻辑电路和异步时序逻辑电路。在PXI-11154采集模块设计中,主要使用了组合逻辑电路和同步时序逻辑电路。在同步电路中所有触发器的状态改变都受同一时钟控制,这一点在PXI-11154时钟设计中非常重要。

为减小偏斜(Skew)与抖动(Jitter),系统采用全局时钟作为时钟输入。时钟电路主要是为A/D、存储电路和其他时序电路提供稳定精确的工作时钟信号。本节中将重点介绍一下A/D转换器的工作时钟。

式(3-9)是实现在无信息损失情况下保证能够完整重构原始数据的必要条件,当然这只是理想状态下的条件。在实际工程应用中,为保证能够减小重构数据的失真程度,在时域分析时,采样频率一般为被测信号最高频率的10~15倍。如果要进行频域分析时,根据Heisenberg测不准原理,可适当降低一下采样频率,通常为6~10倍。PXI-11154可以灵活的分档位设定采样频率,共分为10档,最高采样频率为100kHz,最低为100Hz。在FPGA内部采用编码与之对应,如表3-3所示。

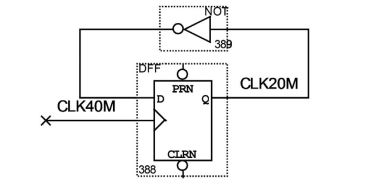

为保证时钟的精确性,同时考虑到FPGA中其他时序电路的需要,设计中采用40MHz高精度有源晶振作为时钟源。40MHz时钟通过全局时钟传送到FPGA中,经过分频可降为需要的工作时钟。FGPA中分频电路主要采用的是二分频逻辑电路,对于不规则分频可使用计数器完成。二分频电路采用D触发器和一个非门反相器组成,原始时钟经过非门反向后对时钟进行一次二分频,分频信号接入到D触发器的输入端。这样原始的40MHz时钟频率就转换为20MHz,如果再对20MHz时钟信号分频就变成了10MHz,以此类推就能够得到精准的低频率时钟信号。采样频率编码表如表3-3所示。FPGA中二分频电路如图3-14所示。(https://www.xing528.com)

表3-3 采样频率编码表

图3-14 二分频逻辑电路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。