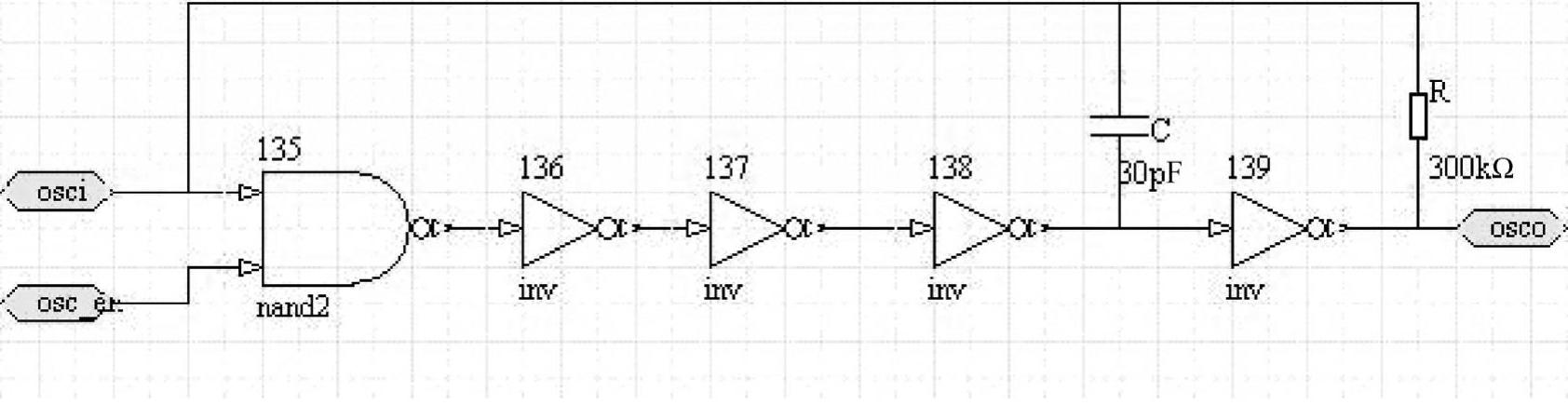

1.振荡器逻辑图

D508项目中有两个振荡器,它们都属于产生方波的多谐振荡器,也称为张弛振荡器或充放电振荡器,这种振荡器的工作特点是储能元件(通常是一个电容)在电路两个门限电平之间来回充电和放电。假设电路保持在一种暂稳态,当储能元件上的电位达到两个门限电平中的某一个值时,电路转换到另一种暂稳状态,然后储能元件上的电位往相反方向变化,当其到达另一个门限电平时,电路返回原来的暂稳状态,如此循环不已,形成振荡。

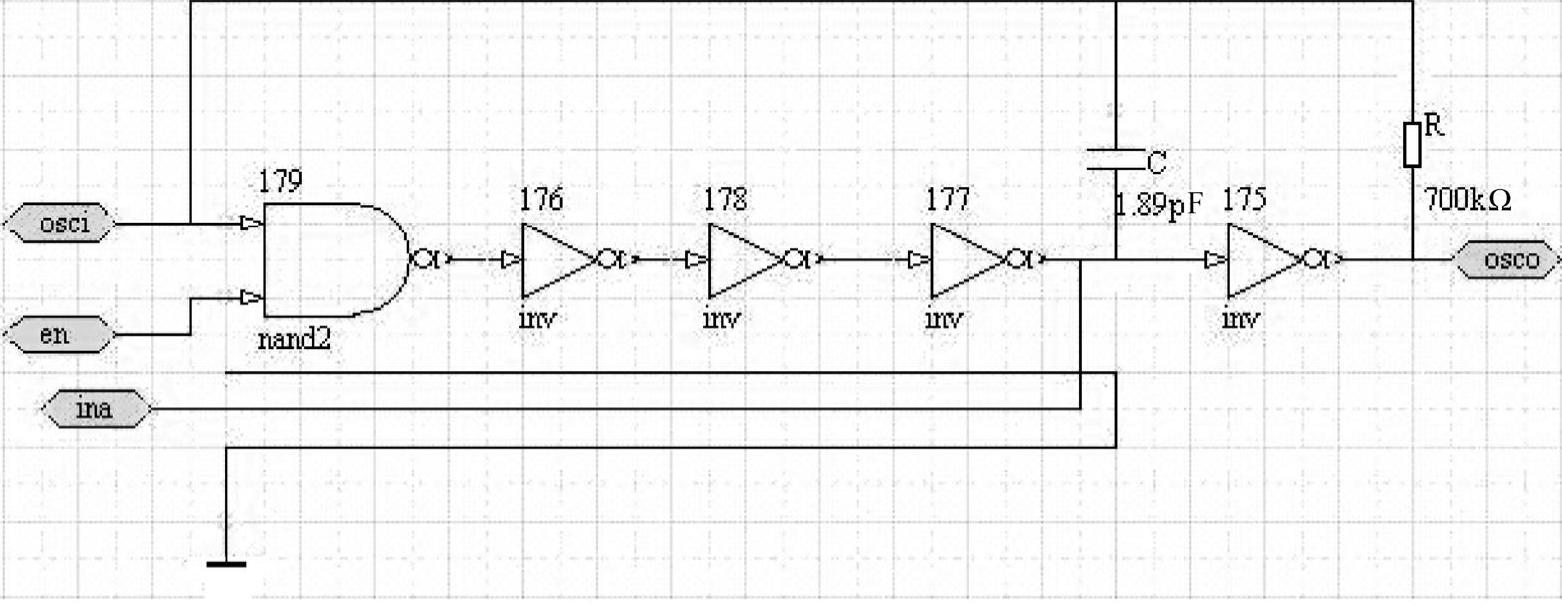

D508项目中的低频、高频两个RC环形振荡器是典型的张弛振荡器,是由奇数个反相器首尾相连组成的,它们的逻辑图分别如图3-7、图3-8所示。图3-7中有两个输入端,一个是振荡器输入端osci,另外一个是振荡使能输入端osc_en,用于控制振荡器是否起作用,当osc_en为低电平时,振荡器就无法起振,因而不起作用。除了以上两个输入端外,还有一个振荡输出端osco,另外就是一个电阻和一个电容。在图3-8中,同样是两个输入端osci、osc_en和一个输出端osco;另外还有一个双向端口ina,这个信号在版图设计时需要作特殊的考虑,下面将具体描述。

图3-7 低频振荡器逻辑图

图3-8 高频振荡器逻辑图

2.振荡器的版图设计

(1)电容类型的选择

因为振荡器的频率f=1/RC,在电阻满足要求的条件下,电容的精确度越高,对频率的影响也就越低。为了提高电路整体的可靠性和稳定性,最终选择精确度较高的PIP电容来做振荡器的振荡电容。

(2)电容形状的考虑

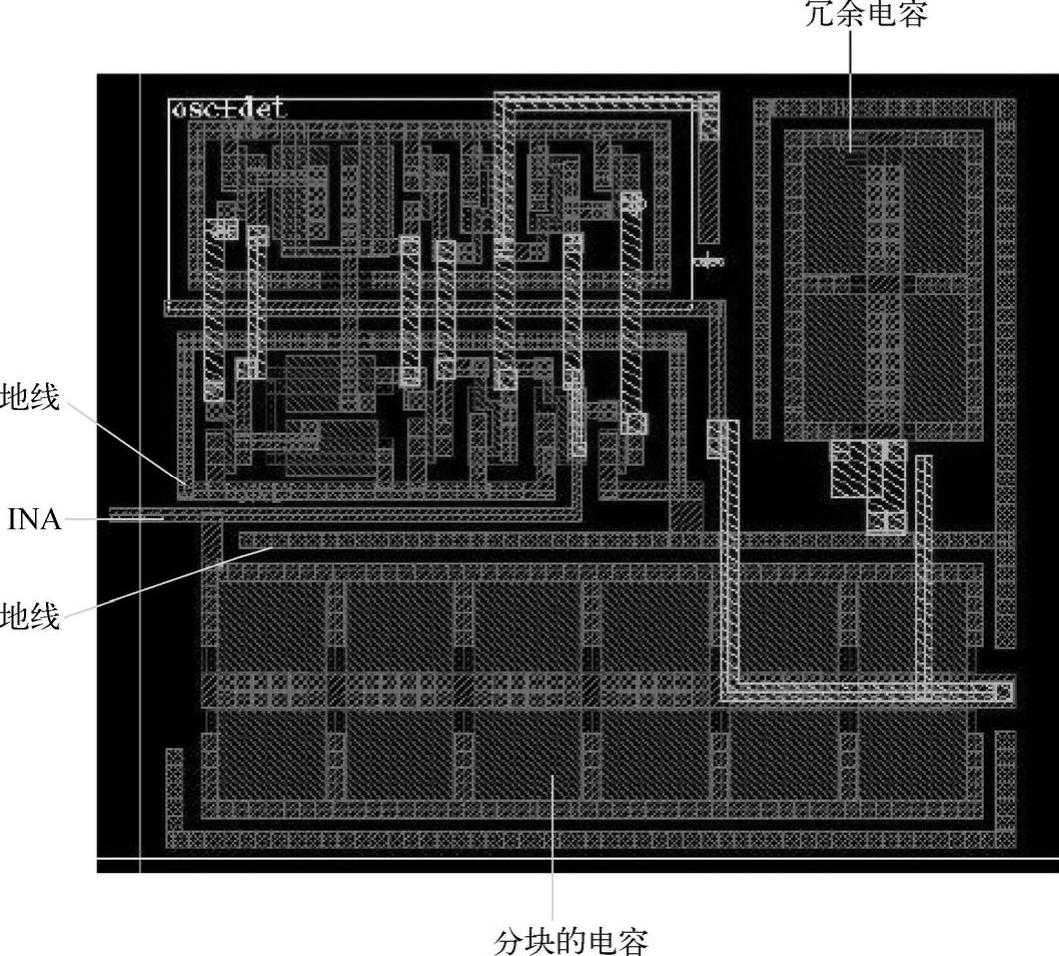

从图3-7、图3-8中可以看到,低频、高频振荡器电路内部各需一个振荡电容,而PIP电容的单位面积的电容值为0.73fF/μm2,因此即使振荡电容值小的高频振荡电路中,所需要的电容面积也要为3560μm2。若用一整块电容来完成,电容均匀性不好,原因是电容在工艺制作过程中会造成一定的误差,因此分成了若干块小的电容,并将多个小电容通过并联的方式来组成一整块电容,在以下振荡器版图中可以看到电容都是分成若干小块的。

(3)冗余电容的设计

集成电路版图除了要体现电路的逻辑功能并确保版图与电路的对比(Layout vs.Schematic,LVS)验证正确外,还要增加一些与LVS无关的图形,以减小工艺过程中的偏差造成的影响,通常称这些为冗余设计。这些冗余设计是为了防止刻蚀时出现刻蚀不足或刻蚀过度而增加的,比如金属密度或多晶硅密度不足,就需要增加一些相应的冗余设计,以增加它们的密度。另外一些则是考虑到光的反射与衍射,关键图形四周情况不一致,会产生因曝光因素而影响到对称尺寸的精确性。(https://www.xing528.com)

冗余设计包括了冗余MOS管设计、冗余电阻设计和冗余电容设计等。D508项目的设计中就采用了冗余电容的设计,以保证电容的稳定性和可靠性。

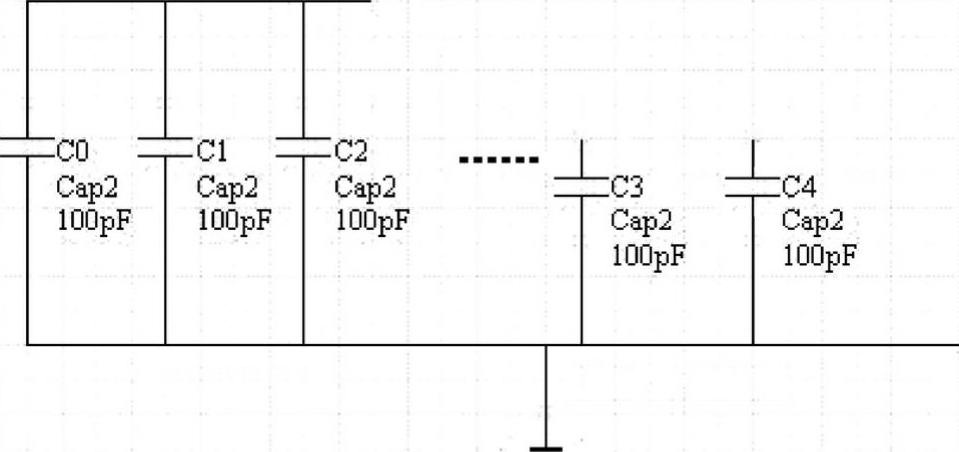

D508项目采用冗余电容的另外一个目的是为了今后方便进行修改和调节,因此在设计振荡电容时考虑了留30%的冗余电容,在需要的时候通过改版来释放使用。冗余电容C3、C4和有效电容C0、C1、C2采用了图3-9所示的连接方式。由图3-9可知,有效电容的上极板接到电路内部,下极板接GND;冗余电容的上极板悬空,下极板接GND。在设计电容版图时,电容的下极板是一整块的多晶,再在多晶的一周打上接触孔,通过一铝连接到GND上。在以下两个振荡器的版图中可以看到分别设计了一些冗余电容。

图3-9 冗余电容和有效电容的连接方式

(4)振荡器中保护环的使用

MOS集成电路工艺中,当金属线从氧化层上通过时,金属线和场氧化层及下面的硅衬底之间会形成一个MOS管。如果金属线上的电压足够高时,也会使场区的硅表面反型,在场区形成导电沟道,这称为场反型或场开启。如果金属连线跨过两个扩散区,在场反型时就形成一个场区寄生MOS晶体管,这种寄生MOS晶体管把不该连通的两个区域接通,破坏了电路的正常工作。为了使集成电路中每个MOS管之间具有良好的隔离特性,在版图设计中采用增加沟道隔离环的方法提高开启电压,实现MOS管之间的隔离。在CMOS集成电路中,PMOS管的隔离环是制作在N-型衬底上的N+环,NMOS管的隔离环是制作在P-型衬底上的P+环,因此保护环在版图设计中是非常重要的。在设计振荡器版图时,PMOS、NMOS管单独用环保护起来(包括NAND、INV的几个门的PMOS管放在一个环中;NMOS管放在另一个环中)。

(5)高频振荡器中敏感信号INA的处理

在版图设计中,如果连线较长,那么连线的平板电容和边缘电容会使工作速度降低,更重要的是,线间电容导致了显著的信号耦合。通过在版图中“屏蔽”敏感信号可以减小这种耦合,通常在敏感信号两边各放置一条地线,这样就把“噪声”干扰线发出的大部分电场线终止于地线而不是该信号线。这样做比单纯地把信号线与干扰线隔开更有效果,但是这种屏蔽所付出的代价是布线更加复杂,同时信号线与地之间的电容变大(线间电容影响)。还可以将敏感信号线用上、下两层金属地线包围,完全隔离外部电场线,但是这根信号线的对地电容更大,而且用到了三层金属,从而使其他信号的布线变得更复杂。

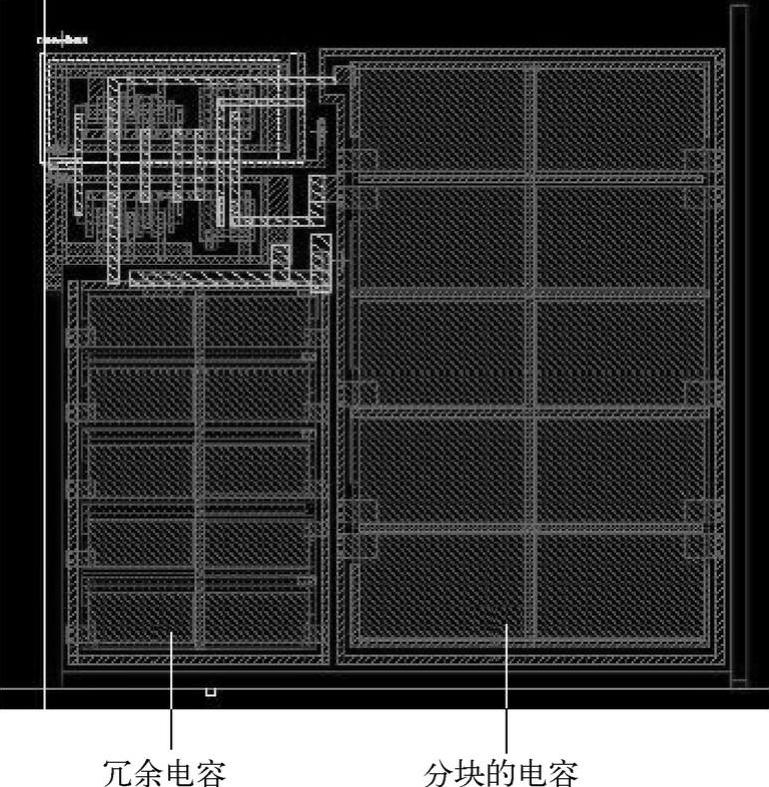

D508项目的高频振荡器中有一根非常敏感的线,名称为ina,在设计版图的时候,需要重点考虑。首先这根线不要太粗,尽量用一根金属线完整地从开始走到结尾,如果无法做到,那么就用多晶这一层作为中间的连接,而不要用有源区来连接。另外为了尽量减少ina与芯片内部其他信号的耦合,采用了地线保护的方法。图3-10所示是低频振荡器版图。图3-11所示是高频振荡器版图。

图3-10 低频振荡器版图

图3-11 高频振荡器版图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。