在集成电路设计中,为了实现多种不同的功能组合,经常在设计时采用掩膜选项(mask option)技术,这样可以同时设计出多种不同的功能产品,只需要对其中一层掩膜版作部分修改就可以实现,从而提高了设计效率,降低了设计成本。

D508项目中在多个逻辑模块中都采用了Metal2作为掩膜选项,因为在集成电路加工工艺中,Metal2在Metal1的上一层,在改版的时候较方便。

1.时钟产生模块

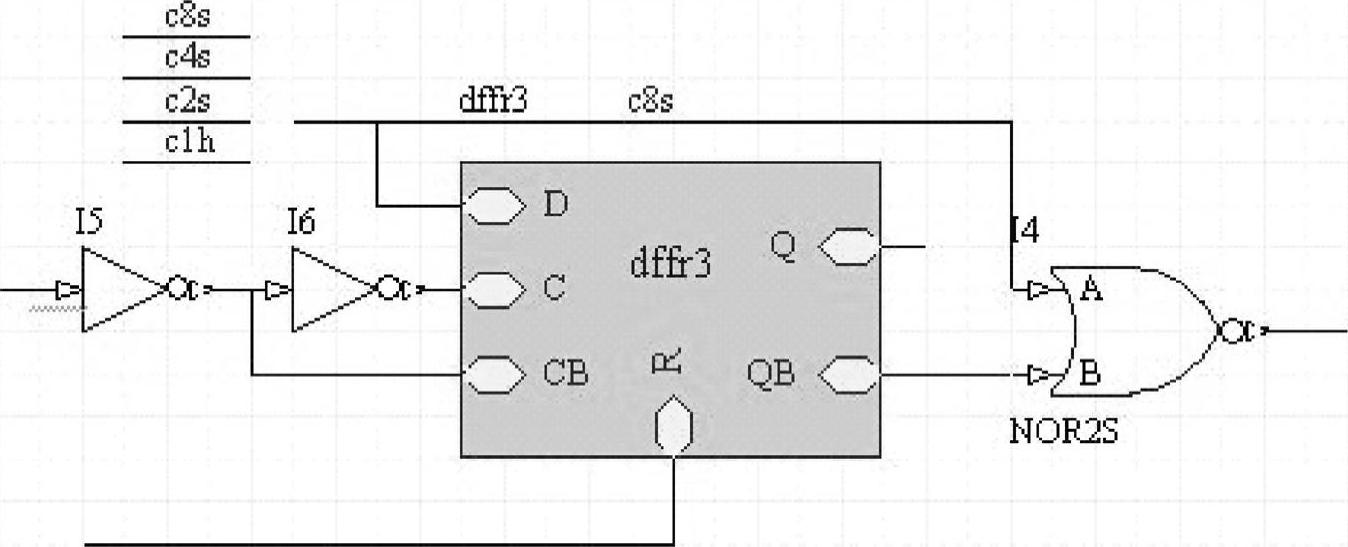

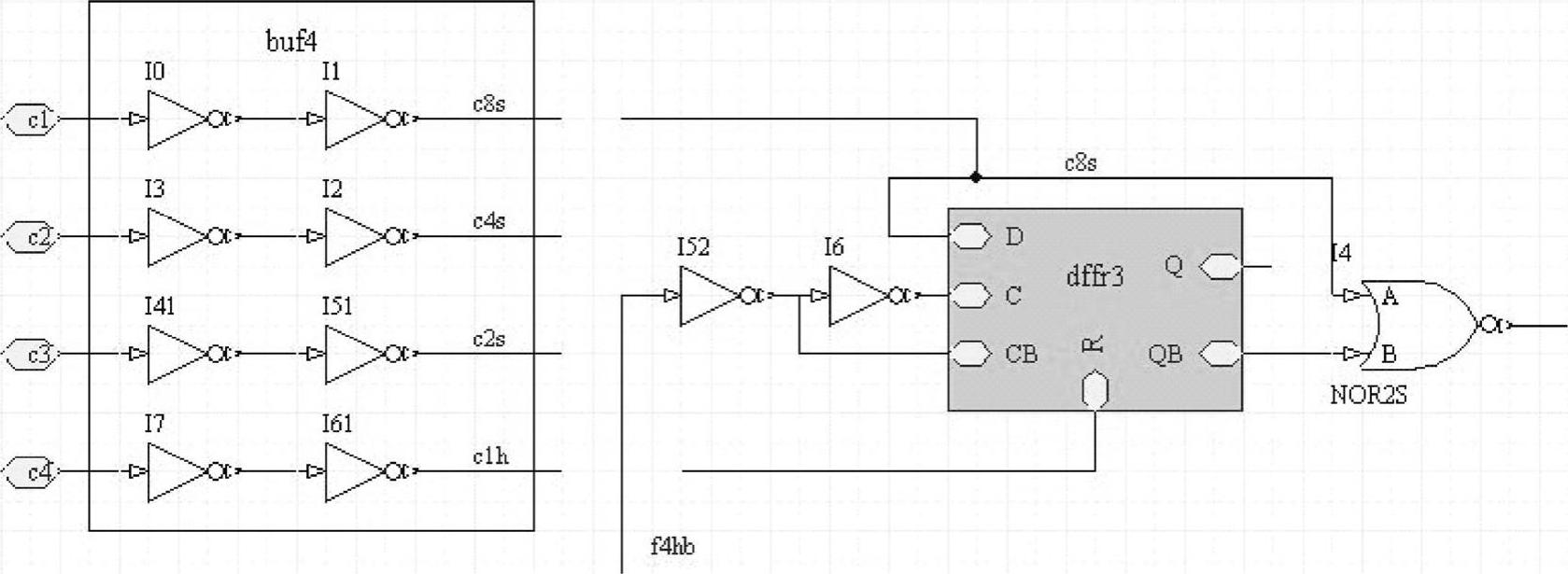

时钟产生模块中掩膜选项原始逻辑图如图5-8所示,连接到触发器dffr3的D端的信号是c8s,通过Mask option,该信号也可以连接到c4s、c2s和c1h上,这样就实现了不同的功能。为了保证在布局布线的时候,c8s、c4s、c2s和c1h这4个信号能够紧挨在一起以便于做option,于是创建了一个buf4的单元,结构是两级反相。时钟产生模块中掩膜选项修改后的逻辑图如图5-9所示。在布局布线完成之后,连接到触发器dffr3的D端信号可以方便地从以上4个信号中选择。

图5-8 时钟产生模块中掩膜选项原始逻辑图

图5-9 时钟产生模块中掩膜选项修改后的逻辑图

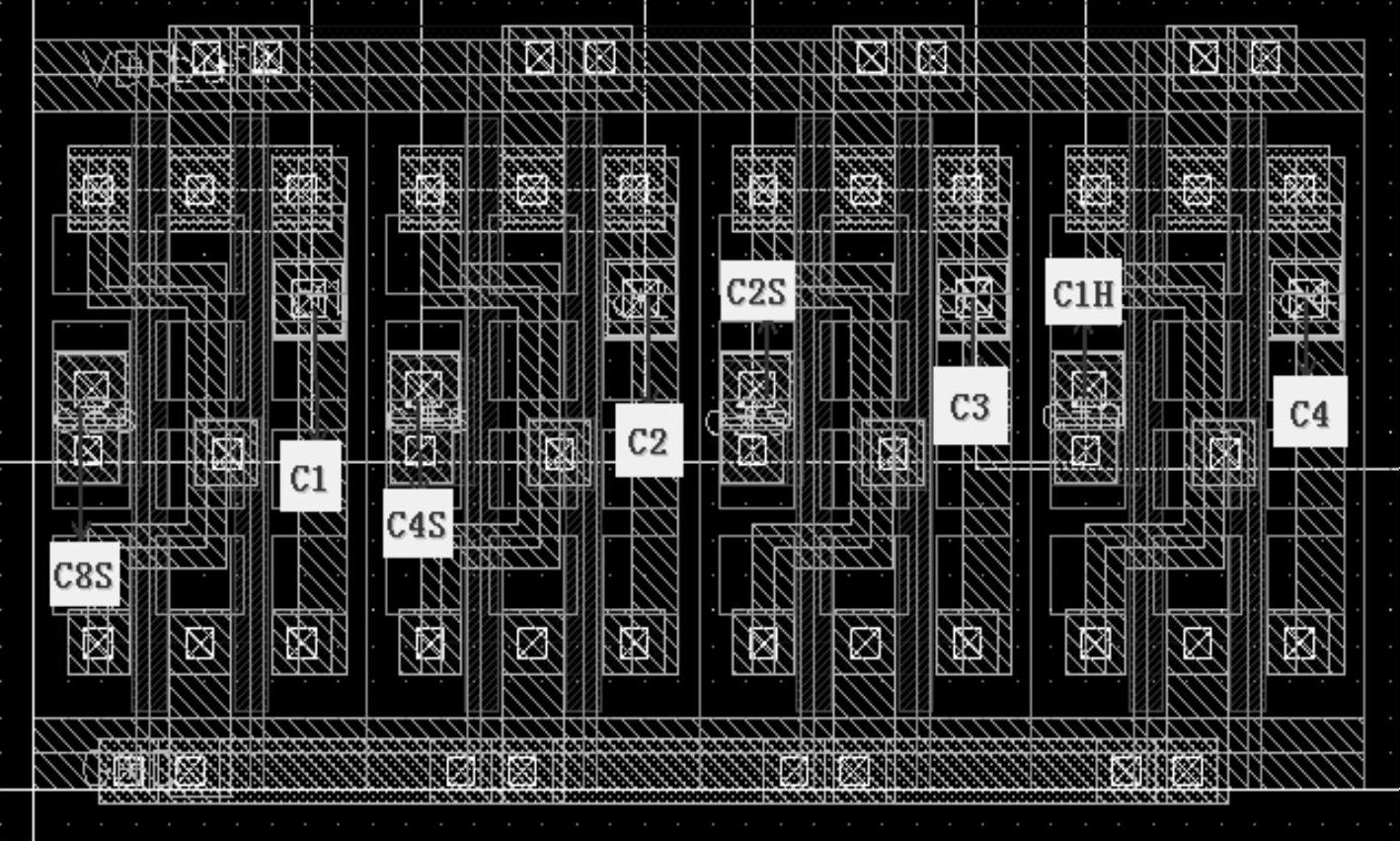

buf4单元版图如图5-10所示。在该图中,c1、c2、c3和c4四个输出端通过二铝可以方便地跟触发器的D端进行连接,从而体现了掩膜选项逻辑实现的灵活性。

图5-10 buf4单元版图

2.延时模块(https://www.xing528.com)

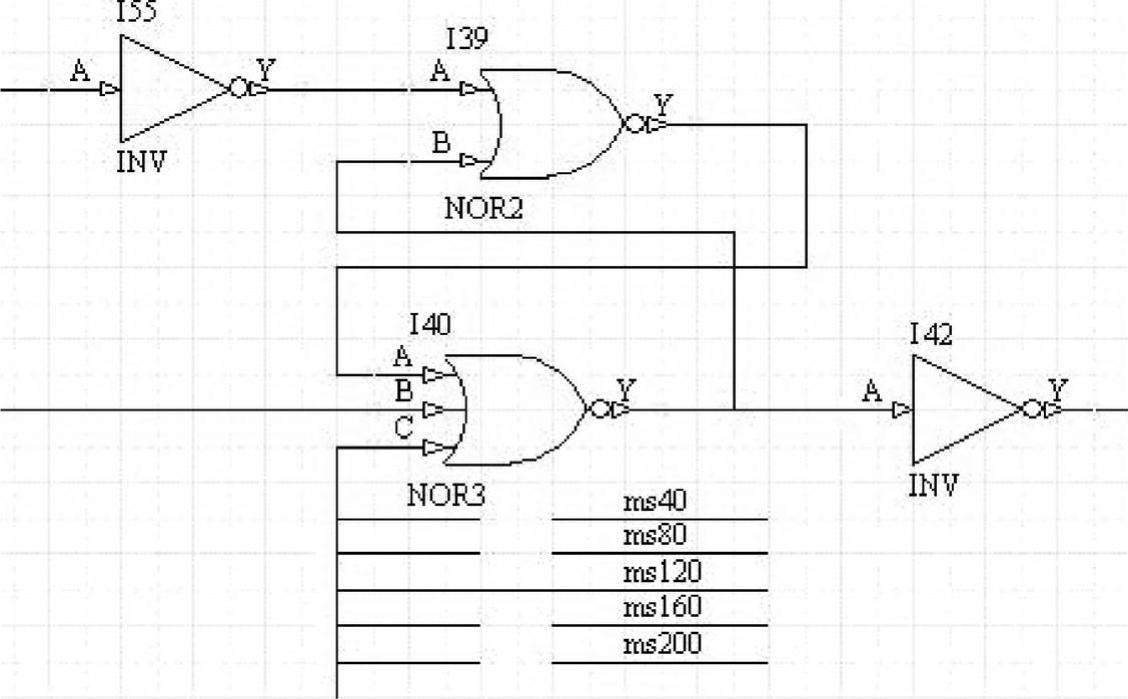

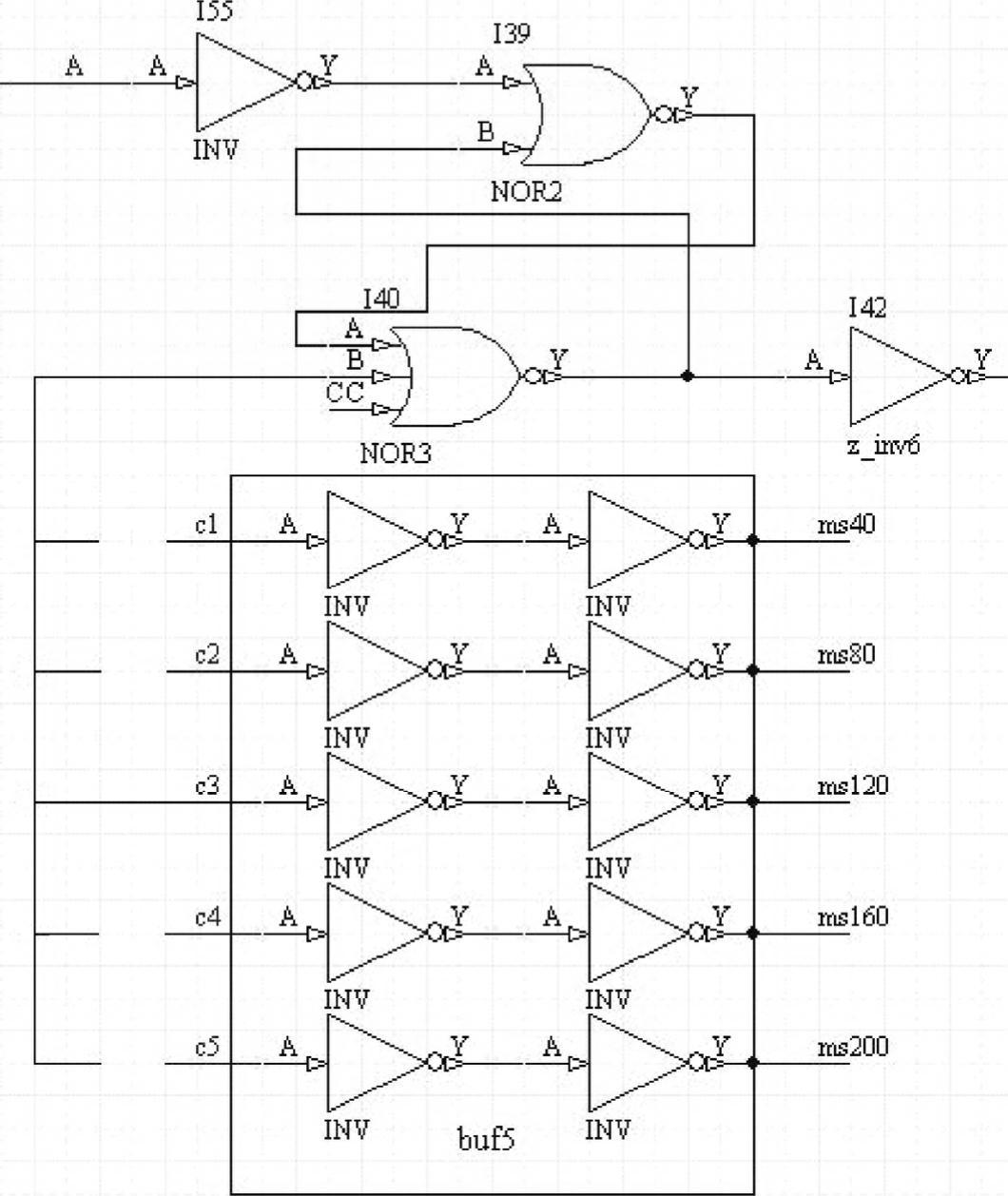

同时钟产生模块类似,在延时模块中也有一个掩膜选项,其原始逻辑图如图5-11所示,其中ms40、ms80、ms120、ms160和ms200这5个信号通过掩膜选项可以分别连接到或非门I40的一个输入端,从而实现不同的逻辑功能。

图5-11 延时模块中掩膜选项原始逻辑图

图5-11中将ms40、ms80、ms120、ms160和ms200这5个信号分别放置在或非门NOR3的其中一个输入端位置,表示这5个信号都可以连接到这个或非门的其中一个输入端口,而如何连接主要取决于芯片功能的要求。

为了保证在布局布线的时候,ms40、ms80、ms120、ms160和ms200这5个信号能够紧挨在一起以便于做option,于是创建了一个buf5的单元,结构也是两级反相,延时模块中掩膜选项修改后的逻辑图如图5-12所示。

图5-12 延时模块中掩膜选项修改后的逻辑图

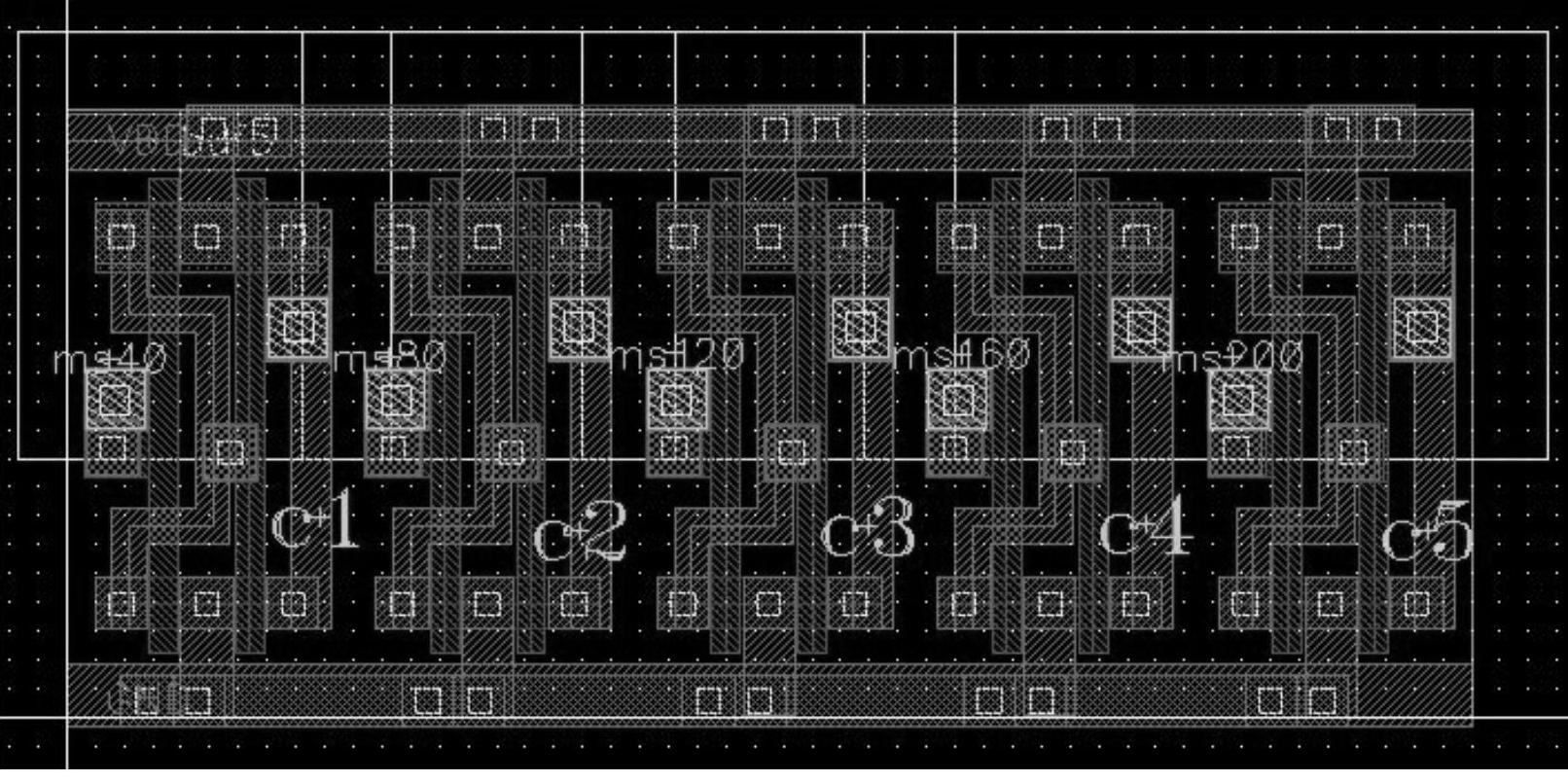

buf5单元的版图如图5-13所示,在布局布线完成之后,连接到或非门I40的一个输入端的信号可以方便地从以上5个信号中选择。

图5-13 buf5单元的版图

除了以上列举的两个掩膜选项外,在D508项目中还有其他多处掩膜选项,如振荡器使能信号的连接处、TG2端口上拉电路中P型倒比管的漏极连接处(如图3-12b所示)等,在版图设计时都采用跟以上类似的方法进行掩膜选项的设置。通过这些掩膜选项的设计可以最大限度地降低改版次数和芯片制造成本。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。