同步时序电路中所有触发器都受同一个时钟信号控制,所以分析方法比较简单。一般按如下步骤进行:

① 根据给定逻辑电路写出驱动方程和输出方程;

② 将各触发器的驱动方程代入相应触发器的特性方程,即得到各触发器的状态方程;

③ 根据输出方程和状态方程,列状态表、画状态图或时序图;

④ 确定电路的逻辑功能。

上述对时序逻辑电路的分析步骤不是一成不变的,可根据电路繁简情况和分析者对电路的熟悉程度进行取舍。

例11.2.1 试分析如图11.2.1所示电路的逻辑功能。

图11.2.1 例11.2.1的逻辑电路图

解:这是一个由两个JK触发器和与门组成的Moore型同步时序逻辑电路,分析如下。

(1)根据逻辑图写出每个触发器的驱动方程和输出方程。

(2)将驱动方程代入触发器的特征方程求得触发器的状态方程。

(3)列出状态转换表,画出状态转换图与时序波形图。

根据状态方程和输出方程,可以列出状态表,如表11.2.1所示。

表11.2.1 例11.2.1的状态表

由此状态表可以得到:

① 状态图,如图11.2.2所示。

图11.2.2 例11.2.1的状态图

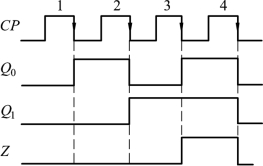

② 时序图,如图11.2.3所示。(https://www.xing528.com)

图11.2.3 例11.2.1的时序图

(4)确定电路的逻辑功能。

由状态图和时序图可知,此电路是一个同步四进制加法计数器,Z为进位输出端。

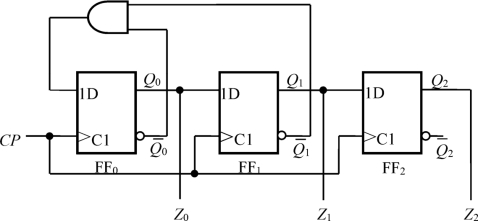

例11.2.2 试分析如图11.2.4所示电路的逻辑功能。

图11.2.4 例11.2.2的逻辑电路图

解:

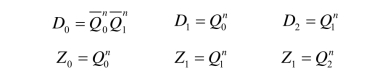

(1)根据逻辑图写出每个触发器的驱动方程和输出方程。

(2)将驱动方程代入触发器的特征方程求得触发器的状态方程。

![]()

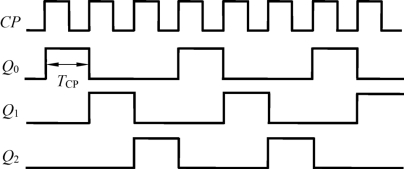

(3)列出状态转换表(表11.2.2),画出状态转换图(图11.2.5)与时序波形图(图11.2.6)。

表11.2.2 例11.2.2的状态表

续表

图11.2.5 例11.2.2的状态图

图11.2.6 例11.2.2的时序图

(4)确定电路的逻辑功能。

由状态图可见,电路的有效状态是三位循环码。从时序图可看出,电路正常工作时,各触发器的Q端轮流出现一个宽度为一个CP周期脉冲信号,循环周期为3 TCP。电路的功能为脉冲分配器或节拍脉冲产生器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。