时序逻辑电路的分析,就是对于一个给定的时序逻辑电路,研究在一系列输入信号作用下,电路将会产生怎样的输出,进而说明该电路的逻辑功能。

(1)同步时序逻辑电路分析

同步时序电路分析的一般步骤:

1)从给定的逻辑电路图中写出各触发器的驱动方程(即每一触发器输入控制端的函数表达式,有的书也称其为激励方程)。

2)将驱动方程代入相应触发器的特性方程,得到各触发器的状态方程(又称为次态方程),从而得到由这些状态方程组成的整个时序电路的状态方程组。

3)根据逻辑电路图写出输出方程。

4)根据状态方程、输出方程列出电路的状态表,画出状态图。

5)对电路可用文字概括其功能,也可做出时序图或波形图。

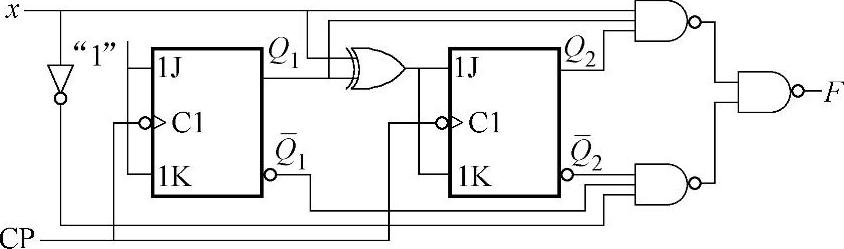

例3-9 分析如图3-51所示时序逻辑电路。

解:该时序电路由2个JK触发器和门电路构成,为同步时序电路,因此时钟脉冲CP方程可以省略。

①由给定电路图写出驱动方程

图3-51 例3-9的时序逻辑电路

驱动方程:

②将驱动方程代入相应触发器的特性方程,求各触发器的状态方程

③根据逻辑电路图写出输出方程为:

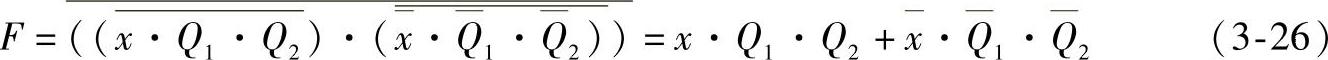

④为便于画出电路的状态图,由状态方程和输出方程列出状态表,如表3-11所示。

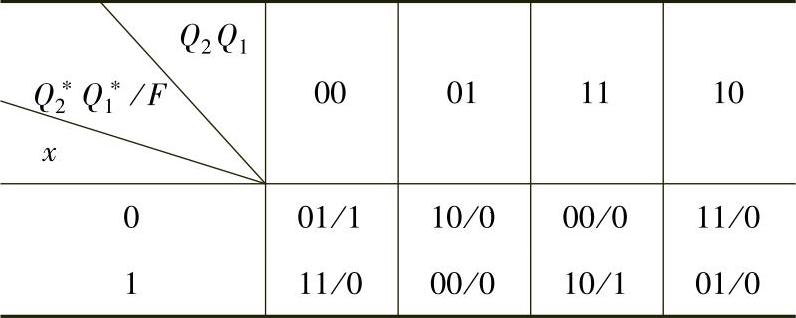

根据表3-11可以画出对应的状态图,如图3-52所示。

表3-11 例3-9电路的状态表

图3-52 例3-9电路的状态图

⑤由状态图可看出,该时序电路是一个模4的可逆计数器。当x=0时,实现模4加法计数,在时钟脉冲CP作用下,Q2Q1从00到11递增又返回00,每经过4个时钟脉冲后,电路的状态循环一次。同时在输出端F输出一个进位脉冲。当x=1时,电路进行减1计数,实现模4减法计数器功能,F是借位输出信号。

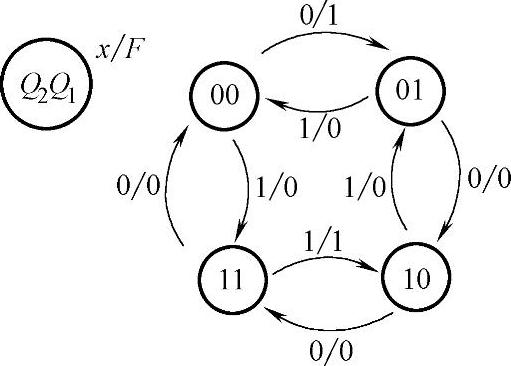

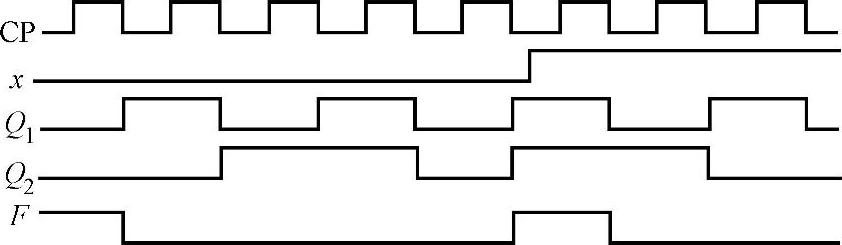

图3-53 例3-9电路的时序波形图

电路的时序波形如图3-53所示。

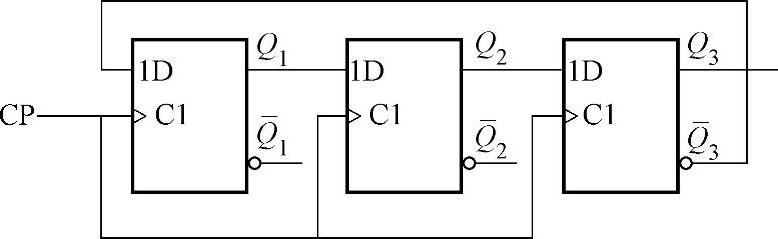

图3-54 例3-10的时序逻辑电路

例3-10 时序电路如图3-54所示,试分析其功能。

解:该电路为同步时序电路。电路的驱动方程为: ;D2=Q1;D3=Q2 (3-27)

;D2=Q1;D3=Q2 (3-27)

状态方程为: ;Q∗2=Q1;Q∗3=Q2 (3-28)

;Q∗2=Q1;Q∗3=Q2 (3-28)

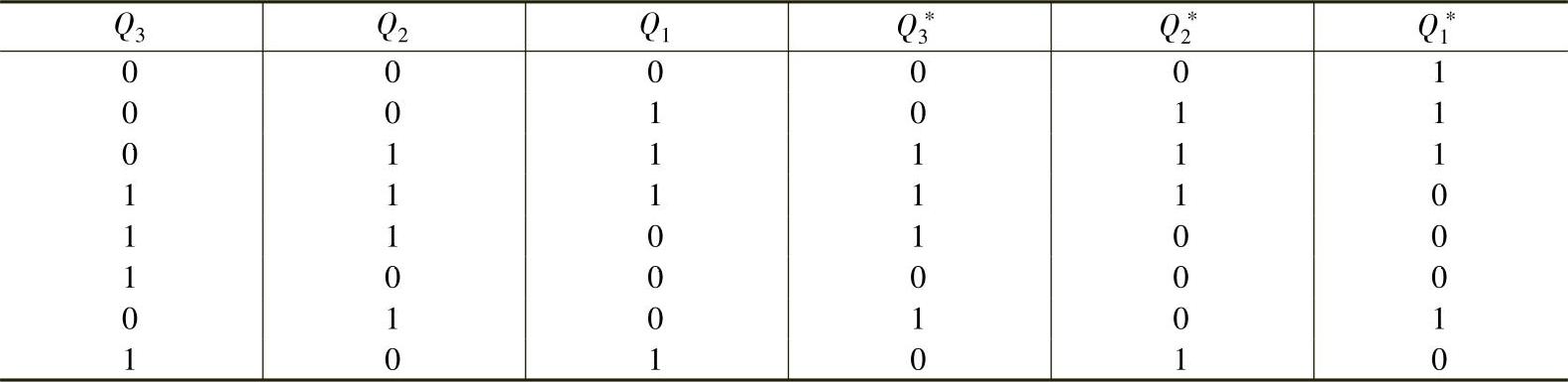

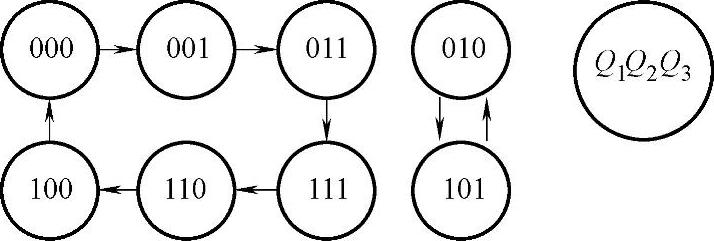

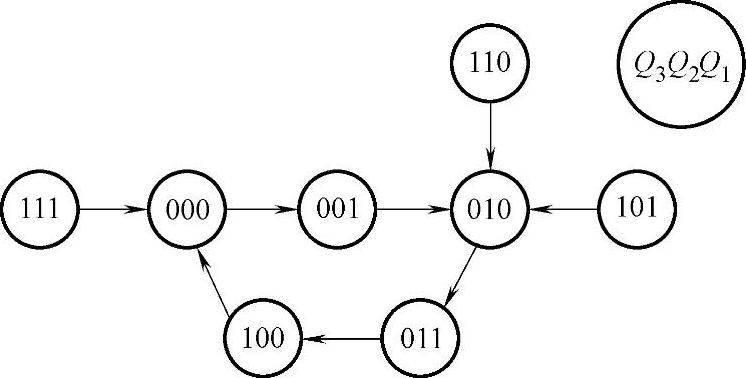

设电路的初始状态为Q3Q2Q1=000,代入式3-27和式3-28求出电路的次态Q∗3Q∗2Q∗1=001,将这一结果作为新的现态,按同样方法代入式3-27和式3-28求得电路新的次态,如此继续下去,直至次态Q∗3Q∗2Q∗1=000,返回了最初设定的初始状态为止。最后检查状态表是否包含了电路所有可能出现的状态。检查结果发现根据上述计算过程列出的状态表中只有6种状态,缺少Q3Q2Q1=010和Q3Q2Q1=101两个状态。将这两个状态代入式3-27和式3-28计算,将计算结果补充到状态表中,得到完整的状态表,如表3-12所示。画出电路状态图,如图3-55所示。(https://www.xing528.com)

表3-12 例3-10电路的状态表

由状态图可以看出,若电路进入Q3Q2Q1=010或Q3Q2Q1=101的状态时,它们自身成为一个无效的计数序列,经过若干节拍后无法自动返回正常计数序列,须通过复位才能正常工作,这种情况称电路无自启动能力。该电路为六进制计数器,又称为六分频电路。所谓分频电路是将输入的高频信号变为低频信号输出的电路。六分频是指输出信号的频率为输入信号频率的六分之一,即:

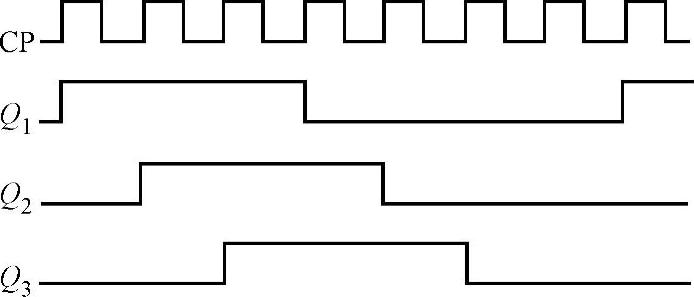

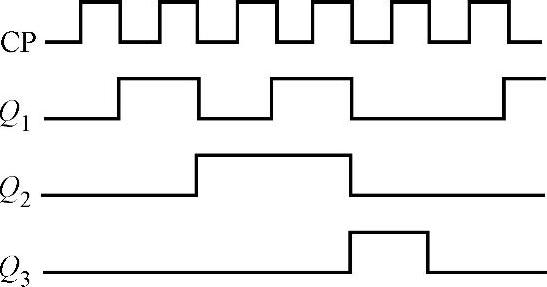

其时序波形如图3-56所示。

图3-55 例3-10电路的状态图

图3-56 例3-10电路的时序波形图

(2)异步时序逻辑电路分析

异步时序电路的分析方法和同步时序电路的分析方法有所不同。在异步时序电路中,不同触发器的时钟脉冲不相同,触发器只有在它自己的CP脉冲的相应边沿才动作,而没有时钟信号的触发器将保持原来的状态不变。因此异步时序电路的分析应写出每一级的时钟方程,具体分析过程比同步时序电路复杂。

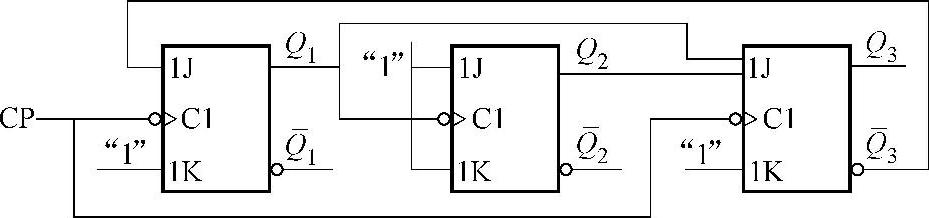

例3-11 已知异步时序电路的逻辑图如图3-57所示,试分析其功能。

解:由图可知,电路无输入控制变量,输出则是各级触发器状态变量的组合。第一级和第三级触发器公用一个外部时钟脉冲;第二级触发器的时钟由第一级触发器的输出提供,因此电路为穆尔型异步时序电路。

图3-57 例3-11的异步时序逻辑电路

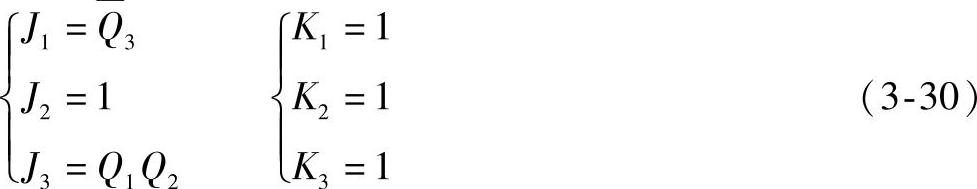

各触发器的驱动方程

列出电路的状态方程和时钟方程

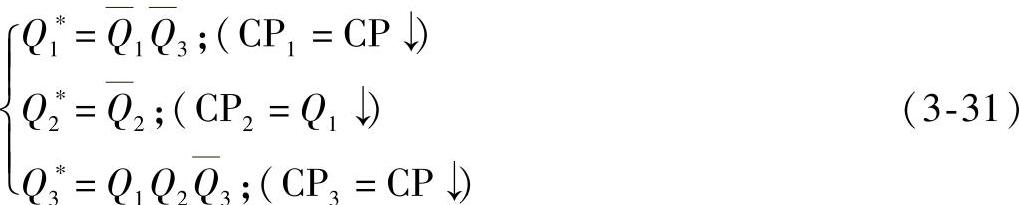

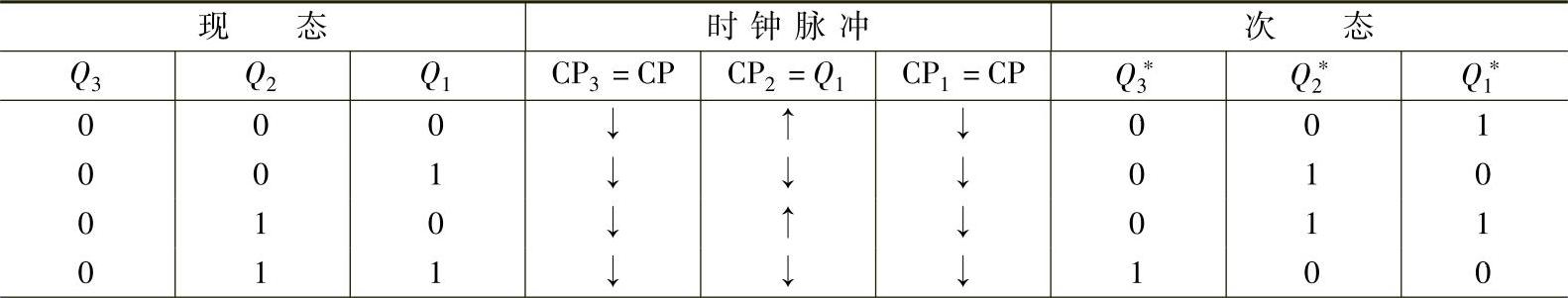

状态方程式3-31仅在括号内触发器时钟下降沿才成立,其余时刻均处于保持状态。在列写状态表时,须注意找出每次电路状态转换时各个触发器是否有式3-31括号内写入量的下降沿,再计算各触发器的次态。

当电路现态Q3Q2Q1=000时,代入Q1和Q3的次态方程,可得在CP作用下Q∗1=1,Q∗3=0,此时Q1由0→1产生一个上升沿,用符号↑表示,而CP2=Q1,因此Q2处于保持状态,即Q∗2=Q2=0。电路次态为001。

当电路现态为001时,Q∗1=0,Q∗3=0,此时Q1由1→0产生一个下降沿,用符号↓表示,Q2翻转,即Q2由0→1,电路次态为010,依此类推,列出电路状态表如表3-13所示。

表3-13 例3-11电路的状态表

(续)

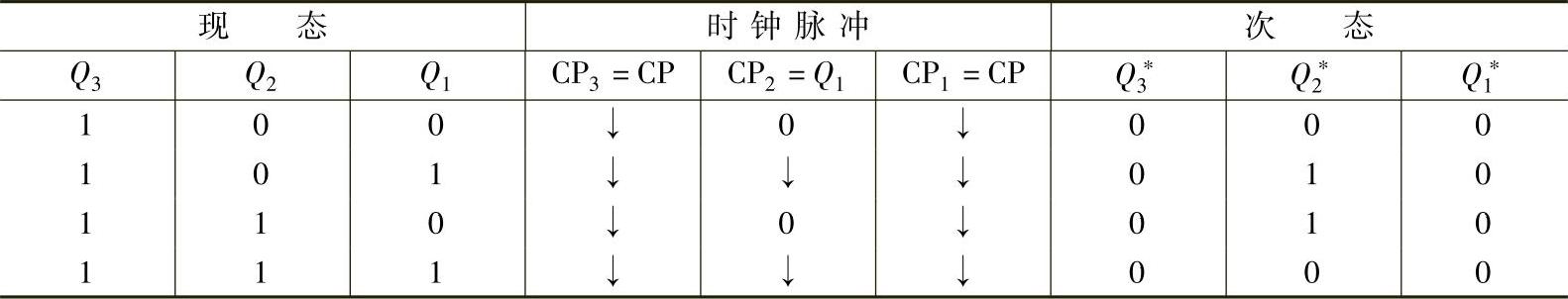

根据状态表画出状态图,如图3-58所示。该电路是异步3位五进制加法计数器,且具有自启动能力。

该电路时序波形如图3-59所示。

图3-58 例3-11电路的状态图

图3-59 例3-11电路的时序波形图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。