寄存器用于存储数据,它是由一组具有存储功能的触发器构成的。一个触发器可以存储1位二进制数,要存储n位二进制数需要n个触发器。无论是电平触发的触发器还是边沿触发的触发器都可以组成寄存器。

按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两类。基本寄存器只能并行送入数据,需要时也只能并行输出。移位寄存器具有数据移位功能,在一位脉冲作用下,存储在寄存器中的数据可以依次逐位右移或左移。数据输入输出方式有并行输入并行输出、串行输入串行输出、并行输入串行输出、串行输入并行输出四种。

移位寄存器不仅具有存储功能,而且存储的数据能够在时钟脉冲控制下逐位左移或者右移。根据移位方式的不同,移位寄存器分为单向移位寄存器和双向移位寄存器两大类。

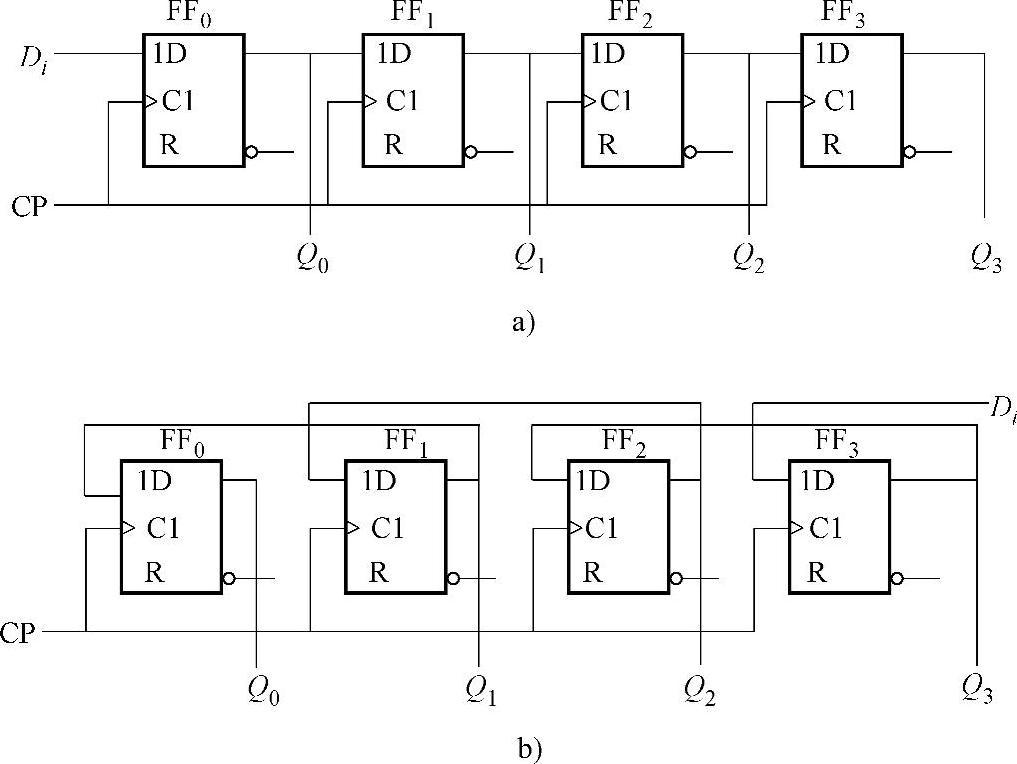

(1)单向移位寄存器

单向移位寄存器分为左移寄存器和右移寄存器,如图3-72所示。以图3-72a中的右移寄存器为例,当CP上升沿到来,串行输入端Di送数据入FF0中,FF1~FF3接受各自左边触发器的状态,即FF0~FF2的数据依次向右移动一位。经过4个时钟信号作用,4个数据被串行送入到寄存器的4个触发器中,此后可从Q0~Q3获得4位并行输出,实现串并转换。再经过4个时钟信号的作用,存储在FF0~FF3的数据依次从串行输出端Q3移出,实现并串转换。

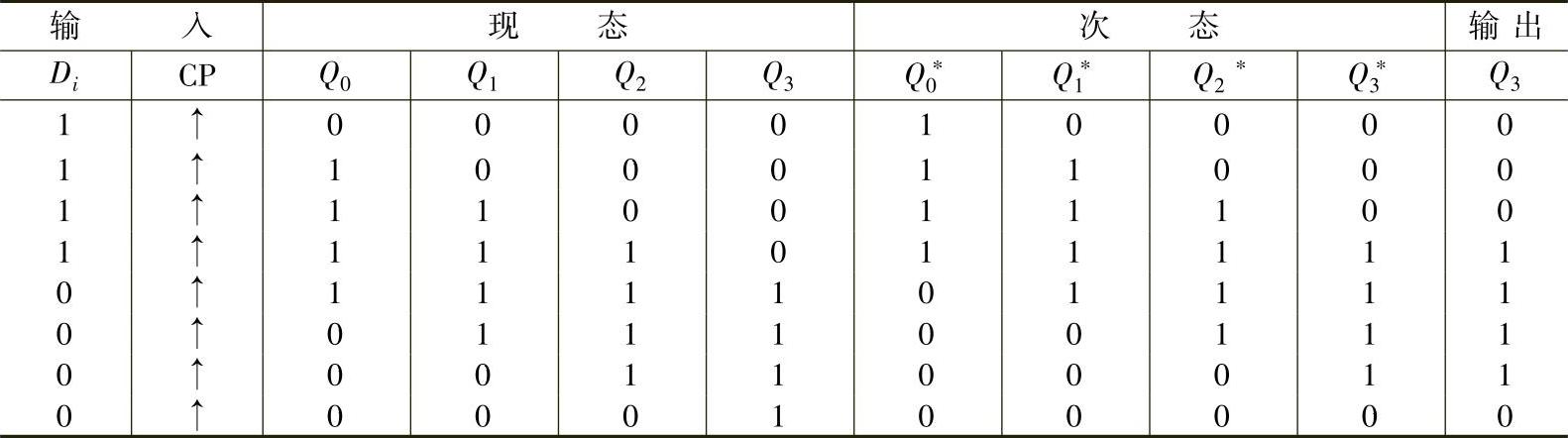

如表3-26所示,在4个时钟周期内依次输入4个1,经过4个CP脉冲,寄存器变成全1状态,再经过4个时钟脉冲连续输入4个0,寄存器被清零。

图3-72 单向移位寄存器

a)右移寄存器 b)左移寄存器

表3-26 4位右移寄存器的状态表

单向移位寄存器的特点:在时钟脉冲CP的作用下,单向移位寄存器中的数据可以依次左移或右移;n位单向移位寄存器可以寄存n位二进制代码。n个CP脉冲即可完成串行输入工作,并从Q0~Qn-1并行输出端获得n位二进制代码,再经n个CP脉冲即可实现串行输出工作;若串行输入端连续输入n个0,在n个CP脉冲周期后,寄存器被清零。

(2)双向移位寄存器

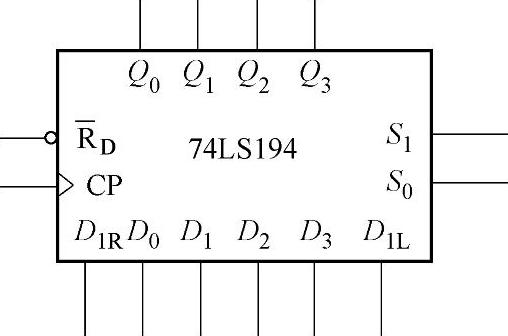

在单向移位寄存器的基础上,把右移寄存器和左移寄存器组合起来,加上移位方向控制信号和控制电路,即可构成双向移位寄存器。74LS194为常用的中规模集成芯片,它除了具有左移、右移功能之外,还具有并行数据输入和在时钟信号到达时保持原来状态不变等功能。

74LS194是由4个RS触发器和一些门电路所构成,每个触发器的输入都是由一个四选一数据选择器给出的。其逻辑符号如图3-73所示。(https://www.xing528.com)

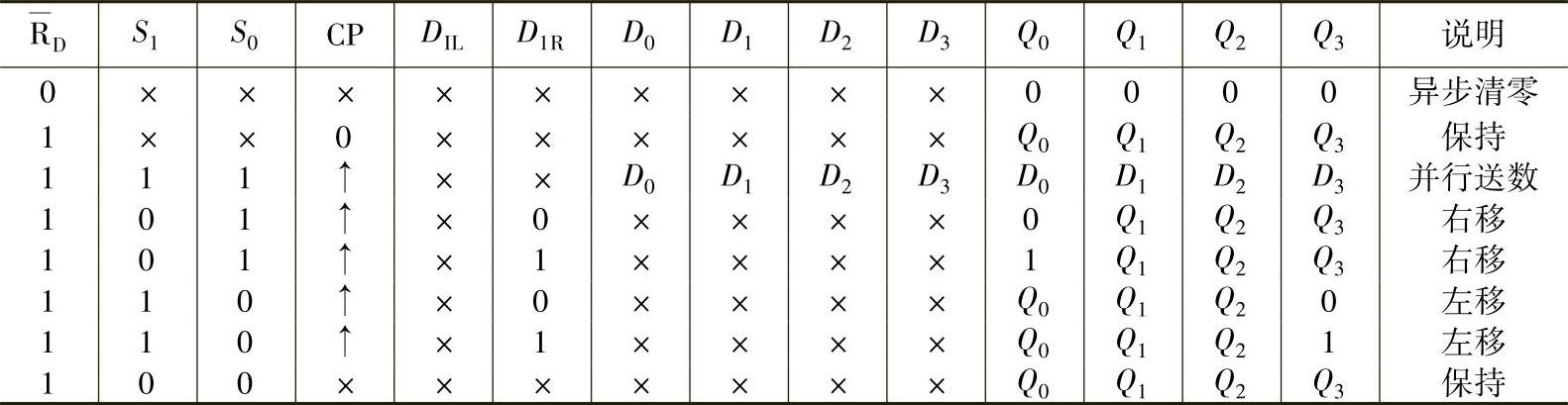

其中D0~D3是并行数据输入端,Q0~Q3是并行数据输出端,D1R是右移串行数据输入端,DIL是左移串行数据输入端, 是异步清零端,低电平有效。S1、S0是工作方式选择端,其选择功能是:S1S0=00为状态保持,S1S0=01为右移,S1S0=10为左移,S1S0=11为并行送数。可列出74LS194的功能表,如表3-27所示。

是异步清零端,低电平有效。S1、S0是工作方式选择端,其选择功能是:S1S0=00为状态保持,S1S0=01为右移,S1S0=10为左移,S1S0=11为并行送数。可列出74LS194的功能表,如表3-27所示。

图3-73 4位双向移位寄存器74LS194

表3-27 双向移位寄存器74LS194的功能表

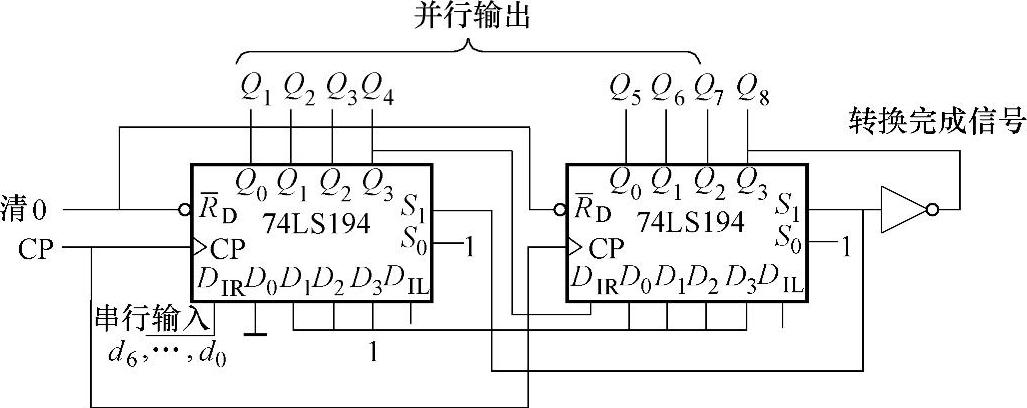

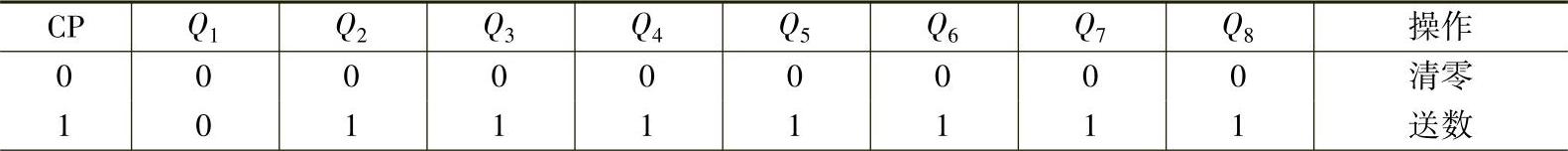

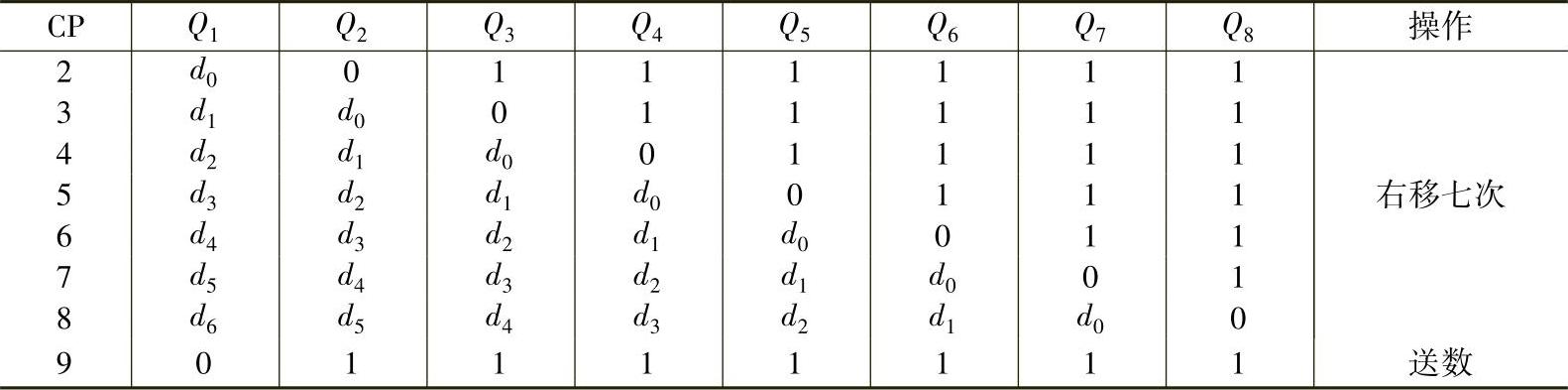

例3-18 用74LS194组成将串行输入转换为并行输出的电路。

解:转换电路如图3-74所示,其转换过程参见表3-28。具体过程:串行数据d6,…,d0从DIR端输入(d0先入),并行数据从Q1~Q7输出,表示转换结束的标志码0加在第1片的D0端,其它并行输入端接1。清0信号启动后,Q8=0,因此,第1个CP脉冲使74LS194完成预置操作,将并行输入的数据01111111送入Q1~Q8。此时由于Q8=1,S1S0=01,故以后的CP脉冲均实现右移操作,经过七次右移后,七位串行码全部移入寄存器。此时Q8=0,表示转换结束,从寄存器读出并行数据Q1~Q7=d6~d0。由于Q8=0,S1S0再次等于11,第9个CP脉冲到来使移位寄存器置数,并重复上述过程。

图3-74 例3-18的逻辑电路图

表3-28 例3-18状态表

(续)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。