用户可开发的PCI总线的外设,基本采用带PCI总线桥路协议的接口芯片。INTEL及其他芯片厂家提供很多接口芯片,较常见的芯片为AMCC公司的S593X系列,资料丰富,应用广泛。

AMCC公司的S593X系列PCI接口芯片提供多种接口操作方式,一般仪器设计者大多熟悉ISA总线设计,在此,介绍采用S5933芯片的直通方式设计的PCI总线采集卡。

S5933是通用PCI接口芯片,提供PCI总线主机同外设接口的单数据和突发数据两种传送。而且,具有直通读写功能,即将PCI总线时序转换为ISA总线时序,直接同外接逻辑进行数据传送,直通方式功能是S5933与PCI总线连接的简单通道,使用相应的握手协议和附加逻辑,PCI总线可以直接使用外加接口上的资源,方便用于A/D采集卡设计。

S5933为用户提供了四个直通方式地址范围。每一个范围与PCI配置基地址寄存器BADR1~BADR4对应。一个范围代表一个地址块,块的大小由用户定义。每一个地址块可以映像到存储空间,也可以映像到I/O空间。如果映像到存储空间,还可以映像到低于1MB的范围内,即Intel的实模式地址。总线宽度也是可以配置,即8位、16位或32位,以适应不同总线宽度的外加存储器和外设。

为了实现PCI总线对外加接口资源的直接访问,S5933内部有一个直通方式地址寄存器(APTA)和一个直通方式数据寄存器(APTD),这两个寄存器连接于PCI总线接口和外加接口之间,允许一个PCI主设备执行一个直通方式写(从PCI总线传送数据到外加接口)或者直通方式读(从外加接口接收数据到PCI总线)。S5933支持单数据节拍和突发数据两种传送模式。

1.S5933芯片的直通方式总线操作

在直通方式下,PCI与外加接口之间传送数据使用以下握手机制:当PCI总线写一个数据到S5933的地址范围,外加接口的逻辑必须从S5933中读取这个数据,并存储在外加接口中。如果PCI总线从S5933的直通方式地址范围中读取一个数据,外加接口必须先将这个数据存放S5933中的数据寄存器中。

如果从PCI总线写数据到外加接口,当TRDY有效时,S5933从PCI总线上获取数据,并将该数据传送到S5933的APTD寄存器。同时,S5933设置相应的状态信号,以表示数据寄存器满。这时,外加接口可以使用PTRDY信号读取该寄存器的内容,表示当前的数据传送已经完成。对于从外加接口上读取数据操作,S5933先设置直通方式状态位,以表示PCI需要从外加接口上获取数据,此时,外加接口逻辑应该将数据写入S5933的直通方式数据寄存器,并且使PTRDY有效,S5933接收到该信号后,将TRDY置为有效,PCI总线主设备读取该数据,完成该数据的传送。如果外加接口逻辑在规定的时间内不能提供数据,S5933将重置,允许PCI总线执行其他的任务。

2.S5933同PCI总线接口

当S5933作为从设备接口时,才具有直通方式功能。它允许PCI主设备读写外加接口上的资源,这种读写可以是单数据节拍,也可以是多数据节拍突发方式。外加接口必须提供完成直通方式操作所需的控制信号和状态信号。

S5933译码所有的PCI总线周期的地址,如果当前地址为S5933所定义的地址范围内,它将设 (PCI总线信号)信号有效。如果直通方式逻辑处于空闲状态,S5933将译码总线周期类型,并设置直通方式的状态信号,初始化外加逻辑。

(PCI总线信号)信号有效。如果直通方式逻辑处于空闲状态,S5933将译码总线周期类型,并设置直通方式的状态信号,初始化外加逻辑。

(1)PCI直通方式单周期访问 单周期传送是最简单的PCI总线传送方式,它由一个地址节拍和一个数据节拍组成。当一个主设备将地址和命令传送到PCI总线,同时使 信号有效时,标志一个PCI总线传送开始。主设备总是在最后一个数据节拍使

信号有效时,标志一个PCI总线传送开始。主设备总是在最后一个数据节拍使 信号无效。对于单周期传送,

信号无效。对于单周期传送, 只在地址节拍内有效。

只在地址节拍内有效。

当S5933检测到 信号有效时,采样总线上的地址和命令信息,如果地址在S5933定义的地址范围内,S5933将接受本次访问(设置DEVSEL有效),并将PCI地址存入S5933内部的直通方式地址寄存器(APTA)。

信号有效时,采样总线上的地址和命令信息,如果地址在S5933定义的地址范围内,S5933将接受本次访问(设置DEVSEL有效),并将PCI地址存入S5933内部的直通方式地址寄存器(APTA)。

对于直通方式写操作,S5933立即响应主设备请求(置 有效),将数据传送到S5933内部直通方式数据寄存器中。然后,S5933通知外加接口直通方式操作已经发生,等待外加接口从数据寄存器中读取数据,完成数据传送(置

有效),将数据传送到S5933内部直通方式数据寄存器中。然后,S5933通知外加接口直通方式操作已经发生,等待外加接口从数据寄存器中读取数据,完成数据传送(置 有效)。一旦S5933从PCI总线获取数据,S5933与PCI总线的传送就宣告结束,PCI总线可以立即被其他操作利用。

有效)。一旦S5933从PCI总线获取数据,S5933与PCI总线的传送就宣告结束,PCI总线可以立即被其他操作利用。

对于直通方式读操作,S5933通知外加接口直通方式读操作正在进行,等待外加逻辑将数据写到S5933数据寄存器(APTD),当数据写入后,外加逻辑置 有效。如外加逻辑不能及时地将数据写入数据寄存器APTD,S5933将向主设备请求重置。

有效。如外加逻辑不能及时地将数据写入数据寄存器APTD,S5933将向主设备请求重置。

(2)PCI直通方式突发访问 对于PCI直通方式访问,S5933在获取PCI地址后,确认该地址是否是在其直通方式地址范围内。如果在定义的范围内,则S5933将把自己的 置为有效,以表示接受主设备的访问,同时监测PCI总线的

置为有效,以表示接受主设备的访问,同时监测PCI总线的 和

和 信号,确认突发访问。

信号,确认突发访问。

对于直通方式写,S5933将立即用T 有效做出响应。S5933将直通方式的第一个数据节拍的数据存入直通方式数据寄存器(APTD),外加接口置

有效做出响应。S5933将直通方式的第一个数据节拍的数据存入直通方式数据寄存器(APTD),外加接口置 有效,完成数据的传送。在每一个数据节拍,由外加逻辑驱动

有效,完成数据的传送。在每一个数据节拍,由外加逻辑驱动 。S5933在每一个数据节拍的开始时使T

。S5933在每一个数据节拍的开始时使T 有效,在下一个数据节拍将该数据存入数据寄存器。对于突发访问,APTA的内容将自动增加,以寻址下一个单元。

有效,在下一个数据节拍将该数据存入数据寄存器。对于突发访问,APTA的内容将自动增加,以寻址下一个单元。

对于突发读,S5933设置 有效,将主设备的数据请求传递到外加逻辑,并且将主设备提供的地址信号存入APTA寄存器,外加接口根据主设备的请求将数据传送到S5933的数据寄存器,同时使

有效,将主设备的数据请求传递到外加逻辑,并且将主设备提供的地址信号存入APTA寄存器,外加接口根据主设备的请求将数据传送到S5933的数据寄存器,同时使 有效,S5933将数据传送到PCI总线,并设置

有效,S5933将数据传送到PCI总线,并设置 有效,启动下一个数据阶段。在每一个数据节拍,S5933中的地址寄存器内容将自动增加,指向下一个数据。(https://www.xing528.com)

有效,启动下一个数据阶段。在每一个数据节拍,S5933中的地址寄存器内容将自动增加,指向下一个数据。(https://www.xing528.com)

(3)PCI重置条件 在一些场合,外加逻辑不能及时地响应直通方式访问,S5933将撤销与PCI的连接,进入重置状态。当从设备准备好,主设备将重新进入访问。这样,在进入重置状态期间,允许其他设备使用总线,提高了系统的效率。

对于许多设备,特别是存储器,第一次访问要比以后的访问花费更多时钟周期,在这种情况下,PCI最多允许在第一个数据节拍中插入16个PCI周期,在以后的数据节拍最多中插入8个PCI时钟周期。

如果一个主设备试图在直通方式地址范围的结尾处突发传送,S5933也将请求重置。在突发传送的每一个数据节拍,S5933将更新直通方式地址寄存器(APTA),如果更新的地址不在直通方式地址范围内,将请求重置。

(4)PCI写重置 当S5933请求一个写重置,表示外加接口正处于忙状态,不能响应当前的写请求。直通方式地址和数据寄存器仍然保持以前内容,一直到传送完成(外加接口保持 有效)。

有效)。

当外加接口忙于完成直通方式写,S5933请求立即进入重置状态,允许PCI执行其他操作,外加电路执行直通方式操作时,可以访问PCI操作寄存器。

(5)PCI读重置 当S5933为PCI直通方式读请求重置时,表示外加电路不能在规定的时间内完成读操作。如果外加接口在完成直通方式操作并将数据写入直通方式数据寄存器后发生重置,S5933将设置 和

和 以完成从S5933到PCI的读操作。如果外加接口没有完成读操作,S5933将最多等待16个PCI时钟周期,如果外加接口在该时钟周期内仍不能完成读操作,将产生另一个重置请求。

以完成从S5933到PCI的读操作。如果外加接口没有完成读操作,S5933将最多等待16个PCI时钟周期,如果外加接口在该时钟周期内仍不能完成读操作,将产生另一个重置请求。

3.S5933同外设接口逻辑

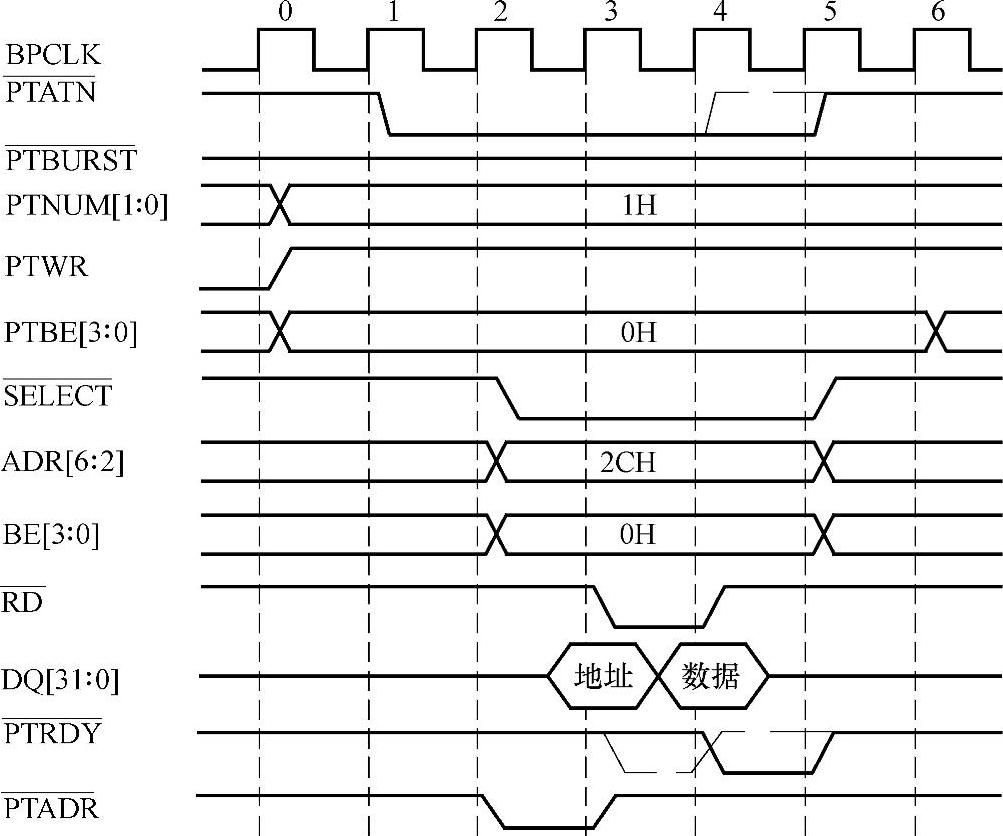

(1)单周期写 当PCI主设备仅写一个数据到直通方式地址范围内,单周期直通方式写操作的时序图如图4-36所示,将发生单周期直通方式写操作。单周期传送由一个地址节拍和一个数据节拍组成,在地址节拍,S5933将PCI地址存入直通方式地址寄存器(AP-TA),如果S5933检测到该地址是在它所定义的范围内,就将数据存入直通方式数据寄存器(APTD),外设接口逻辑再从数据寄存器(ATPD)中读取该数据,并将它传送到目的地。

图4-36 单周期直通方式写操作的时序图

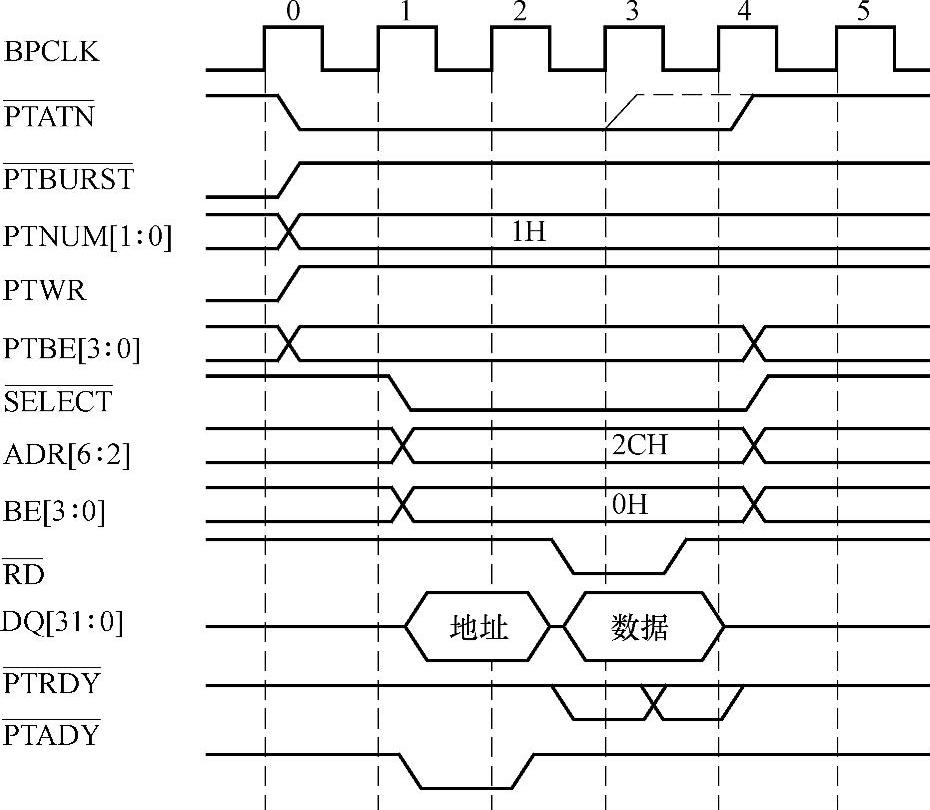

(2)单周期读 当PCI主设备从S5933直通方式地址范围内读一个数据到PCI总线如图4-37所示,将发生单周期直通方式读操作。单周期读操作由一个地址节拍和一个数据节拍组成,在地址节拍,S5933将PCI地址存入直通方式地址寄存器(APTA),如果该地址是在S5933检测到它所定义的范围内,外设逻辑就将指定单元的数据存入直通方式数据寄存器(APTD),等待PCI总线读取。

图4-37 单周期直通方式读操作的时序图

4.PCI总线数据采集卡设计

采用AMCC公司的PCI接口芯片S5933设计接口卡,PCI数据采集卡的原理图如图4-38所示。该设计采用S5933的直通方式,外接可编程逻辑芯片(P22V10)实现外接逻辑,提供S5933对外接口读写操作的必要时序,该接口提供类似ISA总线的地址信号、I/O读写信号、存储器读写控制信号,以及等待周期产生逻辑和总线控制逻辑。

芯片PLD1为S5933芯片的主控芯片,控制S5933插入等待周期、控制总线、产生准备好信号等。PLD2芯片为外接芯片或接口提供地址选择信号。其中WR和RD等同ISA总线的IOW和IOR,接口使能由PTNUM0[1:0]译码确定。DQ[31:0]为32位数据线,SA[17:0]为18位地址线。对SA[17:0]进行译码,作为A/D芯片的片选信号。

选用AD公司新一代高性能A/D芯片ADC7892,ADC7892为12位高速A/D芯片,片内含有基准源和内时钟,可并行输出12位转换结果。转换采用连续启动工作方式,将A/D转换结束信号接入启动A/D转换端,上电后,自动启动A/D转换,数据的读取采用查询或默认方式,查询方式将A/D转换结束信号EOC接到数据线的第16位,低11位接A/D转换结果输出。读入A/D结果,判断EOC可知转换结果,如为有效数字,则存入RAM;否则,继续查询或等待。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。