1.常用CPLD的简介

CPLD/FPGA的生产厂家较多,其名称又不规范一致,因此,在使用前必须加以详细了解。本节主要介绍几个主要厂家的典型产品,包括系列、品种、性能指标。这些公司的详细产品介绍可登录其公司网站查看,如Lattice公司的中文网站

http://www.latticesemi.com.cn/

(1)Lattice公司CPLD器件系列

Lattice公司始建于1983年,是最早推出PLD的公司之一,GAL器件是其成功推出并得到广泛应用的PLD产品。20世纪80年代末,Lattice公司提出了在系统可编程的概念,并首次推出了CPLD,其后,将ISP与其拥有的先进的EECMOS技术相结合,推出了一系列具有ISP功能的CPLD,使CPLD的应用领域又有了巨大的扩展。所谓ISP技术,就是不用从系统上取下PLD芯片,就可进行编程的技术。ISP技术大大缩短了新产品研制周期,降低了开发风险和成本。因而推出后得到了广泛的应用,几乎成了CPLD的标准。

Lattice公司的CPLD主要有ispLSI系列、ispMACH系列。

下面介绍常用的ispLSI/MACH系列。

ispLSI系列是Lattice公司于20世纪90年代以来推出的,集成度1000~60000门,引脚到引脚之间(PinToPin)延时最小3ns,工作速度可达300MHz,支持ISP和JTAG边界扫描测试功能,适宜于通信设备、计算机、DSP系统和仪器仪表中应用;ispLSI/MACH速度更快,可达400MHz。

ispLSI系列主要有6个系列,分别适用于不同场合,前3个系列是基本型,后3个系列是1996年后推出的新产品。

①ispLSI1000系列。ispLSI1000系列包括ispLSI1000/1000E/EA等品种,属于通用器件,集成度2000~8000门,引脚到引脚之间的延时不大于7.5ns,集成度较低,速度较慢,但价格便宜,如ispLSI1032E是目前市面上最便宜的CPLD之一,因而在一般的数字系统中使用较多,如网卡、高速编程器、游戏机、测试仪器仪表中均有应用。ispLSI1000是基本型,ispLSI1000E是ispLSI1000的增强型(Enhanced)。

②ispLSI2000系列。ispLSI2000系列包括ispLSI2000/2000A/2000E/2000V/2000VL/2000VE等品种,属于高速型器件,集成度与ispLSI1000系列大体相当,引脚到引脚之间延时最小3ns,适用于速度要求高、需要较多I/O引脚的电路,如移动通信、高速路由器等。

③ispLSI3000系列。ispLSI3000系列是第一个上万门的ispLSI系列产品,采用双GLB,集成度可达2万门,可单片集成系统逻辑、DSP功能及编码压缩电路。适用于集成度要求较高的场合。

以上系列工作电压为5V,引脚输入/输出电压为5V。

④ispLSI5000系列。ispLSI5000系列包括ispLSI5000V/5000VA等品种,其整体结构与ispLSI3000系列类似,但GLB和宏单元结构有了很大的差异,属于多I/O口宽乘积项型器件,集成度10000~25000门,引脚到引脚之间的延时大约5ns,集成度较高,工作速度可达200MHz,适用于宽总线(32位或64位)的数字系统,如快速计数器、状态机和地址译码器等。ispLSI5000V系列工作电压3.3V,但其引脚能够兼容5V、3.3V、2.5V等多种电压标准。

⑤ispLSI6000系列。ispLSI6000系列的GLB与ispLSI3000系列相同,但整体结构中包含了FIFO或RAM功能,是FIFO或RAM存储模块与可编程逻辑相结合的产物,集成度可达25000门。

⑥ispLSI8000系列。ispLSI8000系列包括ispLSI8000/8000V等品种,是在ispLSI5000V系列的基础上,更新整体结构而来的,属于高密度型器件,集成度可达60000门,引脚到引脚之间的延时大约5ns,集成度最高,工作速度可达200MHz,适用于较复杂的数字系统中应用。如外围控制器、运算协处理器等。

⑦ispMACH4000系列。ispMACH4000系列外观如图3-8所示,包括ispLSI4000/4000B/4000C/4000V/4000Z等品种,主要是供电电压不同,ispMACH4000V、ispM-ACH4000B和ispMACH4000C器件系列供电电压分别为3.3V、2.5V和1.8V,Lattice公司还基于ispMACH4000的器件结构开发出了业界最低静态功耗的CPLD系列——ispM-ACH4000Z。

ispMACH4000系列产品提供SuperFAST(400MHz,超快)的CPLD解决方案。ispM-ACH4000V和ispMACH4000Z均支持军用温度范围:-40~130℃。ispMACH4000系列支持介于3.3V和1.8V之间的I/O标准,既有业界领先的速度性能,又能提供最低的动态功耗。

ispMACH4000V/B/C系列器件的宏单元个数从32~512不等,ispMACH4000Z的宏单元数为32~256。ispMACH系列提供44~256引脚、具有多种密度I/O组合的TQFP、fpBGA和caBGA封装。

⑧ispLSI5000VE/ispMACH5000系列。ispLSI5000VE是后来设计的新产品,Lattice公司推荐用于替代ispLSI3000/5000V/5000VA。

ispLSI5000VE系列外观如图3-9所示。

图3-8 ispMACH4000系列外观图

图3-9 ispLSI5000VE系列外观图

ispLSI5000VE整体结构与ispLSI3000系列类似,但GLB和宏单元结构有了很大的差异,属于多I/O口宽乘积项型器件,引脚到引脚之间延时大约5ns,集成度最大1024个宏单元,工作速度可达180MHz,适用于宽总线(32位或64位)的数字系统中使用,如快速计数器、状态机和地址译码器等。ispMACH5000B系列速度更快,可达275MHz,集成度最大512个宏单元。

ispLSI/ispMACH5000系列器件的可编程结构为各种复杂的逻辑应用系统提供了业界领先的系统性能。器件的每个逻辑块拥有68个输入,可以在单级逻辑上轻松实现包括64位应用系统的复杂逻辑功能,而用传统的CPLD却需要两层或更多的逻辑层才能实现相同的功能,因为它们的逻辑块输入只相当于ispLSI/ispMACH5000器件的一半。所以,对于需要36个以上的输入的“宽”逻辑功能,ispLSI/ispMACH5000的性能表现比传统的CPLD结构高出60%。

⑨ispXPLDTM5000MX系列。ispXPLD5000MX系列外观如图3-10所示,包括ispXPLDTM5000MB/5000MC/5000MV等品种。(https://www.xing528.com)

ispXPLDTM5000MX系列代表了Lattice半导体公司全新的XPLD(eXpanded Programmable Logic De-vices)系列。这类器件采用了新的构建模块——多功能块(Multi-Function Block,MFB)。这些MFB可以根据用户的应用需要,被分别配置成SuperWIDETM超宽(136个输入)逻辑、单口或双口存储器、先入先出堆栈或CAM。

图3-10 ispXPLD5000MX系列外观图

ispXPLD 5000MX器件将PLD出色的灵活性与sysIOTM接口结合了起来,能够支持LVDS、HSTL和SSTL等最先进的接口标准以及比较熟悉的LVCMOS标准。sysCLOCKTM PLL电路简化了时钟管理。ispXPLD 5000MX器件采用拓展了的在系统编程技术,也就是ispXP技术,因而具有非易失性和无限可重构性。编程可以通过IEEE1532业界标准接口进行,配置可以通过Lattice的sysCONFIGTM微处理器接口进行。该系列器件有3.3V、2.5V和1.8V供电电压的产品可供选择(对应MV、MB和MC系列),最大规模1024个宏单元,最快300MHz。

ispLSI/MACH器件都采用EECMOS和EEPROM工艺结构,能够重复编程万次以上,内部带有升压电路,可在5V、3.3V逻辑电平下编程,编程电压和逻辑电压可保持一致,给使用带来很大方便;具有保密功能,可防止非法拷贝;具有短路保护功能,能够防止内部电路自锁和SCR自锁。推出后,受到了极大的欢迎,曾经代表了CPLD的最高水平,现在Lattice公司推出了新一代的扩展在系统可编程技术(ispX),在新设计中推荐采用ispMACH系列产品和ispLSI5000VE,全力打造ispXPLD,并推出采用扩展在系统可编程技术的ispXPGA系列FPGA器件,改变了只生产CPLD的状况。

(2)Xilinx公司的CPLD系列

Xilinx公司以其提出现场可编程的概念和1985年生产出世界上首片FPGA而著名,但其CPLD产品也很不错。

Xilinx公司的CPLD系列主要有XC7200系列、XC7300系列、XC9500系列。

下面介绍常用的XC9500系列。

XC9500系列有XC9500/9500XV/9500XL等品种,主要是芯核电压不同,分别为5V/2.5V/3.3V。

XC9500系列采用快闪(FastFlash)存储技术,能够重复编程万次以上,比ultraMOS工艺速度更快,功耗更低,引脚到引脚之间的延时最小4ns,宏单元数可达288个(6400门),系统时钟200MHz,支持PCI总线规范,支持ISP和JTAG边界扫描测试功能。

该系列器件的最大特点是引脚作为输入可以接受3.3V/2.5V/1.8V/1.5V等多种电压标准,作为输出可配置成3.3V/2.5V/1.8V等多种电压标准,工作电压低,适应范围广,功耗低,编程内容可保持20年。

(3)Altera公司的CPLD系列

Altera公司是著名的PLD生产厂家,它既不是FPGA的首创者,也不是CPLD的开拓者,但在这两个领域都有非常强的实力,多年来一直占据行业领先地位。其CPLD系列主要有FLASHlogic系列、Classic系列和MAX(Multiple Array Matrix)、MAXⅡ系列。

下面介绍常用的MAX系列。

MAX系列包括MAX3000/5000/7000/9000等品种,集成度在几百门至数万门之间,采用EPROM和EEPROM工艺,所有MAX7000/9000系列器件都支持ISP和JTAG边界扫描测试功能。

MAX7000宏单元数可达256个(12000门),价格便宜,使用方便。E、S系列工作电压为5V,A、AE系列工作电压为3.3V混合电压,B系列为2.5V混合电压。

MAX9000系列是MAX7000的有效宏单元和FLEX8000的高性能、可预测快速通道互连相结合的产物,具有6000~12000个可用门(12000~24000个有效门)。

MAX系列的最大特点是采用EEPROM工艺,编程电压与逻辑电压一致,编程界面与FPGA统一,简单方便,在低端应用领域有优势。

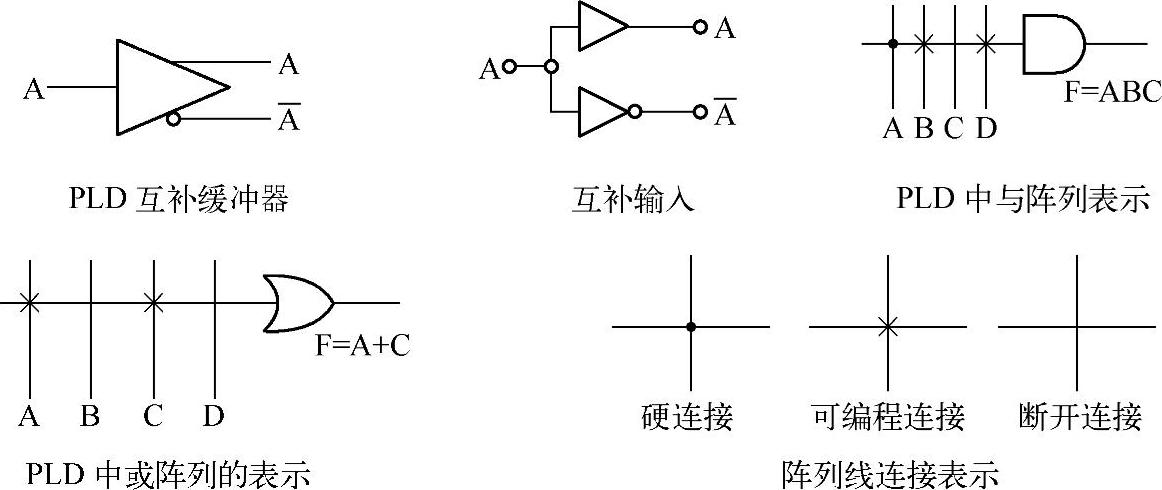

2.CPLD的基本结构

CPLD是采用乘积项结构的大规模可编程器件的统称,在结构上有许多的相似之处,但也有一定的差别。图3-11所示的是常用的各种内部结构图。下面介绍Altera公司的MAX系列CPLD基本结构和工作原理。

图3-11 各种内部结构图

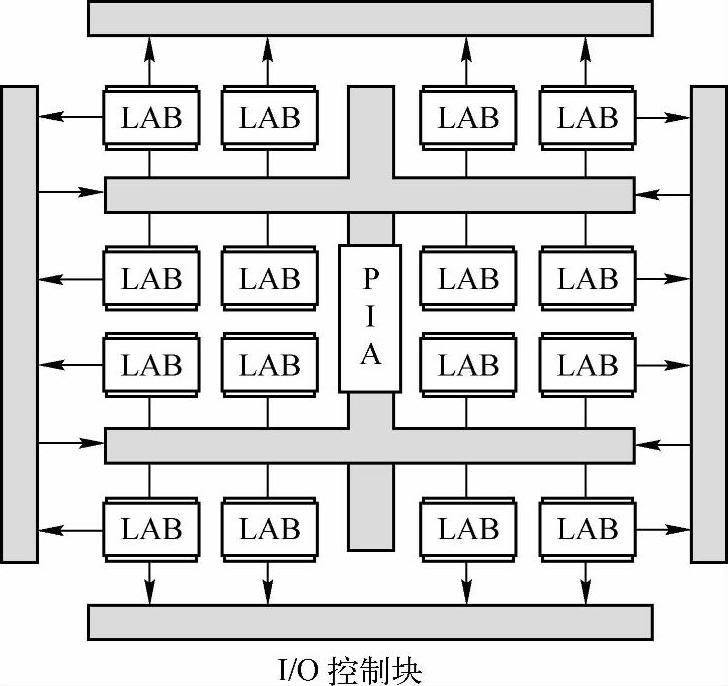

MAX7128S逻辑结构主要由4部分组成:逻辑阵列块(Logic Array Block,LAB)、扩展乘积项(eXtended Product Term,XPT)、可编程连线阵列(Programmable Interconnect Array,PIA)和I/O控制块,其内部结构如图3-12所示。

图3-12 MAX7128S的内部结构图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。