在对VHDL的设计实体结构有一定了解后,通过以下几个基本逻辑器件的VHDL描述示例,使读者对VHDL程序设计有初步的理解。

例4.6与非门的描述。

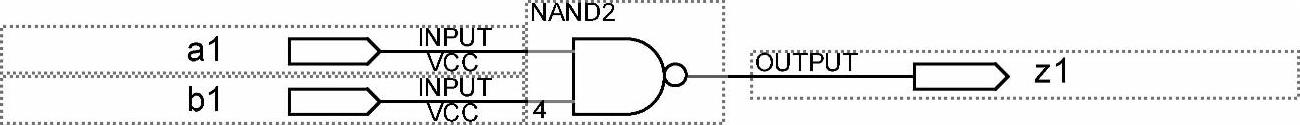

图4-3是根据VHDL端口规则画出的二输入与非门的逻辑符号,其中a1、b1是输入信号,z1是输出信号,输出与输入的逻辑关系表达式为

图4-3 与非门逻辑符号

在VHDL语法中,与非运算符号是“NAND”,赋值等号是“<=”,因此在VHDL程序中,式(4-1)应写为

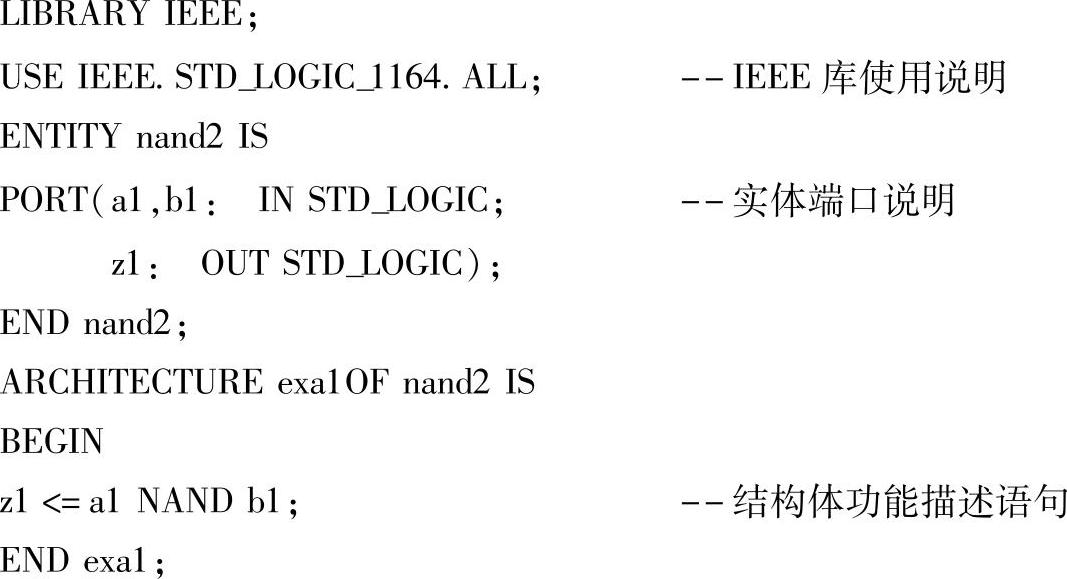

下面是按照VHDL语法规则写出来的与非门程序,它是一个完整、独立的语言模板,相当于电路中的一个“与非”器件或者电路原理图上的一个“与非”元件符号。它能够被VHDL综合器接受,形成一个独立存在和独立运行元件,也可以被高层次的系统调用,成为系统中的一部分。

程序的语句行后可以用“--”符号将语句的注释部分内容分隔,这是语法规则允许的。

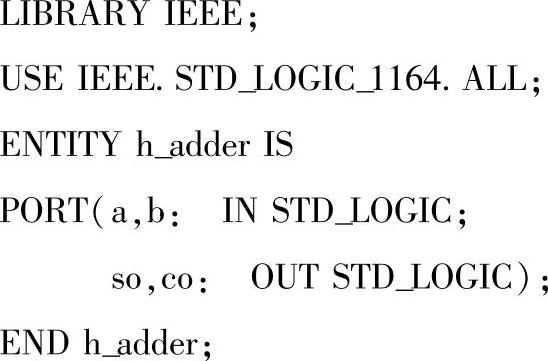

例4.7 半加器的描述。

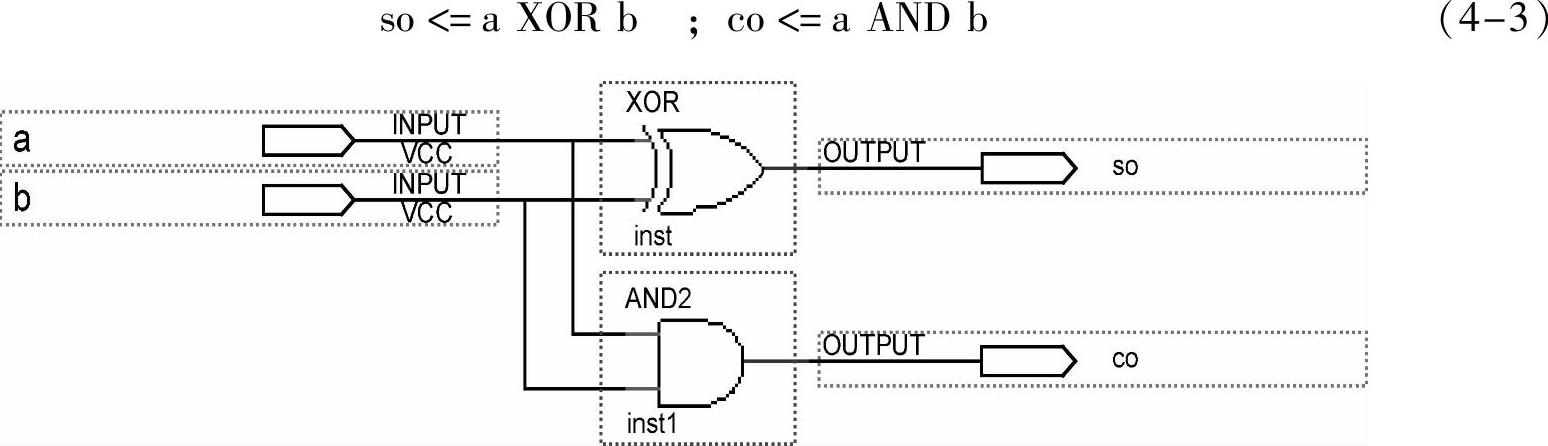

图4-4 半加器的逻辑图(https://www.xing528.com)

图4-4是半加器的逻辑图,其中a、b是输入信号,so、co是输出信号。用VHDL语法规则推导输出与输入信号之间的逻辑表达式为

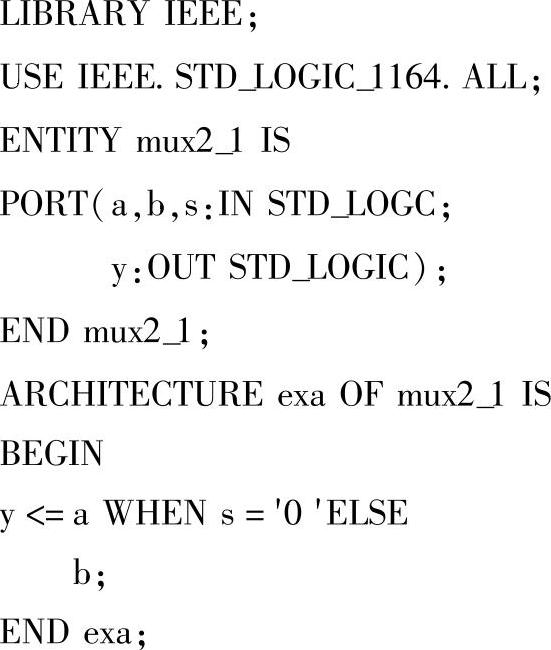

例4.82 选1数据选择器的描述。

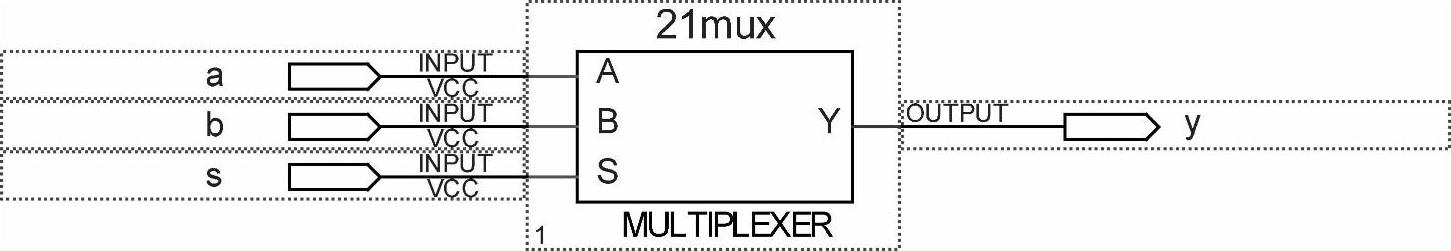

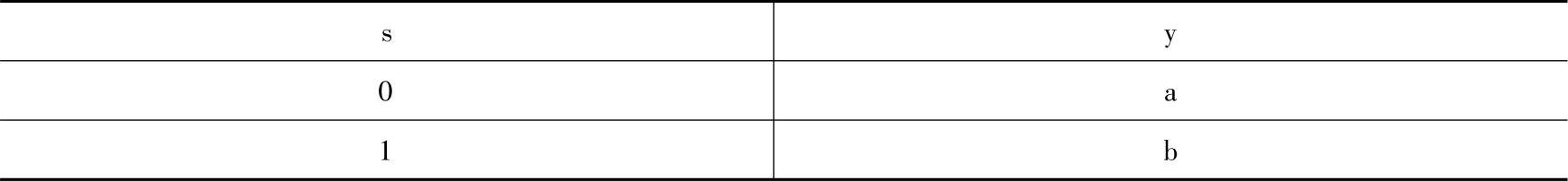

2选1数据选择器的逻辑符号如图4-5所示,其中,a、b是数据输入信号,s是控制输入信号,y是输出信号。2选1数据选择器的功能见表4-1。表中反映出数据选择器的功能是:如果s=0,则y=a;如果s=1,则y=b。用VHDL描述y与s、a、b之间的功能关系语句为

图4-52 选1数据选择器逻辑符号

表4-12 选1数据选择器功能表

这是VHDL另一个描述风格,称为行为描述。行为描述只描述所设计电路的功能或者说电路行为,而没有直接指向或涉及实现这些行为的硬件结构。完整的2选1数据选择器的VHDL描述为

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。