译码是编码的逆过程,它的功能是将具有特定含义的二进制代码转换成对应的输出信号,具有译码功能的逻辑电路称为译码器。通常根据译码器电路的逻辑功能和特点,将译码器分为二进制译码器、二-十进制译码器和7段显示译码器。

1.二进制译码器

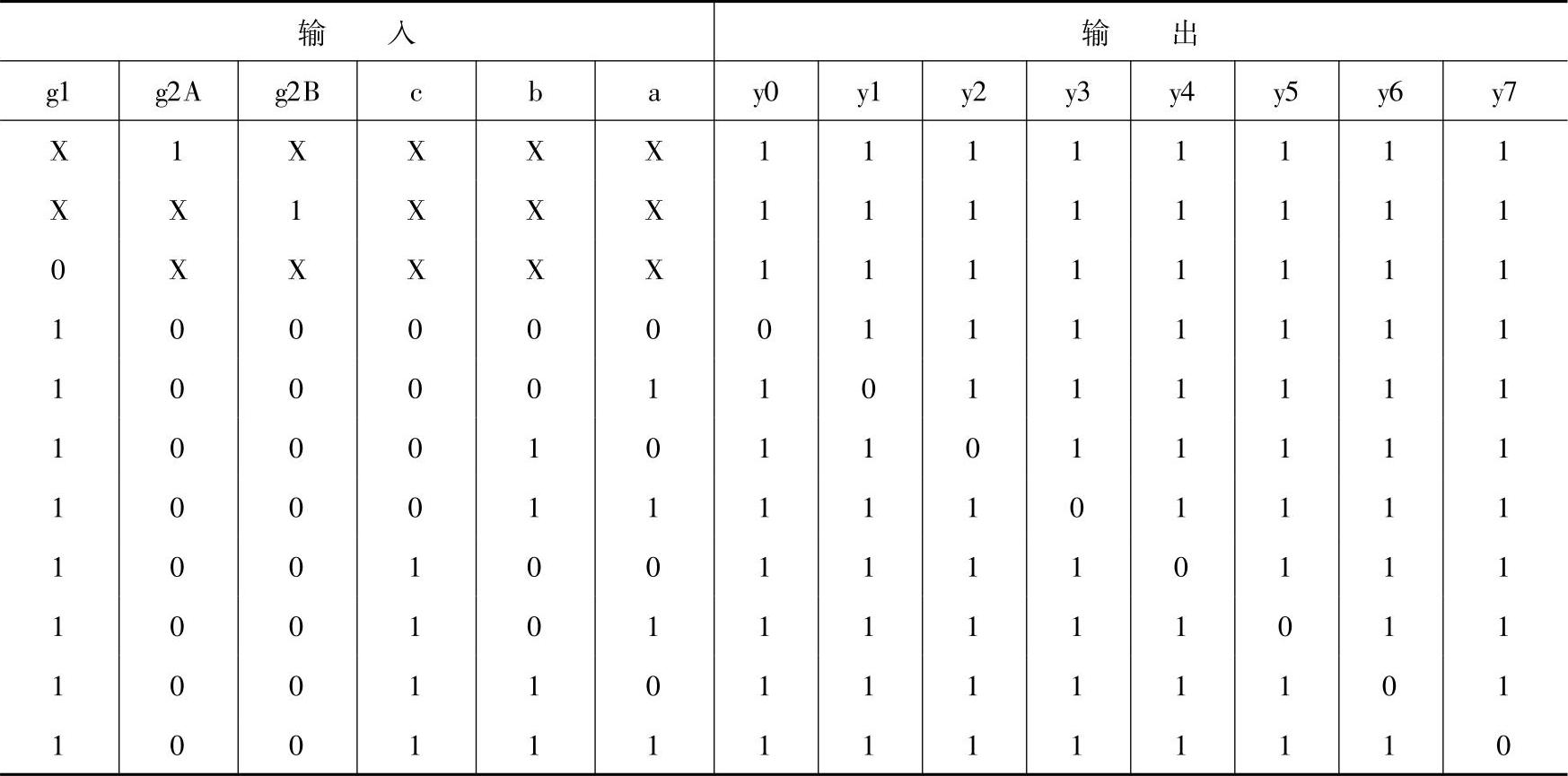

二进制译码器的输入是一组二进制代码,输出是一组与输入代码一一对应的高、低电平信号。二进制译码器一般具有n个输入端,2n个输出端。74LS138是常用的一种二进制译码器,它具有3个输入端、8个输出端。真值表见表5-2。其工作原理是:当译码器的输入使能端g1=1、g2A+g2B=0时,译码器处于工作状态,根据输入信号的不同组合,可译出8个输出信号,输出为低电平有效;否则译码器不能工作,输出端被封锁为高电平。

表5-2 74LS138译码器的真值表

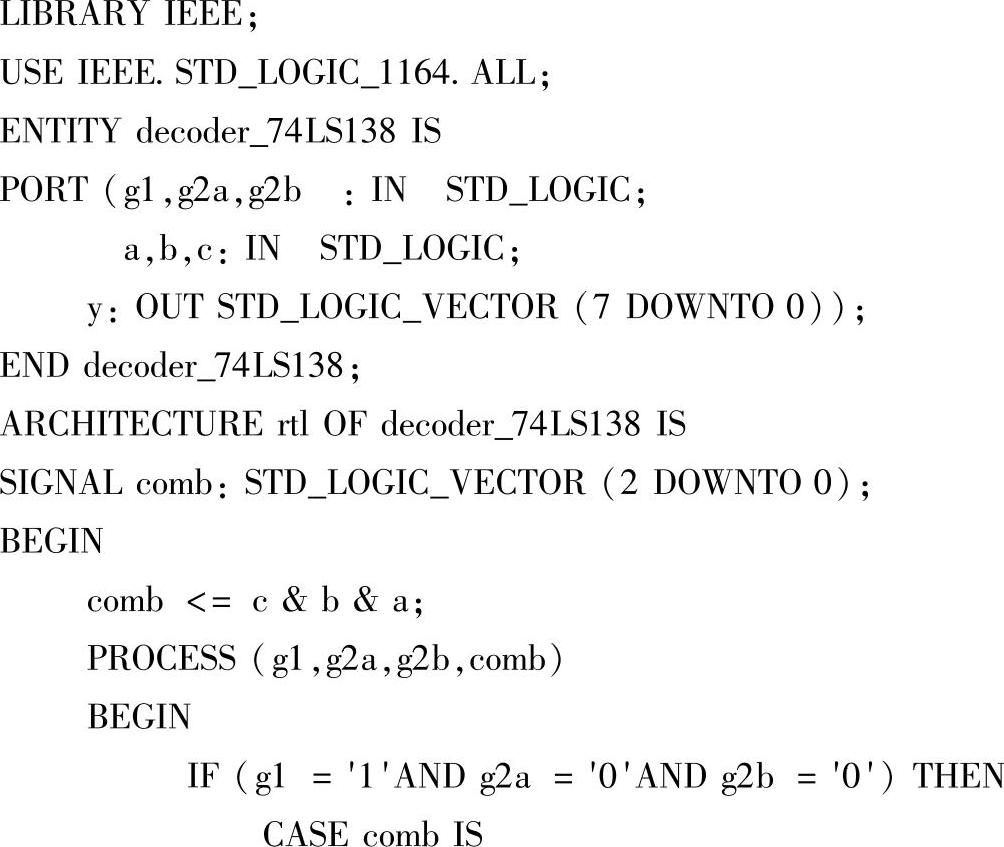

用VHDL描述的74LS138译码器的源程序如例5.5所示。

例5.5

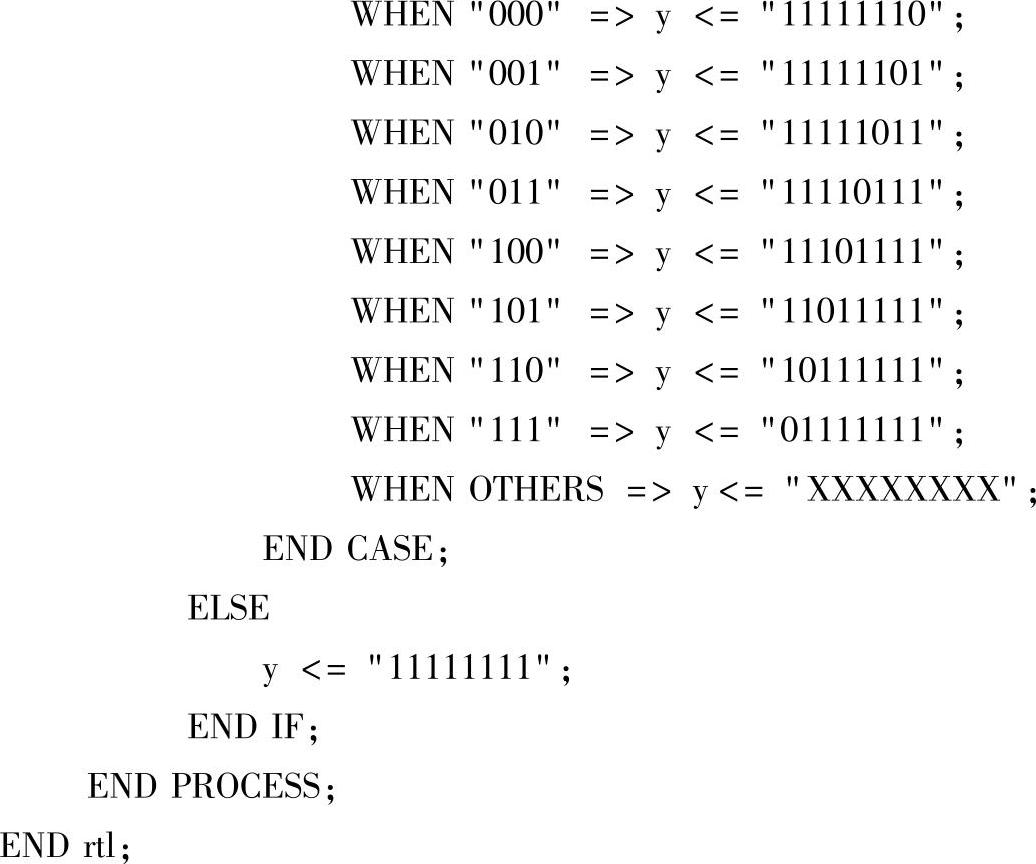

74LS138译码器电路的仿真波形如图5-3所示。从图中可以看出,当g1、g2a和g2b三种信号中的任一为任意值时,y为“XXXXXXXX”;当g1=‘1’、g2a=‘0’和g2b=‘0’时,c、b、a分别赋初值时,结果y是正确的。

图5-3 74LS138译码器电路的仿真波形

2.二-十进制译码器

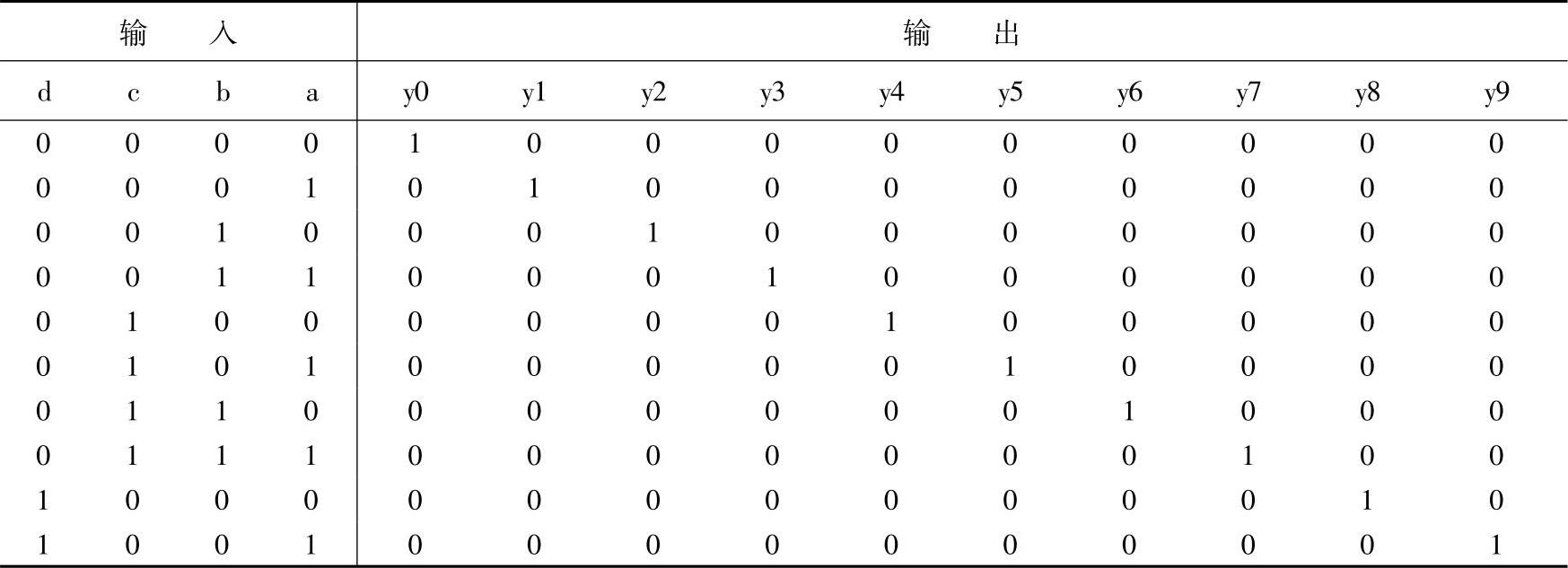

二-十进制码是指用4位二进制码来表示1位十进制数中的0~9这10个数码,简称BCD码。二-十进制译码器是实现8421-BCD码至十进制译码的电路。真值表见表5-3,输出为高电平有效。

表5-3 二-十进制译码器真值表

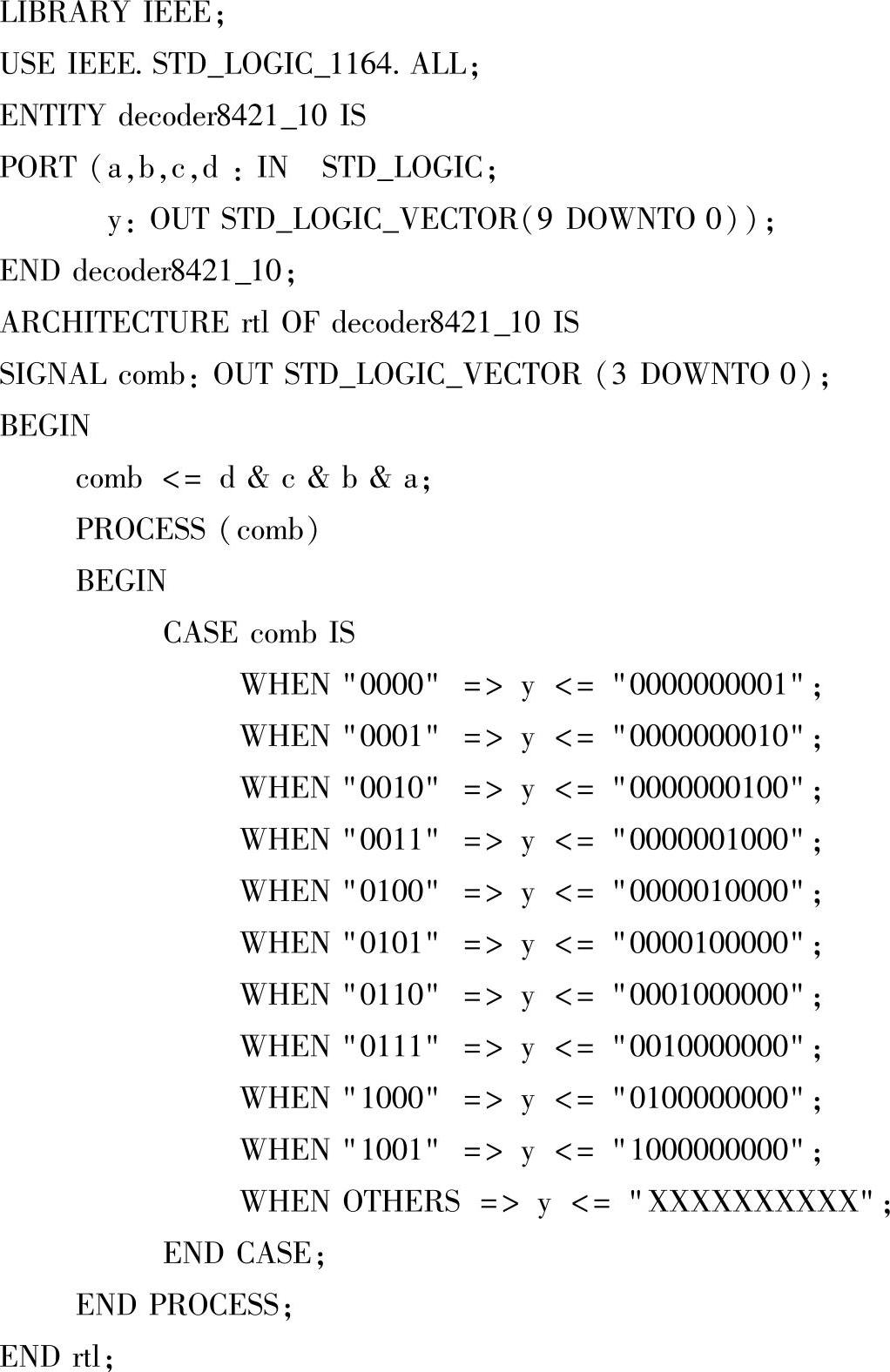

用VHDL描述的二-十进制译码器的源程序如例5.6所示。(https://www.xing528.com)

例5.6

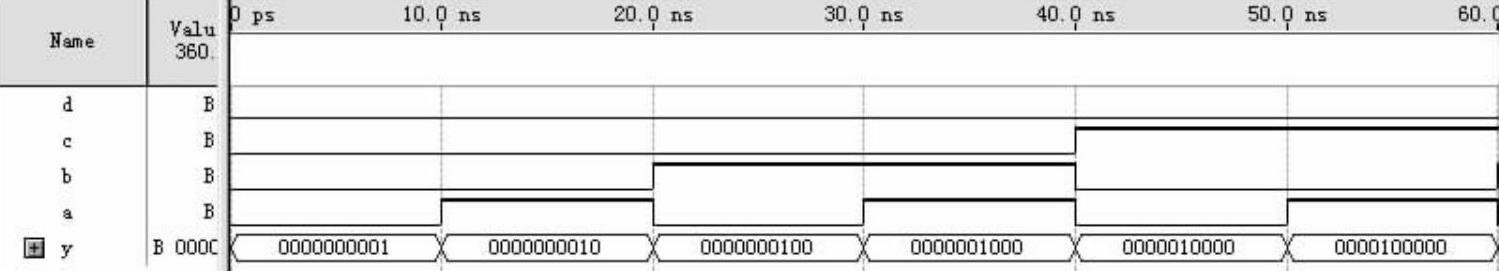

二-十进制译码器电路的仿真波形如图5-4所示。从图中可以看出,当a、b、c和d四路信号赋初值,结果y是正确的。

图5-4 二-十进制译码器电路的仿真波形

3.7段显示译码器

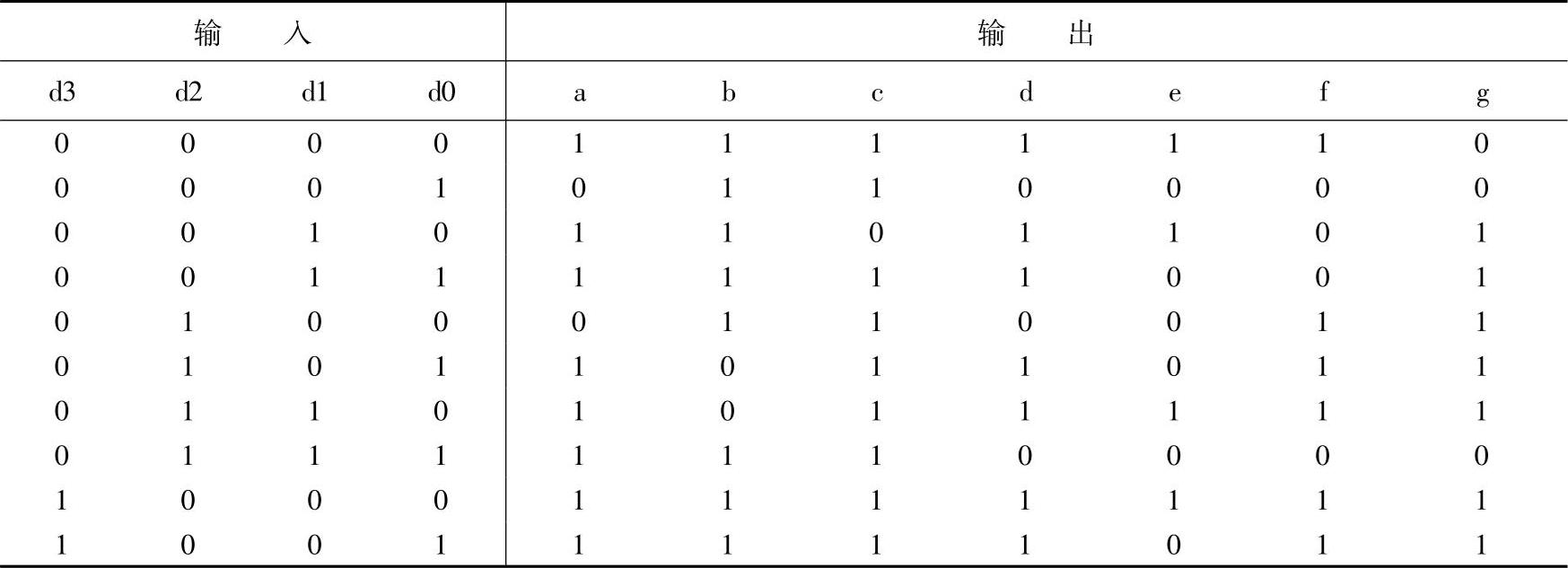

7段显示译码器是指将十进制的代码译成数码管显示对应的段。对于共阴极数码管,译码器输出高电平有效,其真值表见表5-4。

表5-47 段显示译码器真值表

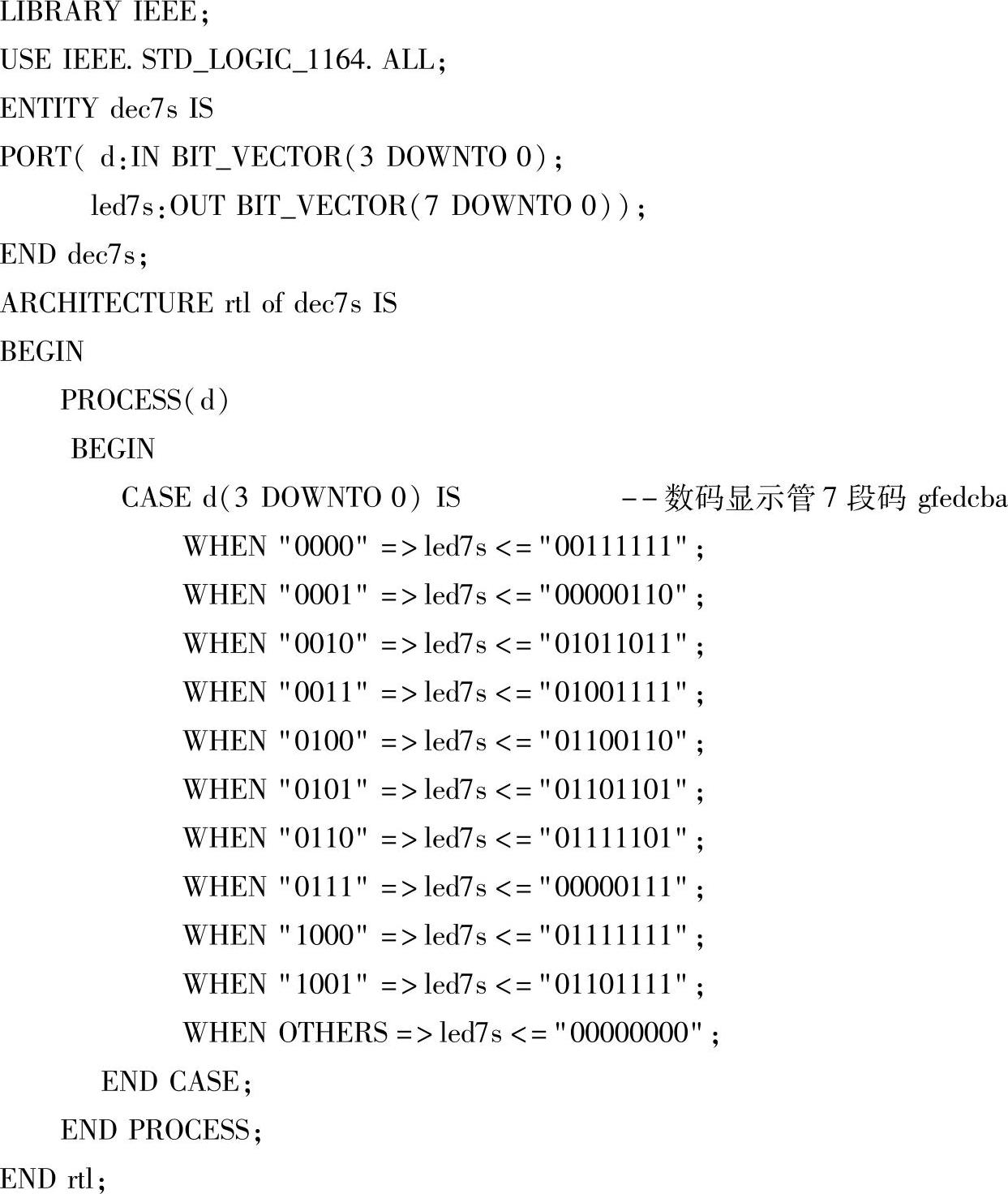

用VHDL描述的7段显示译码器的源程序如例5.7所示。

例5.7

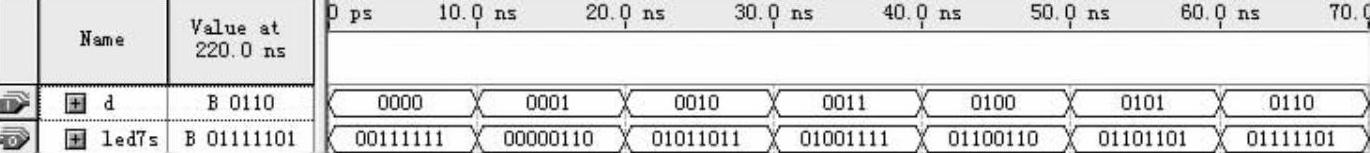

7段显示译码器电路的仿真波形如图5-5所示。从图中可以看出,当d信号赋值时,结果led7s是正确的。

图5-57 段显示译码器电路的仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。