1.实验目的

熟悉用VHDL设计计数、译码和显示电路的方法。

2.实验原理

十进制计数器完成对时钟脉冲的计数,并将计数结果通过显示译码器进行译码,最后由7段数码管进行显示。

3.实验仪器

1)计算机(预装QuartusII软件)。

2)EDA技术实验箱。

4.实验内容

1)新建工程项目top。

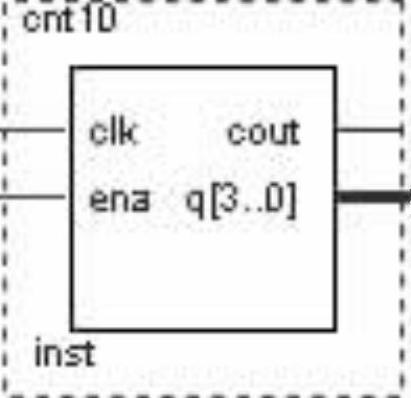

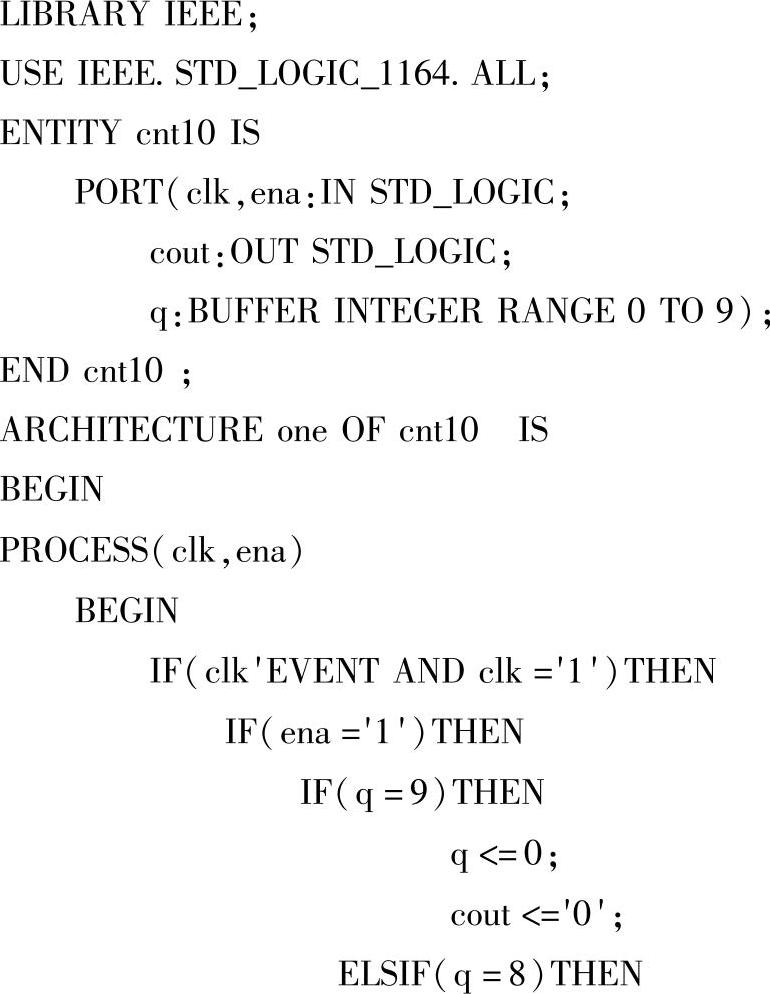

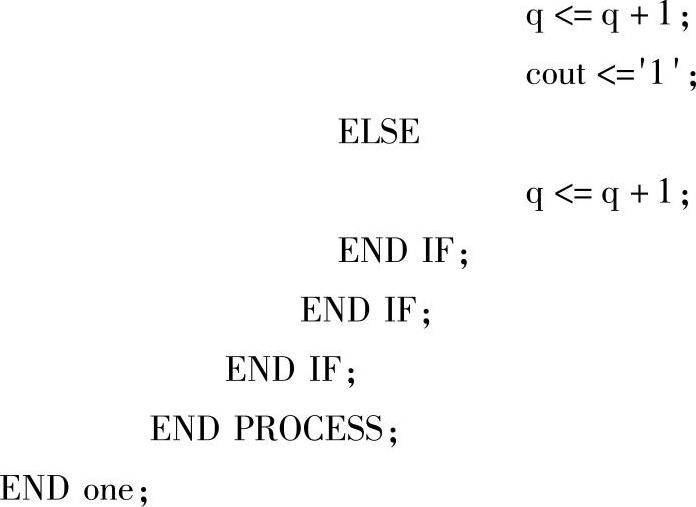

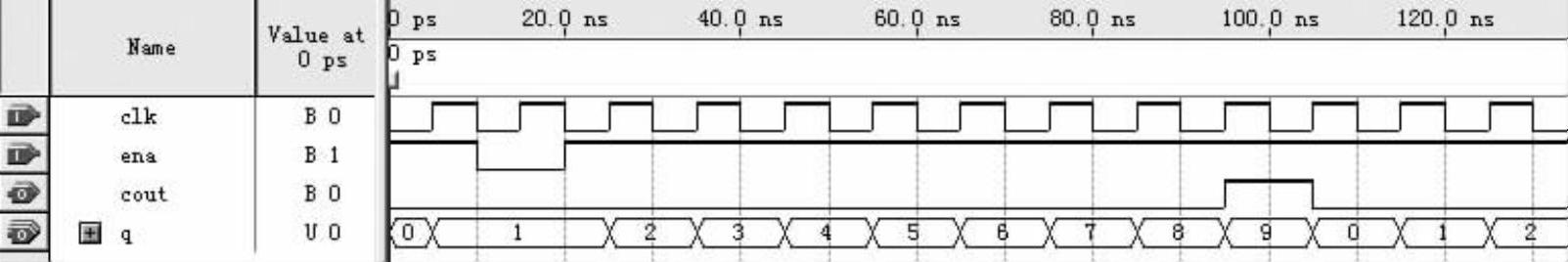

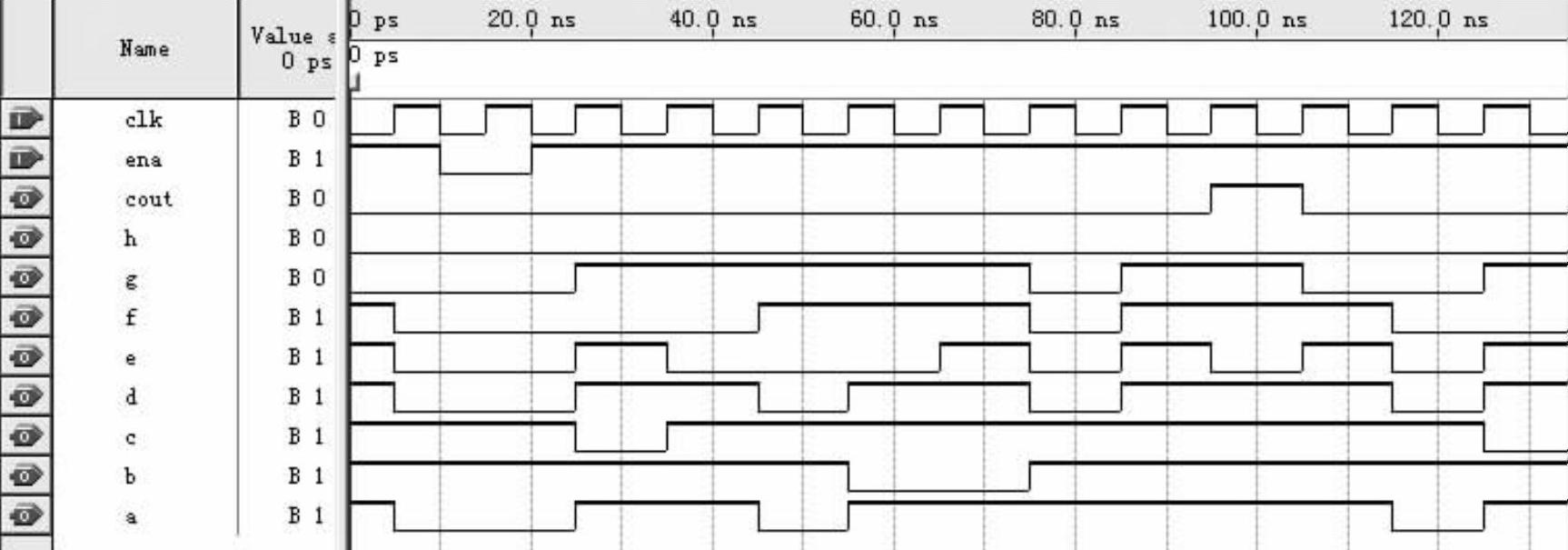

2)在QuartusⅡ的VHDL文本编辑窗口,输入如下十进制加法计数器的VHDL文本文件,并以cnt10.vhd为文件名保存于工程目录top中,其计数器元件符号如图6-41所示,仿真波形如图6-42所示。

图6-41 计数器元件符号

图6-42 计数器仿真波形图

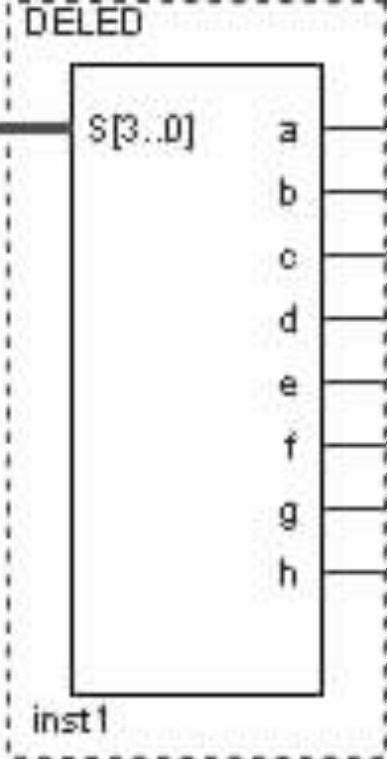

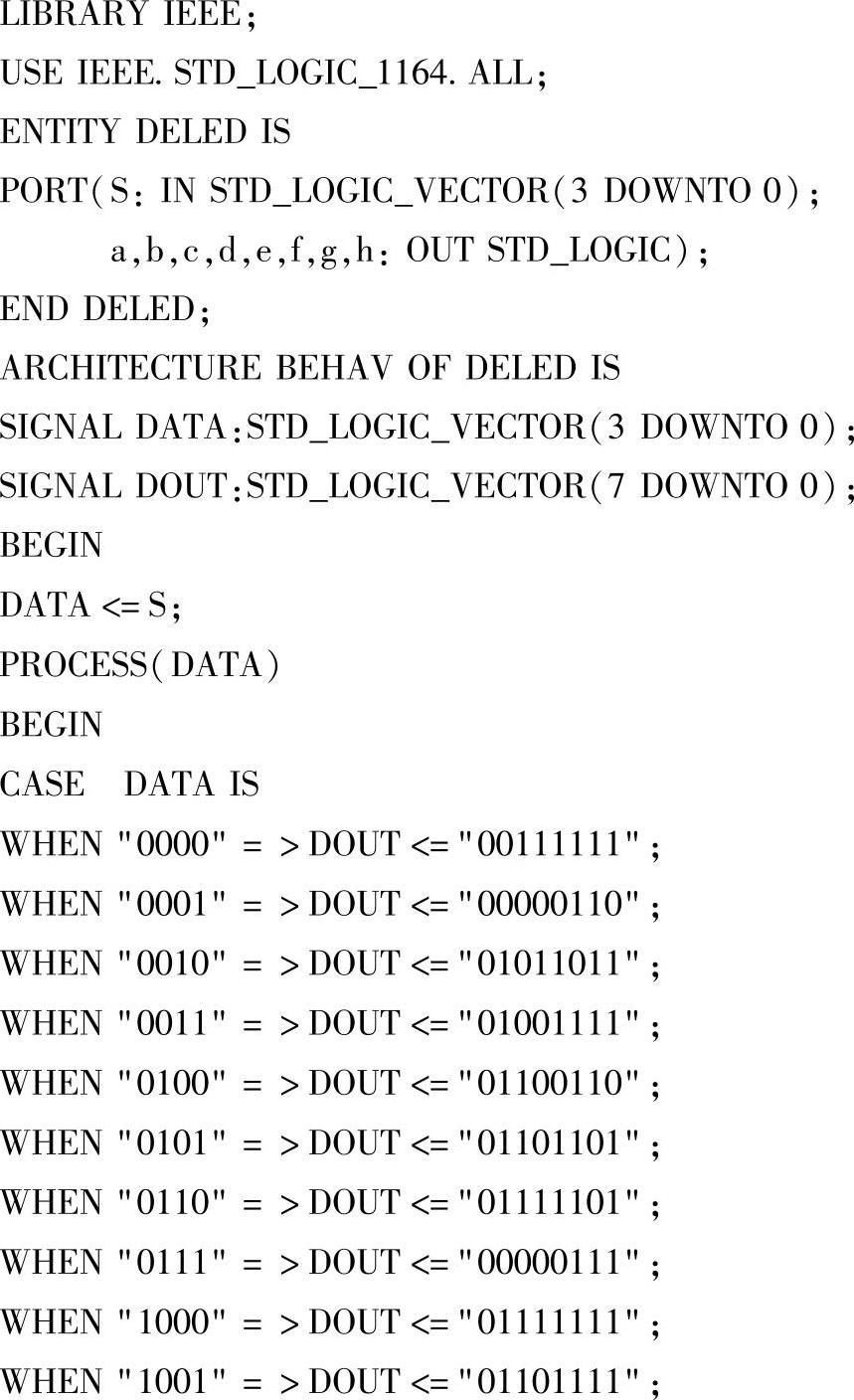

3)在QuartusⅡ的VHDL文本编辑窗口,输入如下显示译码电路的VHDL文本文件,并以DELED.vhd为文件名保存于工程目录top中,其显示译码电路元件符号如图6-43所示。(https://www.xing528.com)

图6-43 显示译码电路元件符号

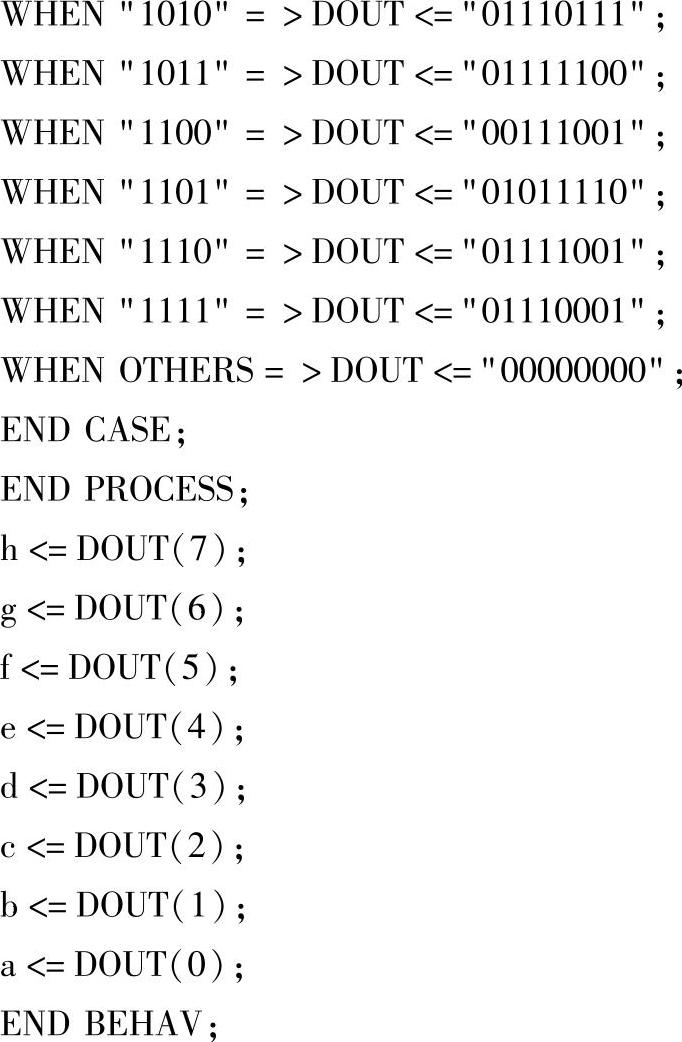

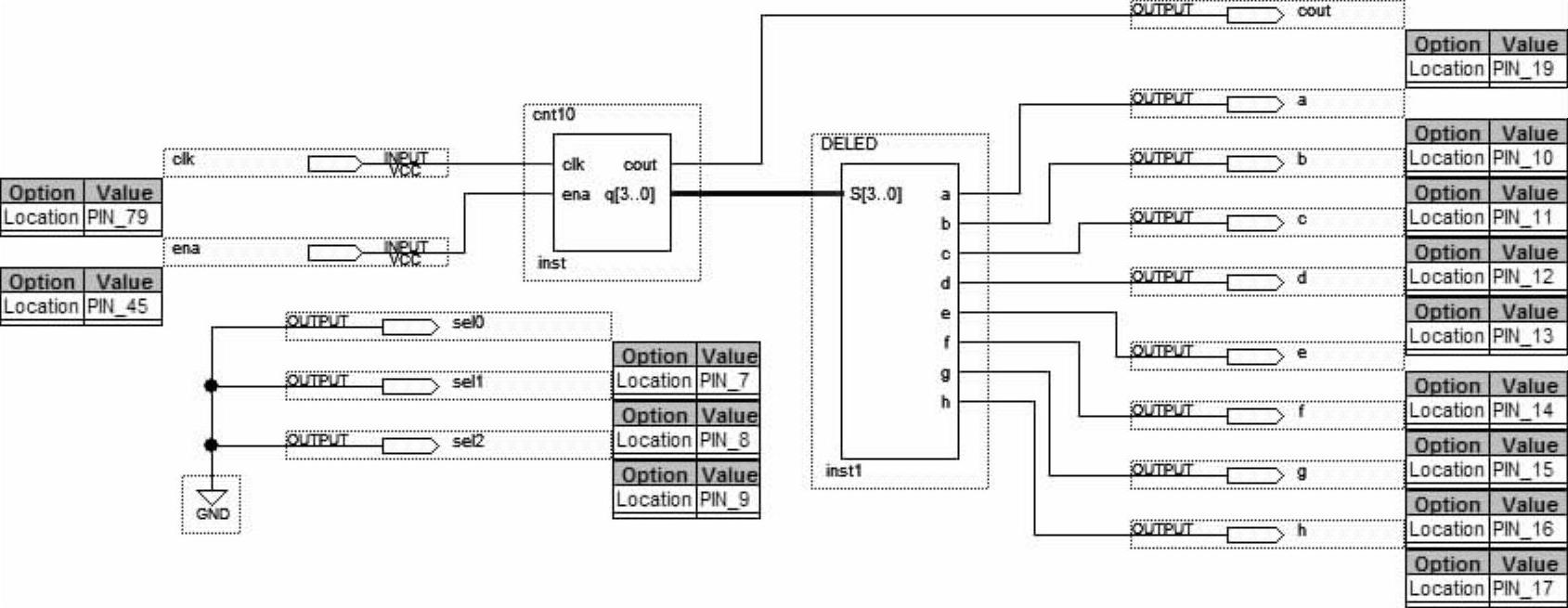

4)设计十进制计数、译码和显示电路的顶层文件top.bdf。在工程项目top下的Quartus II原理图编辑窗口,将十进制计数器的元件符号cnt10和显示译码电路元件符号DELED调出,并按图6-44所示连接,完成的顶层文件用top.bdf作为文件名存入工程目录top中,其仿真波形如图6-45所示。

图6-44 十进制计数、译码和显示电路图

5)引脚锁定及编程下载。根据ZY11203E型EDA技术实验箱FPGA目标芯片EP1K30QC208-2引脚排列图进行引脚锁定,并添加位选信号sel2、sel1、sel0,如图6-46所示,就可以下载到目标芯片进行验证了。

5.实验报告

根据实验内容写出实验报告,包括VHDL程序设计、软件编译、仿真分析、引脚锁定情况、硬件测试和详细实验过程。

图6-45 十进制计数、译码和显示仿真波形图

图6-46 计数、译码和显示电路引脚锁定

6.思考题

参考十进制加法计数器的设计方法,设计一个60进制计数、译码和显示电路。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。