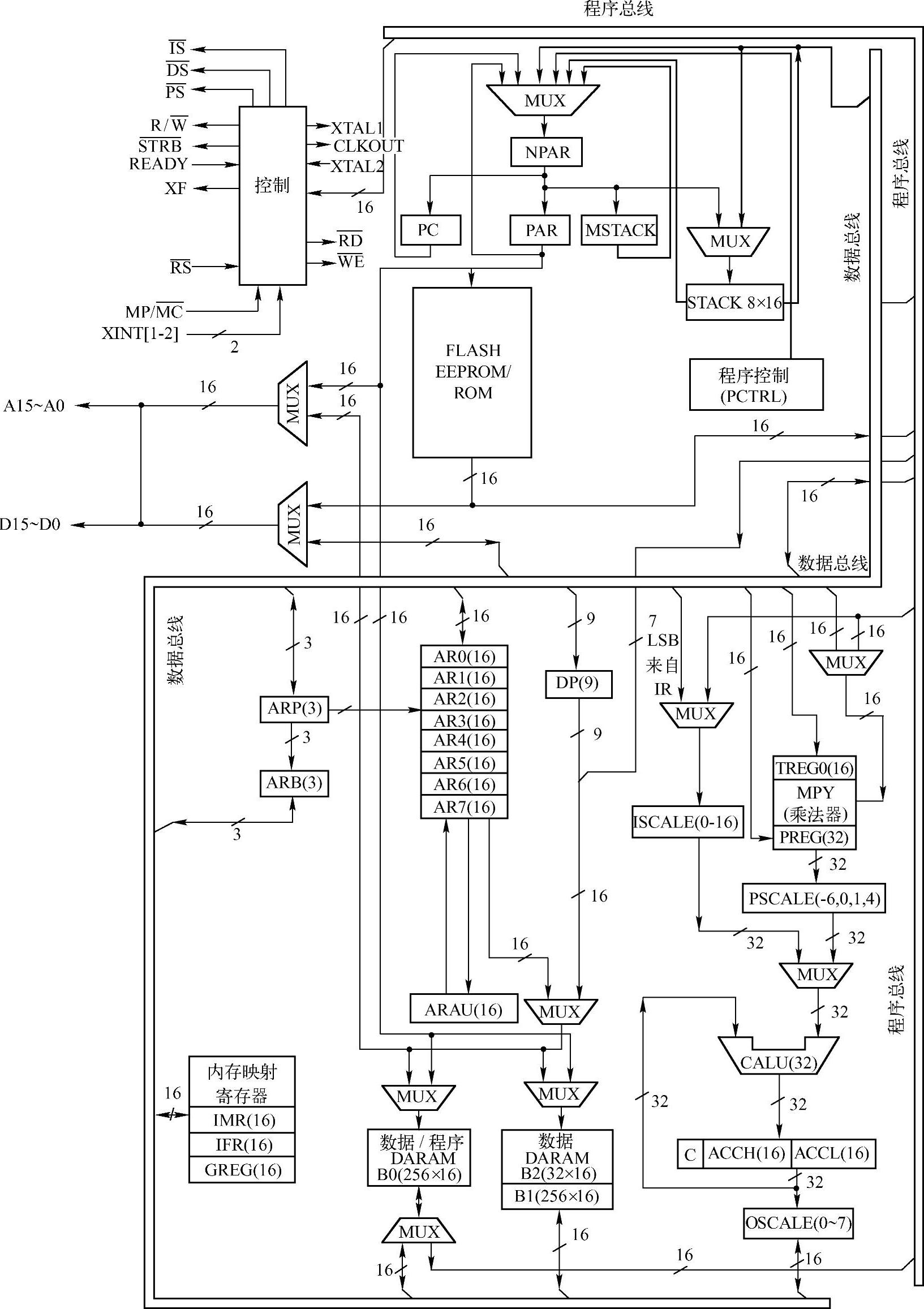

【摘要】:240x DSP的CPU内部总体结构功能框图如图3-1所示,其中的功能模块符号说明见表3-1。主要完成CPU内部寄存器与各逻辑部件之间或者CPU与外部存储器之间的数据传递。可以执行16位×16位的二进制补码乘法运算,并产生32位的计算结果。寄存器TREG提供乘法的一个乘数,乘积被送往PREG寄存器中。CPU的移位器实现对操作数的移位操作。

240x DSP的CPU内部总体结构功能框图如图3-1所示,其中的功能模块符号说明见表3-1。可以看出,240x的CPU主要由总线、CPU寄存器、程序地址发生器和控制逻辑、辅助寄存器算术单元(ARAU)、中央算术逻辑单元(CALU)、乘法器和移位器等逻辑部件组成。

1)总线。主要完成CPU内部寄存器与各逻辑部件之间或者CPU与外部存储器之间的数据传递。

2)程序地址发生器和控制逻辑。用于自动产生指令地址,将其送往程序地址总线,并控制对应指令的读取。

3)ARAU。主要作用是产生指令操作数的地址并将其送往对应的数据地址总线。

4)CALU。执行二进制补码的算术运算和布尔运算。在运算之前,CALU从寄存器、数据存储器或程序控制逻辑单元接收数据,然后进行运算,最后把结果存入寄存器或数据存储器中。

图3-1 240x DSP CPU内部结构功能框图(https://www.xing528.com)

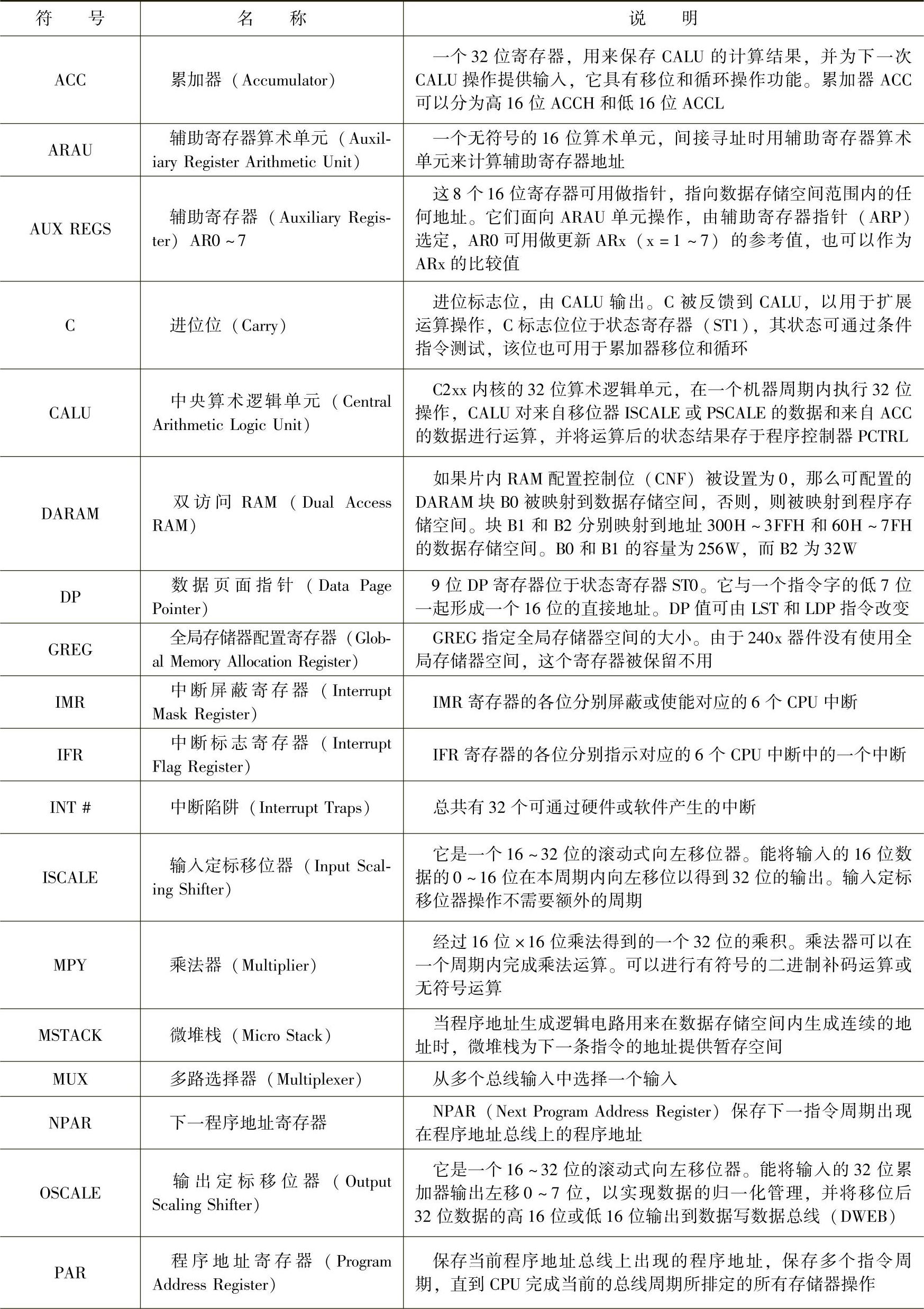

表3-1 240xDSP的CPU的功能模块符号说明

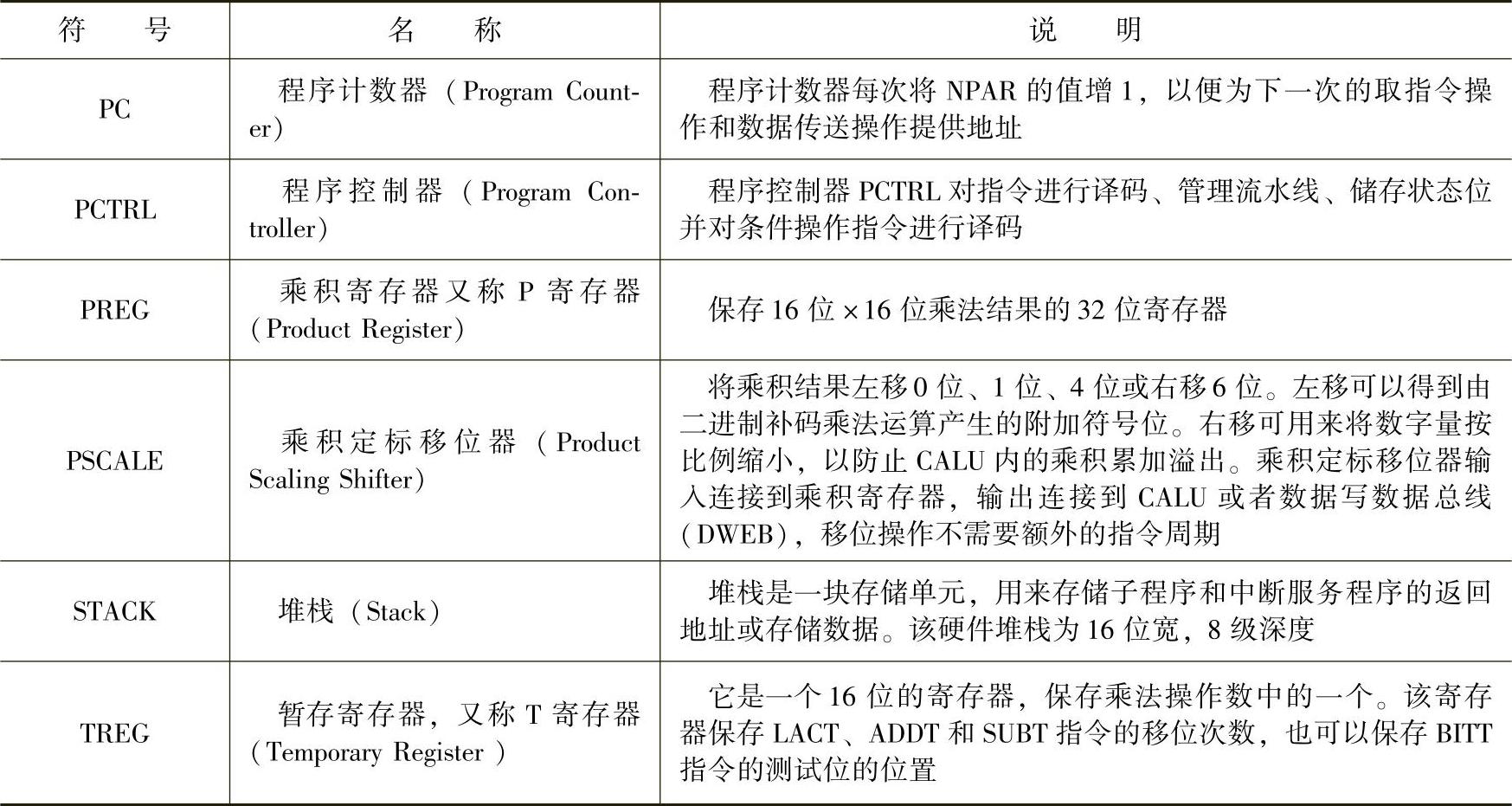

(续)

5)乘法器。可以执行16位×16位的二进制补码乘法运算,并产生32位的计算结果。乘法器采用16位乘数寄存器(TREG)、32位乘积寄存器(PREG)和32位累加器(ACC)。寄存器TREG提供乘法的一个乘数,乘积被送往PREG寄存器中。

6)移位器。CPU的移位器实现对操作数的移位操作。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。