设计方法可以简单地分为手工设计、半自动设计和自动设计;还可以分为正向设计和逆向设计,正向设计是从电路功能开始到得到物理版图的设计方法,逆向设计是指从物理版图分析开始到得到逻辑电路并重新设计物理版图的设计方法。

1.结构化设计思想

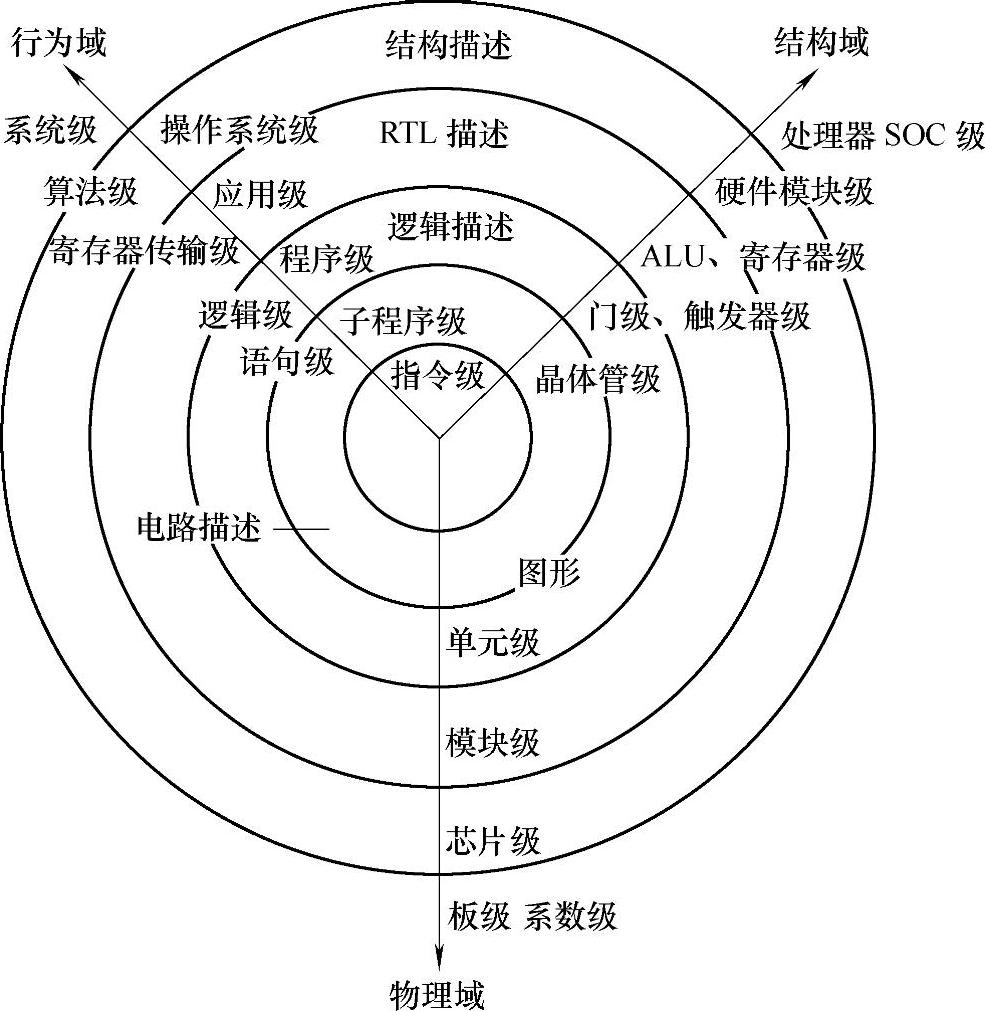

设计所能达到的生产效率在很大程度上影响着集成电路的生存能力,而设计的效率又取决于设计过程中的转化效率,主要包括概念到结构的转化、结构到逻辑模块的转化、逻辑结构到逻辑电路的转化和逻辑电路到物理版图的转化。一个好的VLSI设计系统在三个描述域(行为域、结构域及物理域)和抽象级(结构级或功能级、寄存器传输级(Register Transfer Level,RTL)及电路级)上应该是完全一致的,根据应用的不同,可以在不同的方面进行度量,如性能方面(速度、功耗、功能及灵活性)、芯片尺寸(费用)、设计时间(进度)、验证的简便性和可测试性等。描述域和抽象级之间的关系——Gajski-KuhnY图如图4-26所示。

图4-26 Gajski-KuhnY图

简化设计过程的方法是使用约束和抽象,使用约束可以实现设计过程自动化,使用抽象可以压缩细节,从一个简单的目标进行处理。

就设计方法而言,结构化的设计方法非常适合处理设计复杂性方面。结构化的设计方法一般主要包括以下几个方面:层次化、模块化、规则化和局部化。层次化设计时,可以将一个系统划分成多个模块,然后对每一个模块进行进一步划分,直到可以详细理解各个子模块的复杂性为止。规则化的设计原则可以用于设计层次的各个层,在电路级可以使用同样尺寸的晶体管,在门级可以使用固定高度、可变长度的逻辑门。规则化的设计方法可以辅助验证,减少需要验证的子部件的数量。模块化原则规定模块必须具有明确定义的功能和接口。局部化目前指时间局部化,或者是指遵守某种时钟或时序协议。时间局部化的关键问题之一是让所有的信号都参考一个时钟,因此要指明输入信号与时钟边沿相关的建立时间和保持时间,输出信号与时钟边沿相关的延迟时间。

2.设计方法

设计方法与设计和实现系统所需的时间和费用有明显的关系。为了选择合适的设计方案,理解某种实现技术的成本、性能和限制是很重要的。

从具体的逻辑功能特点上,集成电路可以分为通用集成电路和专用集成电路(Applica-tion Specific Integrated Circuit,ASIC)。ASIC又可以分为全定制集成电路和半定制集成电路。

(1)全定制设计方法 全定制设计方法(Full-Custom Design Approach)是指利用人机交互图形系统,由设计人员从每个半导体器件的图形和尺寸开始设计,直至整个版图的布局和布线。

全定制设计的特点是针对每个元器件进行电路参数和版图参数的优化,它往往采用自由格式的版图设计规则进行设计,并且由设计者不断完善版图设计,以使每个元器件及其内部连接安排得最紧凑、最合理。这样就可以得到最佳的性能(包括速度和功耗)以及最小的芯片面积,有利于提高集成度和降低生产成本。它适用于要求高速度、低功耗和小面积的设计。

这种设计方法还要求有完整的检查和验证工具,同时要求设计者具有微电子技术和生产工艺方面的专业知识以及一定的设计经验。

这种设计方法的缺点是设计周期很长,查错困难较大,且设计费用高。

(2)符号设计法 符号设计法版图是利用一组预先定义好的符号来表示版图中的晶体管、接触孔和金属线等。

设计人员根据网络要求画出一相应的符号,自动转换程序将元件对应的符号转换为版图图形。此时不用考虑版图规则的细节,大大提高了效率。

目前有三种符号设计法:固定栅格式、梗图式和虚网格式。(https://www.xing528.com)

固定栅格式是把芯片表面划分成均匀间隔的栅格,栅格大小表示最小的特征尺寸或布局上的容差。设计人员根据要求将这些符号画在栅格图上,经自动转换得到版图。

梗图式是设计人员根据网络图画出一对应的梗形草图,符号设计法系统将其整理成规则的梗形图,再进一步转换成版图。

虚网格式是指网格之间的最终间距取决于相邻网格之间电路元器件的密度和相互关系,不再是固定的。

(3)半定制设计方法 半定制设计方法适用于专用集成电路ASIC。

1)标准单元设计法。在标准单元设计法中,基本单元电路的版图是预先设计好的,放在EDA系统的库中,而且具有统一的高度。设计者利用EDA系统绘制电路框图,然后EDA系统能够利用框图中单元逻辑电路符号与单元电路版图的对应关系,自动布局布线,得到版图。设计者也可以利用标准单元的版图人工布局布线。一般来说,人工布局布线的硅片面积利用率高,但费时较多,易出错。

标准单元设计法不要求设计者必须具有专门的半导体工艺知识。

2)门阵列设计方法。门阵列设计方法是在一个芯片上把逻辑门排列成阵列形式,每个门具有相同的版图形状,门与门之间暂时不相连,因此构成一个未完成的逻辑阵列。严格地讲,门阵列是把单元排列成阵列形式,每个单元内有若干器件,通过连接单元内器件使每个单元实现某种类型门的功能,并通过各单元之间的连接实现电路的要求。

由于芯片内的单元是相同的,所以可采用统一的掩膜,而且可以完成连线以外的所有芯片的加工步骤,这样的芯片可以大量制造并保存起来,所以生产周期缩短约一半,成本大大下降。

(4)可编程逻辑器件 可编程逻辑器件的发展基本上经历了PLA→PAL→GAL→EPLD→CPLD→FPGA的过程,其中目前常用的CPLD和FPGA由于集成度高也可称为高密度可编程逻辑器件。

1)CPLD。CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)是EPLD的改进,规模更大,结构更复杂。CPLD包括可编程逻辑宏单元、可编程I/O单元和可编程内部连线。有些CPLD还集成了RAM等。

2)FPGA。FPGA(Field Prom-mable Gate Array,现场可编程门阵列)的规模可以做得很大,其逻辑功能单元不限于逻辑门,可以具有较复杂的功能。

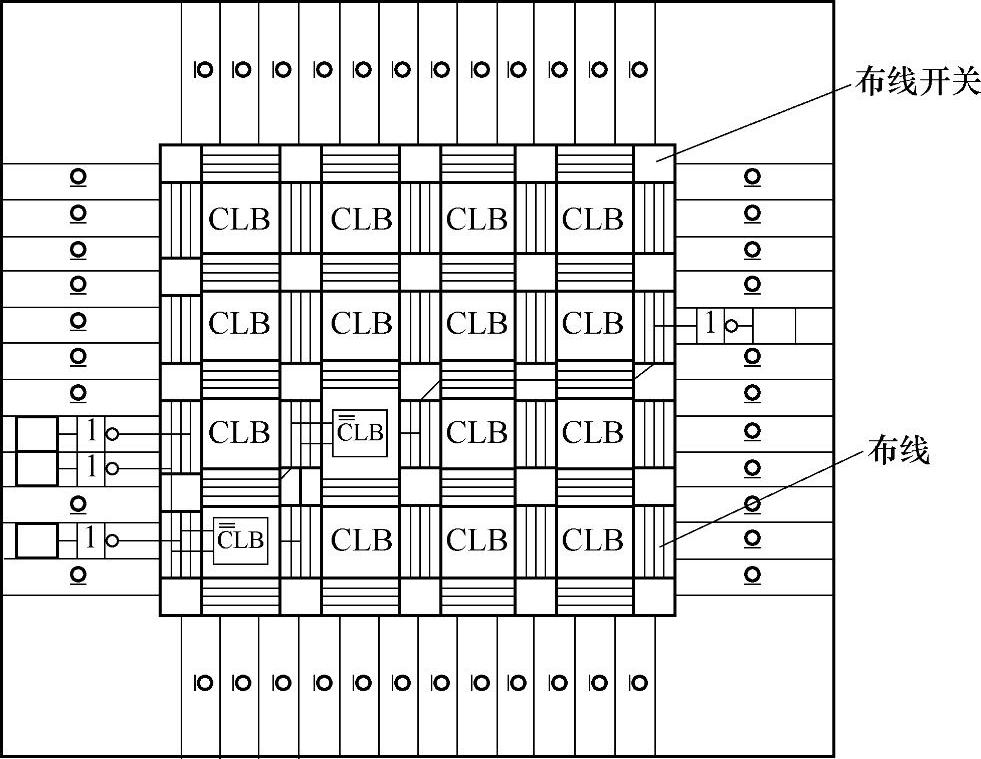

图4-27 简化的FPGA布局规划

FPGA实现的功能由逻辑结构的配置数据决定,工作时这些数据存放在芯片内部的SRAM或熔丝图上。FPGA设计过程由专门的设计软件来实现,最后生成一个用来对FPGA器件进行编程的文件。FPGA器件的配置数据可以存放在芯片外部的EPROM或其他存储器上,设计人员可以控制芯片的加载过程并现场修改器件的逻辑功能,因此称为现场可编程。

FPGA主要包括输入输出模块(Input Output Block,IOB)、可配置逻辑模块(Configu-rable Logic Block,CLB)和可编程互连总线(Programmable Interconnect,PI),简化的FPGA布局规划如图4-27所示。三个部分都可以改变,因此改变FPGA器件实现的功能可以通过改变连接或内部逻辑单元来实现。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。