加法运算电路是对多个输入信号进行求和运算的电路,而减法运算电路是对输入信号进行相减运算的电路。加法与减法电路可以由单运放或双运放构成。

1.加法电路

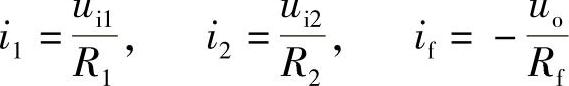

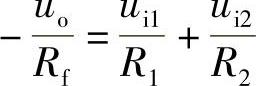

如图4-16所示,加法电路由单运放实现。与比例运算电路分析方法相似,利用“虚短”和“虚断”的概念,可知in=ip=0,un=up=0,由此可知

由于if=i1+i2,所以

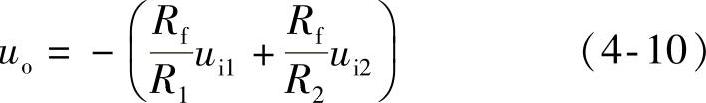

经整理得

若R1=R2=Rf,则式(4-10)变为

uo=-(ui1+ui2) (4-11)

输出电压等于各输入电压之和的负值。

若在图4-16的输出端再接一级反相器,则可消除-号,实现常规的算术加法。双运放组成的加法电路如图4-17所示。

图4-16 反相加法运算电路

图4-17 双运放加法运算电路

图4-18 单运放减法电路

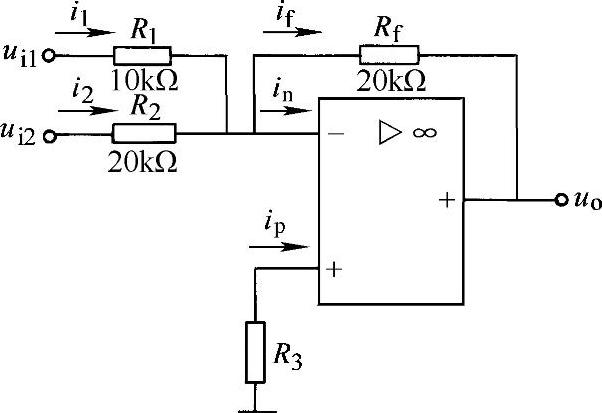

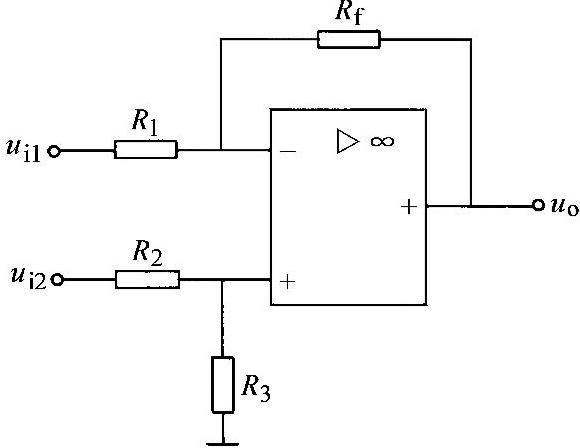

2.减法电路

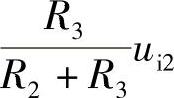

图4-18所示为单运放构成的减法运算电路,两个输入信号分别由运放的同相输入端和反相输入端输入。利用“虚短”和“虚断”的概念可知R2与R3相当于串联,因而同相输入信号ui2被R2和R3分压后,只有R3上的电压输入给运放,即实际的同相输入信号电压为 。根据叠加定理,当ui1单独作用时相当于反相比例电路,它产生的输出信号

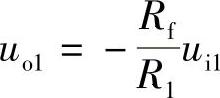

。根据叠加定理,当ui1单独作用时相当于反相比例电路,它产生的输出信号

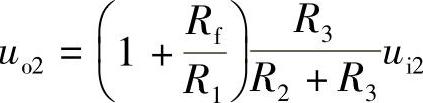

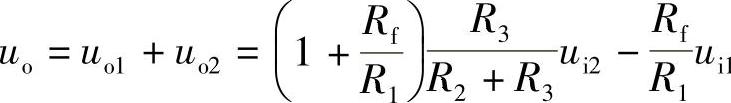

ui2单独作用时相当于同相比例电路,它产生的输出信号

(https://www.xing528.com)

(https://www.xing528.com)

当ui1和ui2共同作用时产生的输出信号

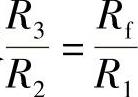

若取 ,则

,则

即输出信号电压正比于两个输入信号电压之差。

当Rf=R1时

uo=ui2-ui1 (4-13)

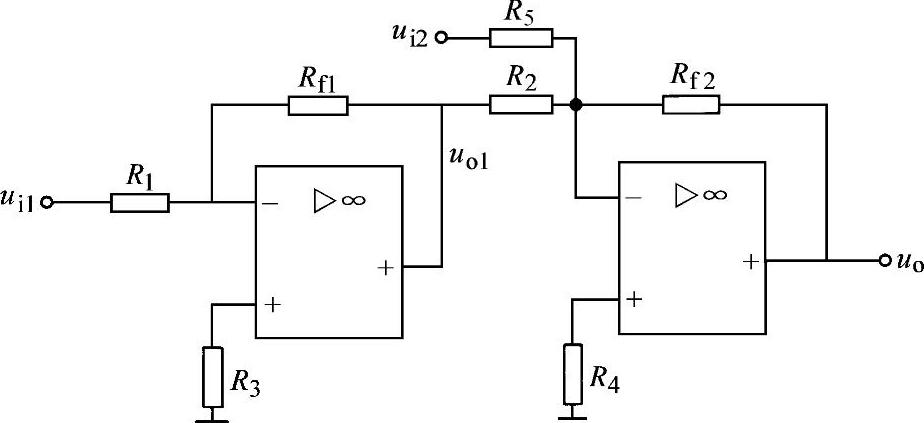

输出电压等于两个输入电压之差。减法运算也可以由双运放来实现,图4-19所示为双运放构成的减法电路。第一级为反

相比例电路,若Rf1=R1,则uo1=-ui1;第二级为反相加法电路,于是有

若取Rf2=R2,则上式变为

uo=ui1-ui2 (4-15)

可见,电路实现了常规的算术减法运算。

图4-19 双运放减法电路

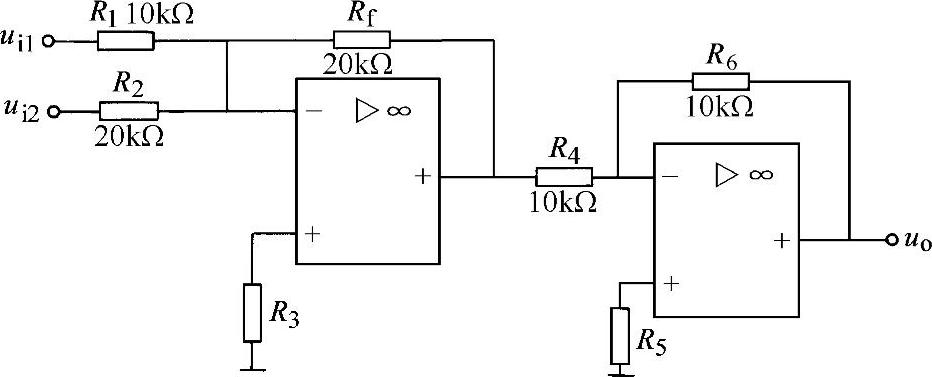

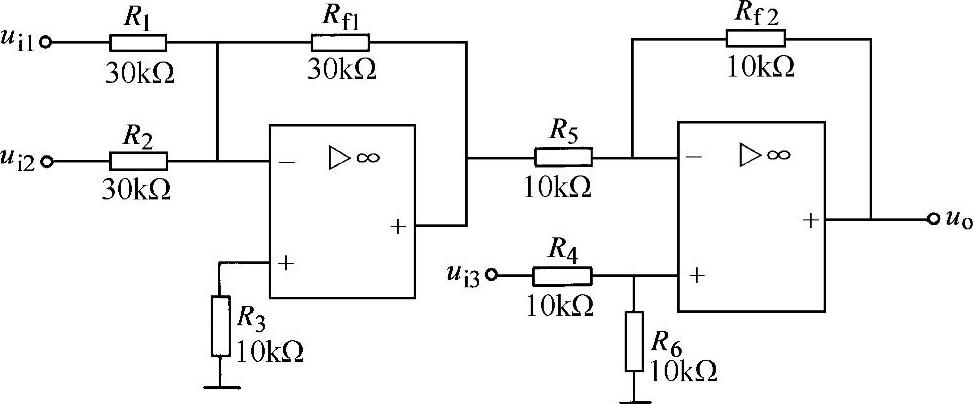

例4-2 图4-20所示为双运放组成的电路,已知电阻R1=R2=Rf1=30kΩ,R3=R4=R5=R6=Rf2=10kΩ,输入电压ui1=0.2V,ui2=0.3V,ui3=0.5V,求输出电压uo。

图4-20 例4-2

解 电路第一级为加法运算电路,第二级为减法运算电路。输出电压与输入电压的关系应分别满足式(4-11)和式(4-13)。由此可得

uo=ui3-[-(ui1+ui2)]

=ui1+ui2+ui3

=0.2V+0.3V+0.5V=1V

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。