模-数转换是将模拟信号转换为相应的数字信号,把模拟信号转换为数字信号称为模-数转换,简称A-D(Analog to Digital)转换。实现A-D转换的电路称为A-D转换器,或写为ADC(Analog-Digital Converter);实际应用中用到大量的连续变化的物理量,如温度、流量、压力、图像、文字等信号,需要经过传感器变成电信号,但这些电信号是模拟量,它必须变成数字量才能在数字系统中进行加工、处理。因此,模-数转换是数字电子技术中非常重要的组成部分,在自动控制和自动检测等系统中应用非常广泛。

A-D转换器是模拟系统和数字系统之间的接口电路,A-D转换器在进行转换期间,要求输入的模拟电压保持不变,但在A-D转换器中,因为输入的模拟信号在时间上是连续的,而输出的数字信号是离散的,所以进行转换时,只能在一系列选定的瞬间对输入的模拟信号进行采样,然后再把这些采样值转化为输出的数字量,一般来说,转换过程包括取样、保持、量化和编码四个步骤。

图12-3 DAC0832的三种工作方式

a)双缓冲器型 b)单缓冲器型 c)直通型

A-D转换的一般步骤如下:

1.采样和保持

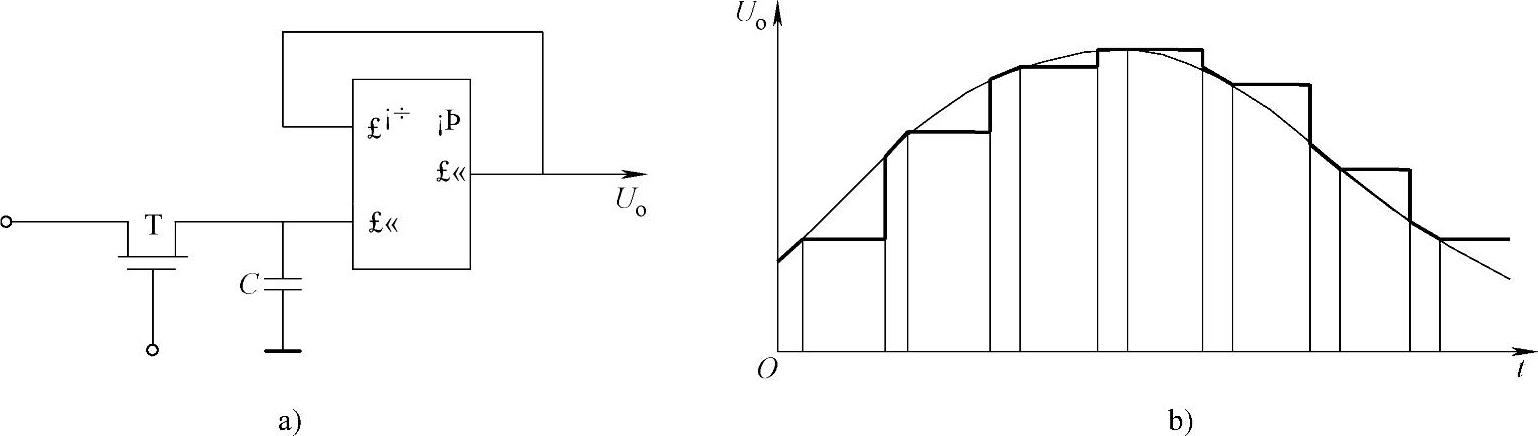

采样(又称抽样或取样)是对模拟信号进行周期性地获取样值的过程,即将时间上连续变化的模拟信号转换为时间上离散、幅度上等于采样时间内模拟信号大小的模拟信号,即转换为一系列等间隔的脉冲。其采样原理如图12-4所示。

图12-4a中,ui为模拟输入信号,us为采样脉冲,uo为取样后的输出信号。

采样电路实质上是一个受采样脉冲控制的电子开关,其工作波形如图12-4b所示。在采样脉冲us有效期(高电平期间)内,采样开关S闭合接通,使输出电压等于输入电压,即uo=ui;在采样脉冲us无效期(低电平期间)内,采样开关S断开,使输出电压等于0,即uo=0。因此,每经过一个采样周期,在输出端便得到输入信号的一个采样值。us按照一定频率fS变化时,输入的模拟信号就被采样为一系列的样值脉冲。当然采样频率fS越高,在时间一定的情况下采样到的样值脉冲越多,因此输出脉冲的包络线就越接近于输入的模拟信号。

图12-4 采样原理图

a)采样原理图 b)工作波形

为了不失真地用采样后的输出信号uo来表示输入模拟信号ui,采样频率fS必须满足:采样频率应不小于输入模拟信号最高频率分量的两倍,即fS≥2fmax(此式就是广泛使用的采样定理)。其中,fmax为输入信号ui的上限频率(即最高次谐波分量的频率)。

ADC把采样信号转换成数字信号需要一定的时间,所以在每次采样结束后,都需要将这个断续的脉冲信号,保持一定时间以便进行转换。图12-5a是一种常见的采样保持电路,它由采样开关、保持电容和缓冲放大器组成。

图12-5 基本采样-保持电路

a)电路 b)输入输出波形

在图12-5a中,利用场效应晶体管做模拟开关。在采样脉冲CP到来的时间τ内,开关接通,输入模拟信号ui(t)向电容C充电,当电容C的充电时间常数为tC时,电容C上的电压在时间τ内跟随ui(t)变化。采样脉冲CP结束后,开关断开,因电容的漏电很小且运算放大器的输入阻抗又很高,所以电容C上电压可保持到下一个采样脉冲到来为止。运算放大器构成电压跟随器,具有缓冲作用,以减小负载对保持电容的影响。在输入一连串采样脉冲后,输出电压uo(t)波形如图12-5b所示。

2.量化和编码

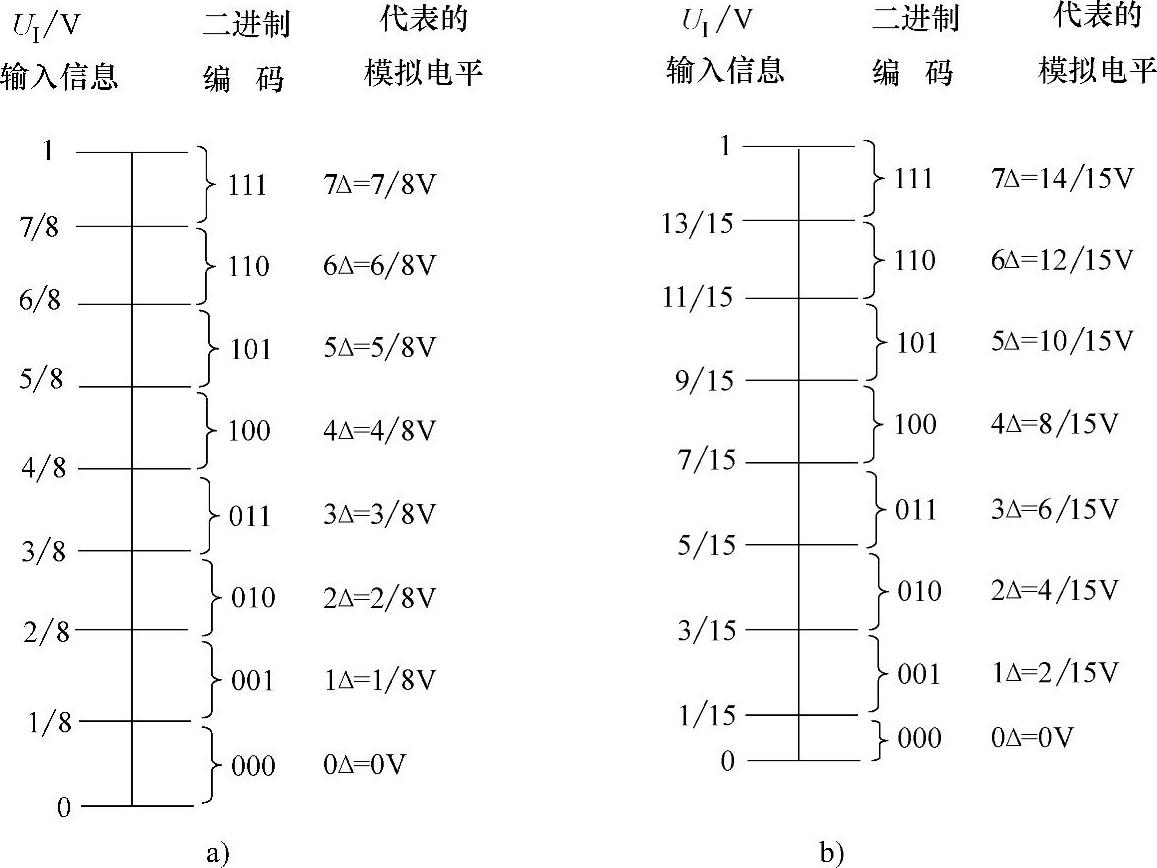

输入的模拟信号经采样—保持电路后,得到的是阶梯形模拟信号,它们是连续模拟信号在给定时刻上的瞬时值,但仍然不是数字信号。必须进一步将阶梯形模拟信号的幅度等分成n级,并给每级规定一个基准电平值,然后将阶梯电平分别归并到最邻近的基准电平上。这个过程称为量化。量化中采用的基准电平称为量化电平,采样保持后未量化的电平uo值与量化电平uq值之差称为量化误差δ,即δ=uo-uq。量化的方法一般有两种:只舍不入法和有舍有入法(或称四舍五入法)。我们将用二进制数码来表示各个量化电平的过程称为编码。此时把每个样值脉冲都转换成与它的幅度成正比的数字量,才算全部完成了模拟量到数字量的转换。

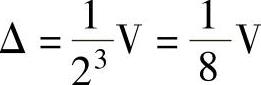

只舍不入的方法是:取最小量化单位Δ=Um/2n,其中Um为模拟电压最大值,n为数字代码位数,将0~Δ之间的模拟电压归并到0·Δ,把Δ~2Δ之间的模拟电压归并到1·Δ,依此类推。这种方法产生的最大量化误差为Δ。比如,将0~1V的模拟电压信号转换成三位二进制代码。有 ,那么

,那么 之间的模拟电压归并到0·Δ,用000表示,

之间的模拟电压归并到0·Δ,用000表示, 之间的模拟电压归并到1·Δ,用001表示,…,依此类推直到将

之间的模拟电压归并到1·Δ,用001表示,…,依此类推直到将 之间的模拟电压归并到7·Δ,用111表示,此时最大量化误差为

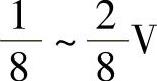

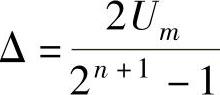

之间的模拟电压归并到7·Δ,用111表示,此时最大量化误差为 。该方法简单易行,但量化误差比较大,为了减小量化误差,通常采用另一种量化编码方法,即有舍有入法。有舍有入的方法是:取最小量化单位

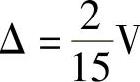

。该方法简单易行,但量化误差比较大,为了减小量化误差,通常采用另一种量化编码方法,即有舍有入法。有舍有入的方法是:取最小量化单位 ,其中Um仍为模拟电压最大值,n为数字代码位数,将

,其中Um仍为模拟电压最大值,n为数字代码位数,将 之间的模拟电压归并到0·Δ,把

之间的模拟电压归并到0·Δ,把 之间的模拟电压归并到1·Δ,…,依此类推。这种方法产生的最大量化误差为

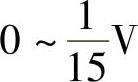

之间的模拟电压归并到1·Δ,…,依此类推。这种方法产生的最大量化误差为 。用此法重做上例,将0~1V的模拟电压信号转换成三位二进制代码。有

。用此法重做上例,将0~1V的模拟电压信号转换成三位二进制代码。有 ,那么将

,那么将 之间的模拟电压归并到0·Δ,用000表示,把

之间的模拟电压归并到0·Δ,用000表示,把 以内的模拟电压归并到1·Δ,用001表示…,直到将

以内的模拟电压归并到1·Δ,用001表示…,直到将 之间的模拟电压归并到7·Δ,用111表示,很明显此时最大量化误差为

之间的模拟电压归并到7·Δ,用111表示,很明显此时最大量化误差为 。比上述只舍不入方法的最大量化误差

。比上述只舍不入方法的最大量化误差 明显减小了(减小了近一半)。因而实际中广泛采用有舍有入的方法。当然,无论采用何种划分量化电平的方法都不可避免地存在量化误差,量化级分得越多(即ADC的位数越多),量化误差就越小,但同时输出二进制数的位数就越多,要实现这种量化的电路将更加复杂。因而在实际工作中,并不是量化级分的越多越好,而是根据实际要求,合理地选择A-D转换器的位数。图12-6表示了两种不同的量化编码方法。

明显减小了(减小了近一半)。因而实际中广泛采用有舍有入的方法。当然,无论采用何种划分量化电平的方法都不可避免地存在量化误差,量化级分得越多(即ADC的位数越多),量化误差就越小,但同时输出二进制数的位数就越多,要实现这种量化的电路将更加复杂。因而在实际工作中,并不是量化级分的越多越好,而是根据实际要求,合理地选择A-D转换器的位数。图12-6表示了两种不同的量化编码方法。

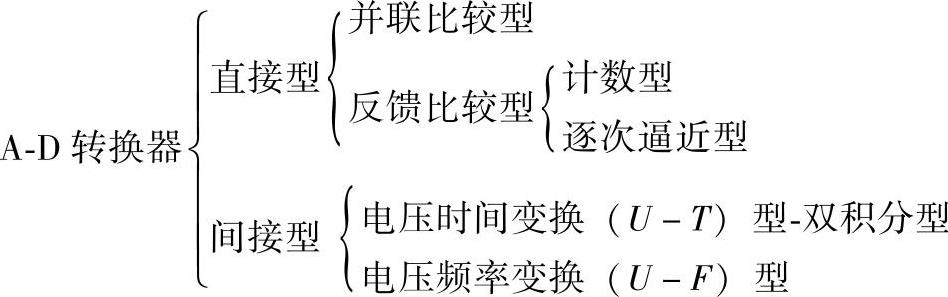

3.A-D转换器的分类

目前,A-D转换器的种类虽然很多,但从转换过程来看,可以归结成两大类,一类是直接A-D转换器,另一类是间接A-D转换器。在直接A-D转换器中,输入模拟信号不需要中间变量就直接被转换成相应的数字信号输出,如计数型A-D转换器、逐次逼近型A-D转换器和并联比较型A-D转换器等,其特点是工作速度高,转换精度容易保证,调准也比较方便。而在间接A-D转换器中,输入模拟信号先被转换成某种中间变量(如时间、频率等),然后再将中间变量转换为最后的数字量,如单次积分型A-D转换器、双积分型A-D转换器等,其特点是工作速度较低,但转换精度可以做得较高,且抗干扰性能强,一般在测试仪表中用得较多。我们将A-D转换器的分类归纳如下:

图12-6 两种量化编码方法的比较

a)只舍不入法 b)有舍有入法

下面将以最常用的两种A-D转换器(逐次逼近型A-D转换器、双积分型A-D转换器)为例,介绍A-D转换器的基本工作原理。

4.逐次逼近型A-D转换器

逐次逼近型A-D转换器又称逐次渐近型A-D转换器,是一种反馈比较型A-D转换器。逐次逼近型A-D转换器进行转换的过程类似于天平称物体重量的过程。天平的一端放着被称的物体,另一端加砝码,各砝码的重量按二进制关系设置,一个比一个重量减半。称重时,把砝码从大到小依次放在天平上,与被称物体比较,如砝码不如物体重,则该砝码予以保留,反之去掉该砝码,多次试探,经天平比较加以取舍,直到天平基本平衡称出物体的重量为止。这样就以一系列二进制码的重量之和表示了被称物体的重量。例如设物体重11克,砝码的重量分别为1克、2克、4克和8克。称重时,物体天平的一端,在另一端先将8克的砝码放上,它比物体轻,该砝码予以保留(记为1),我们将被保留的砝码记为1,不被保留的砝码记为0。然后再将4克的砝码放上,现在砝码总和比物体重了,该砝码不予保留(记为0),依次类推,我们得到的物体重量用二进制数表示为1011。用表12-1表示整个称重过程。

表12-1 逐次逼近法称重物体过程表

利用上述天平称物体重量的原理可构成逐次逼近型A-D转换器。(https://www.xing528.com)

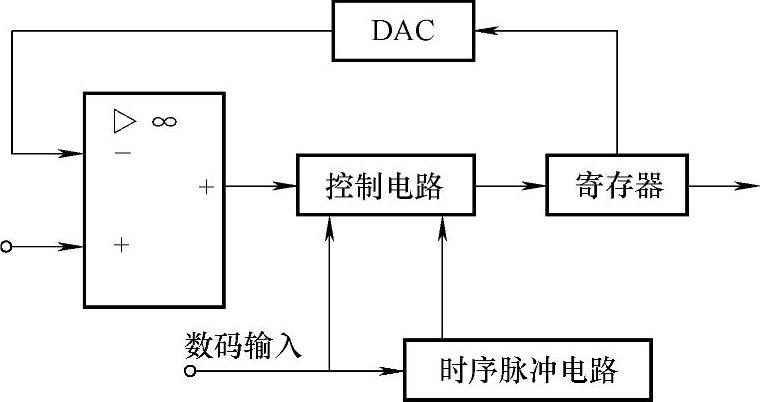

逐次逼近型A-D转换器的结构框图如图12-7所示。包括四个部分:电压比较器、D-A转换器、逐次逼近寄存器和顺序脉冲发生器及相应的控制逻辑。

图12-7 逐次逼近型A-D转换器框图

逐次逼近型A-D转换器是将大小不同的参考电压与输入模拟电压逐步进行比较,比较结果以相应的二进制代码表示。转换开始前先将寄存器清零,即送给D-A转换器的数字量为0,三个输出门G7、G8、G9被封锁,没有输出。转换控制信号有效后(为高电平)开始转换,在时钟脉冲作用下,顺序脉冲发生器发出一系列节拍脉冲,寄存器受顺序脉冲发生器及控制电路的控制,逐位改变其中的数码。首先控制逻辑将寄存器的最高位置为1,使其输出为100……00。这个数码被D-A转换器转换成相应的模拟电压Uo,送到比较器与待转换的输入模拟电压Ui进行比较。若Uo>Ui,说明寄存器输出数码过大,故将最高位的1变成0,同时将次高位置1;若Uo≤Ui,说明寄存器输出数码还不够大,则应将这一位的1保留。数码的取舍通过电压比较器的输出经控制器来完成的。依次类推按上述方法将下一位置1进行比较确定该位的1是否保留,直到最低位为止。此时寄存器里保留下来的数码即为所求的输出数字量。

5.A-D转换器的主要技术指标

(1)分辨率

A-D转换器的分辨率指A-D转换器对输入模拟信号的分辨能力,即A-D转换器输出数字量的最低位变化一个数码时,对应的输入模拟量的变化量。常以输出二进制码的位数n来表示。

式中,uI是输入的满量程模拟电压,n为A-D转换器的位数。显然A-D转换器的位数越多,可以分辨的最小模拟电压的值就越小,也就是说A-D转换器的分辨率就越高。

例如,n=8,uI=5V,A-D转换器的分辨率

当n=10,uI=5V,A-D转换器的分辨率为

由此可知,同样输入情况下,10位ADC的分辨率明显高于8位ADC的分辨率。

实际工作中经常用A-D转换器的位数来表示A-D转换器的分辨率。和D-A转换器一样,A-D转换器的分辨率也是一个设计参数,不是测试参数。

(2)转换速度 转换速度是指完成一次A-D转换所需的时间。转换时间是从模拟信号输入开始,到输出端得到稳定的数字信号所经历的时间。转换时间越短,说明转换速度越高。并联型A-D转换器的转换速度最高,约为数十纳秒;逐次逼近型转换速度次之,约为数十微秒;双积分型A-D转换器的转换速度最慢,约为数十毫秒。

(3)相对精度 在理想情况下,所有的转换点应在一条直线上。相对精度是指A-D转换器实际输出数字量与理论输出数字量之间的最大差值。一般用最低有效位LSB的倍数来表示。如果相对精度不大于LSB的一半,就说明实际输出数字量与理论输出数字量的最大差值不超过LSB的一半。

6.常用集成ADC简介

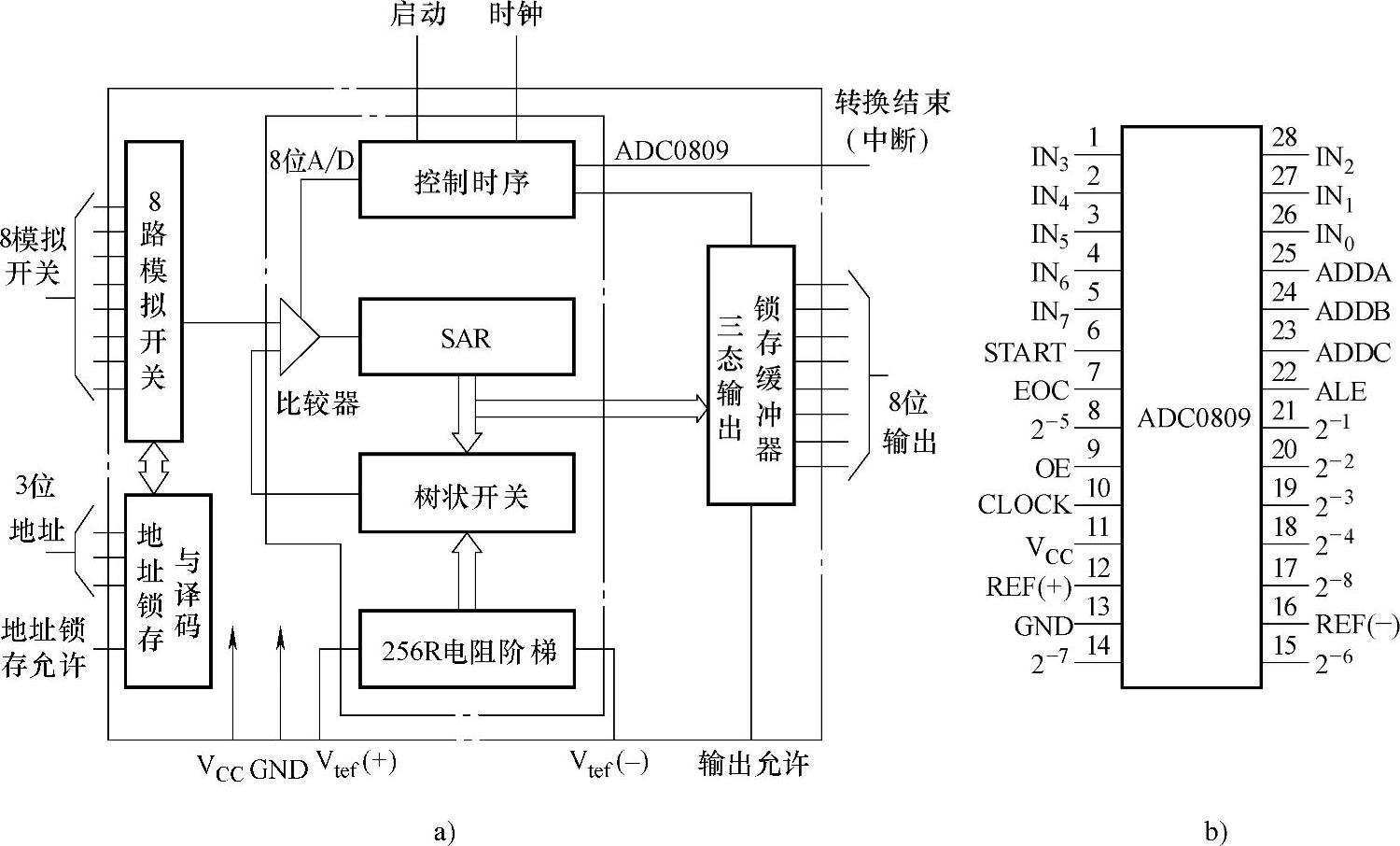

ADC0809是一种逐次比较型ADC。它是采用CMOS工艺制成的8位8通道A-D转换器,采用28只引脚的双列直插封装,其原理和引脚如图12-8所示。

图12-8 ADC0809原理和引脚

a)功能框图 b)引脚图

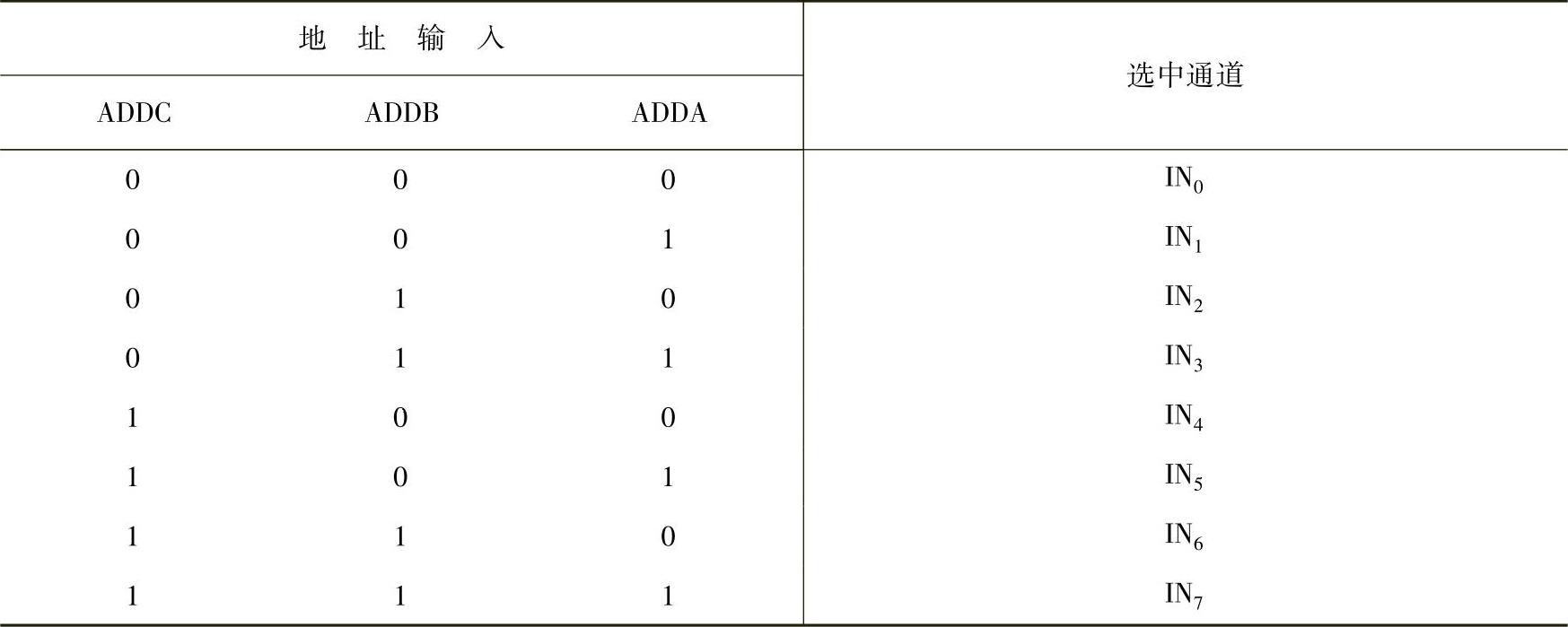

ADC0809有三个主要组成部分:256个电阻组成的电阻阶梯及树状开关、逐次比较寄存器SAR和比较器。电阻阶梯和树状开关是ADC0809的一个特点。另一个特点是,它含有一个8通道单端信号模拟开关和一个地址译码器。地址译码器选择8个模拟信号之一送入ADC进行A-D转换,因此适用于数据采集系统。表12-2为通道选择。

表12-2 通道选择

图12-8b为引脚图。各引脚功能如下:

1)IN0~IN7是八路模拟输入信号;

2)ADDA、ADDB、ADDC为地址选择端;

3)2-8~2-1为变换后的数据输出端;

4)START(6脚)是启动输入端。

5)ALE(22脚)是通道地址锁存输入端。当ALE上升沿到来时,地址锁存器可对AD-DA、ADDB、ADDC锁定。下一个ALE上升沿允许通道地址更新。实际使用中,要求ADC开始转换之前地址就应锁存,所以通常将ALE和TART连在一起,使用同一个脉冲信号,上升沿锁存地址,下降沿则启动转换。

6)OE(9脚)为输出允许端,它控制ADC内部三态输出缓冲器。

7)EOC(7脚)是转换结束信号,由ADC内部控制逻辑电路产生。当EOC=0时表示转换正在进行,当EOC=1表示转换已经结束。因此EOC可作为微机的中断请求信号或查询信号。显然只有当EOC=1以后,才可以让OE为高电平,这时读出的数据才是正确的转换结果。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。