下面介绍TMS320C64x DSP的EDMA控制器的操作。关于事件编码器和参数RAM(Pa-RAM)的操作与TMC320C621x/671x DSP的类似。

1.链接EDMA通道到一个事件

EDMA的任意64个传输完成代码之一可以用于触发另一个EDMA通道传输。为了使能EDMA控制器链接通道到一个事件,用户必须设置TCINT位为1。另外,用户应该设置通道链接使能寄存器(CCERL或CCERH)的相关位,以便触发由TCC指定的下一个通道传输。用户指定的传输完成代码被扩展为一个6位的值TCCM:TCC。OPT寄存器中的4位TCC是传输完成代码的低位,而2位TCCM是最高位。例如,如果传输完成代码(TCCM:TCC)为010001b(TCCM=01并且TCC=0001,并且为EDMA通道4指定了CCERL[17]=1时,只要通道4的TCINT=1,则通道4传输完成后会启动由EDMA通道17指定的下一个传输。与TMS320C621x/C671x EDMA不同,只有通道链使能寄存器的相关位,事件寄存器才会捕获TMS320C64x EDMA上的事件位。

当一个块的中间传输完成时,OPT寄存器的交替传输完成中(ATCINT)位和交替传输完成代码(ATCC)位允许TMS320C64x EDMA执行通道链接。交替传输中断的功能与传输完成中断的功能类似。交替传输完成代码链接不会影响连接操作。

当交替传输完成链接被使能时,则在当前通道的每个中间传输完成时,下一个EDMA通道会被同步(当前通道的ATCC值设定)。当整个通道传输完成时,只要传输完成链接被使能,则产生传输完成链接。交替传输完成链接不会应用于2D块同步传输,因为在这种模式下没有任何中间传输。在每进行一次传输请求时(而不是每个块一次),交替传输链接允许一个通道触发另一个通道。

为了使能交替传输完成链接,需要配置EDMA通道参数如下:

1)设置OFT寄存器的ATCINT=1。

2)设定ATCC的值为链接中的下一个EDMA通道。

3)设置通道链接使能寄存器(CCER[ATCC])相关位。

2.外设器件传输

TMS320C64x EDMA支持外设传输模式(PDT),从而为共享数据引脚的外部器件和外部存储器之间传输大量的数据提供了一个有效的方式。在通常的操作中,这种类型的传输要求在外部源的一次EMIF读之后,紧跟一次对外部目的写操作。当PDT被使能时,数据直接被外部源驱动,并且通过相同的数据总线写到外部目的。

按照EMIF上的存储器类型对PDT传输进行分类。PDT写是指从外设到存储器(存储器是物理可写的)的传输。为了使能从一个外设源到一个外部存储器目的的PDT写,应该设置OPT寄存器的PDTS位为1。

PDT读是指从存储器(存储器是物理可读的)到外设的传输。为了使能从一个外部存储器源到一个外设目的的PDT读,应该设置OPT寄存器的PDTD位为1。

PDT写和PDT读是相互排斥的,也就是说,PDTS和PDTD不能同时设置为1。

3.资源仲裁和优先级处理

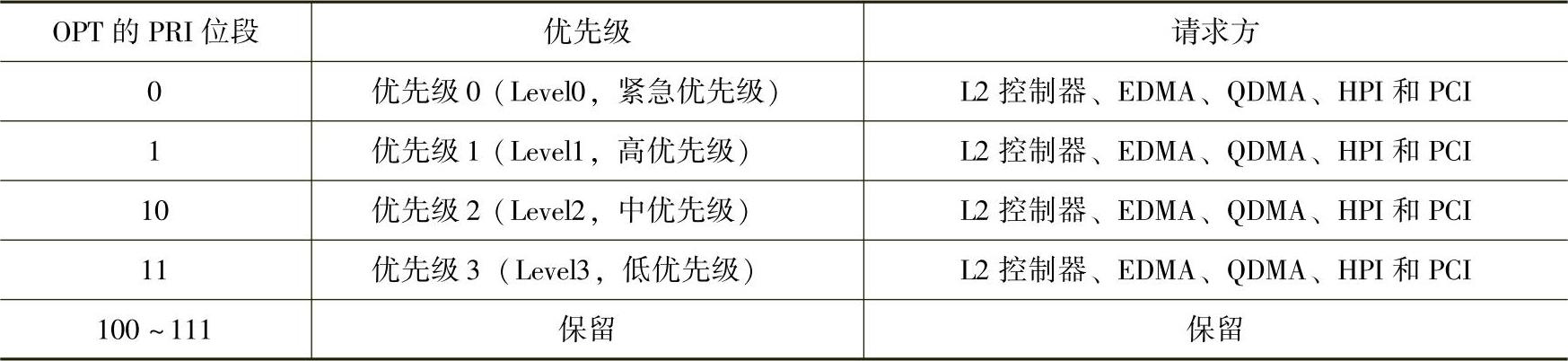

EDMA通道具有可编程序的优先级。OPT寄存器的PRI位指定了优先级。表3-23列出了TMS320C64x DSP的可编程序的数据请求优先级。

表3-23 TMS320C64x DSP的可编程序的数据请求优先级

(https://www.xing528.com)

(https://www.xing528.com)

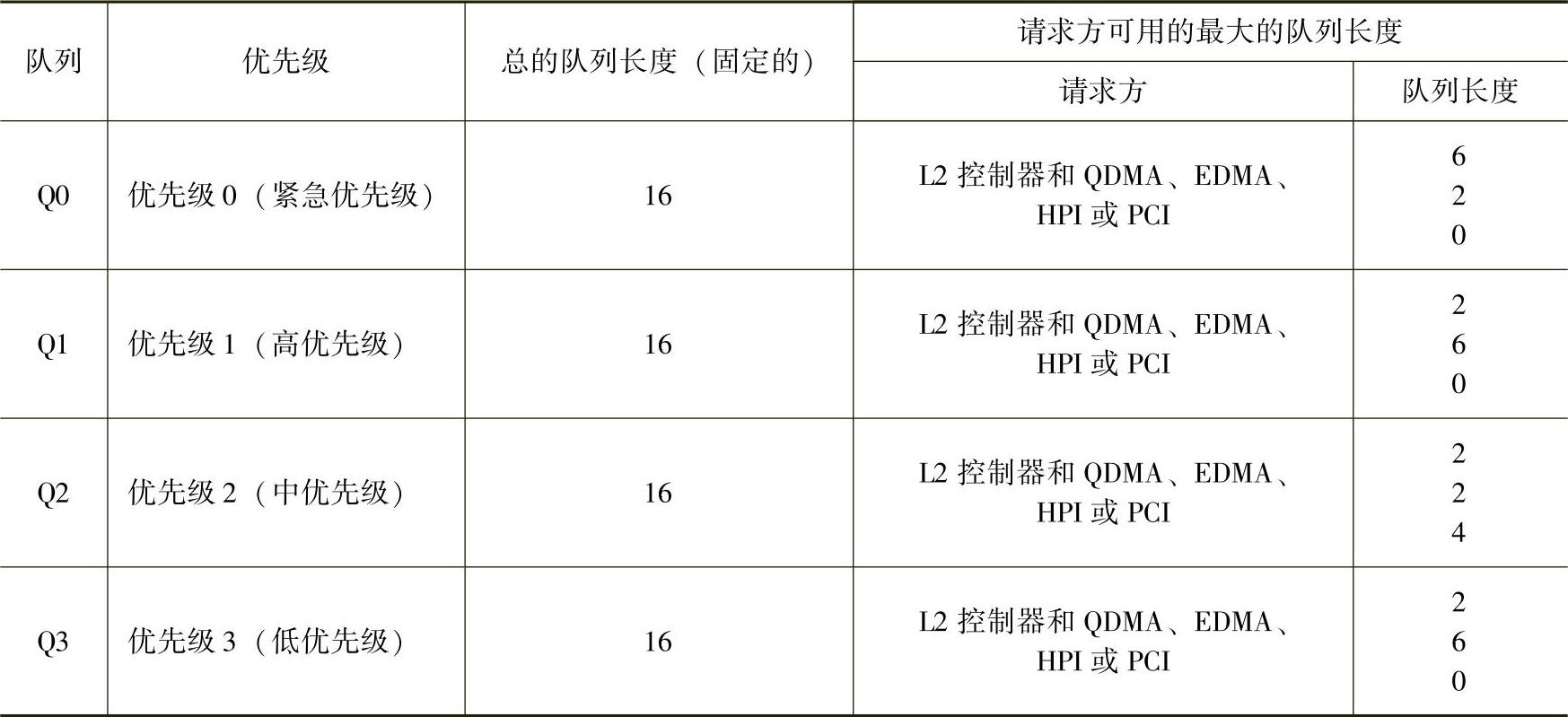

4.传输请求队列长度

TMS320C64xEDMA具有4个传输请求队列:Q0、Q1、Q2和Q3。不同优先级传输请求(OPT中的PRI位段)被归类到Q0、Q1、Q2和Q3中,见表3-24。

表3-24 TMS320C64x DSP的传输请求队列

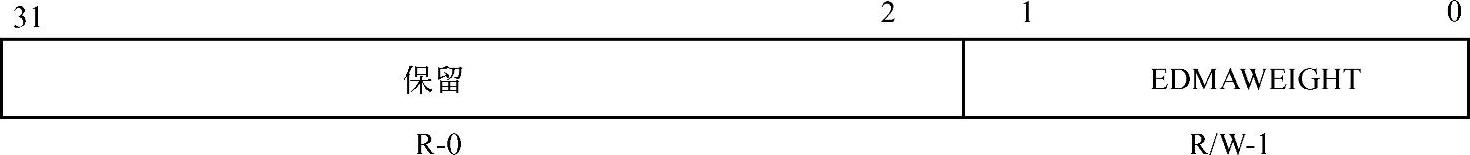

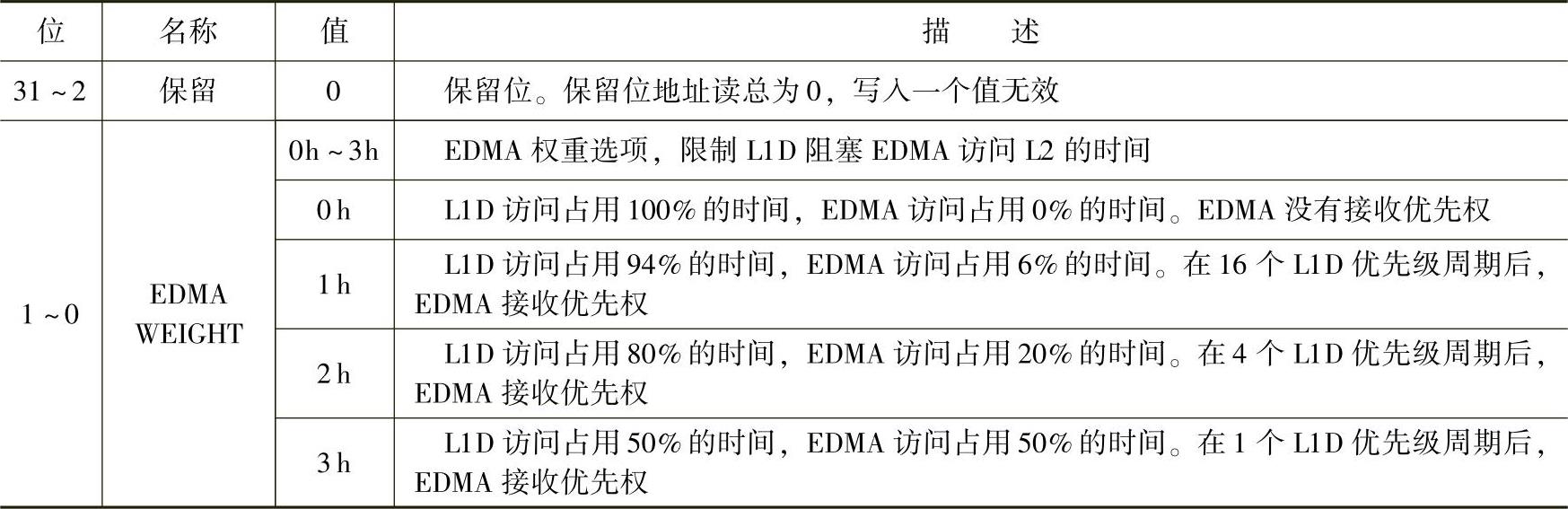

5.EDMA访问L2控制

TMS320C64x DSP具有一个L2EDMA访问控制寄存器(EDMA WEIGHT),位于L2高速缓存寄存器存储器映射区。该寄存器可以控制EDMA和L1D访问L2的优先级。通过限制L1D阻塞EDMA访问L2的时间,EDMA WEIGHT可以临时增强EDMA访问。如果来自CPU的数据还没有到达L1 D,但是已经到达L2高速缓存或L2 SDRAM,此时与来自CPU的数据产生竞争时,才应用这个优先级的增强。EDMA WEIGHT让用户控制每隔多久给予一次优先级增强。当EDMA优先级被提升时,在优先级返回到CPU数据之前允许完成一次访问。EDMAWEIGHT如图3-20所示,各位段的描述见表3-25。

图3-20 L2EDMA访问控制寄存器(EDMA WEIGHT)

表3-25 EDMA WEIGHT描述

6.EDMA控制寄存器

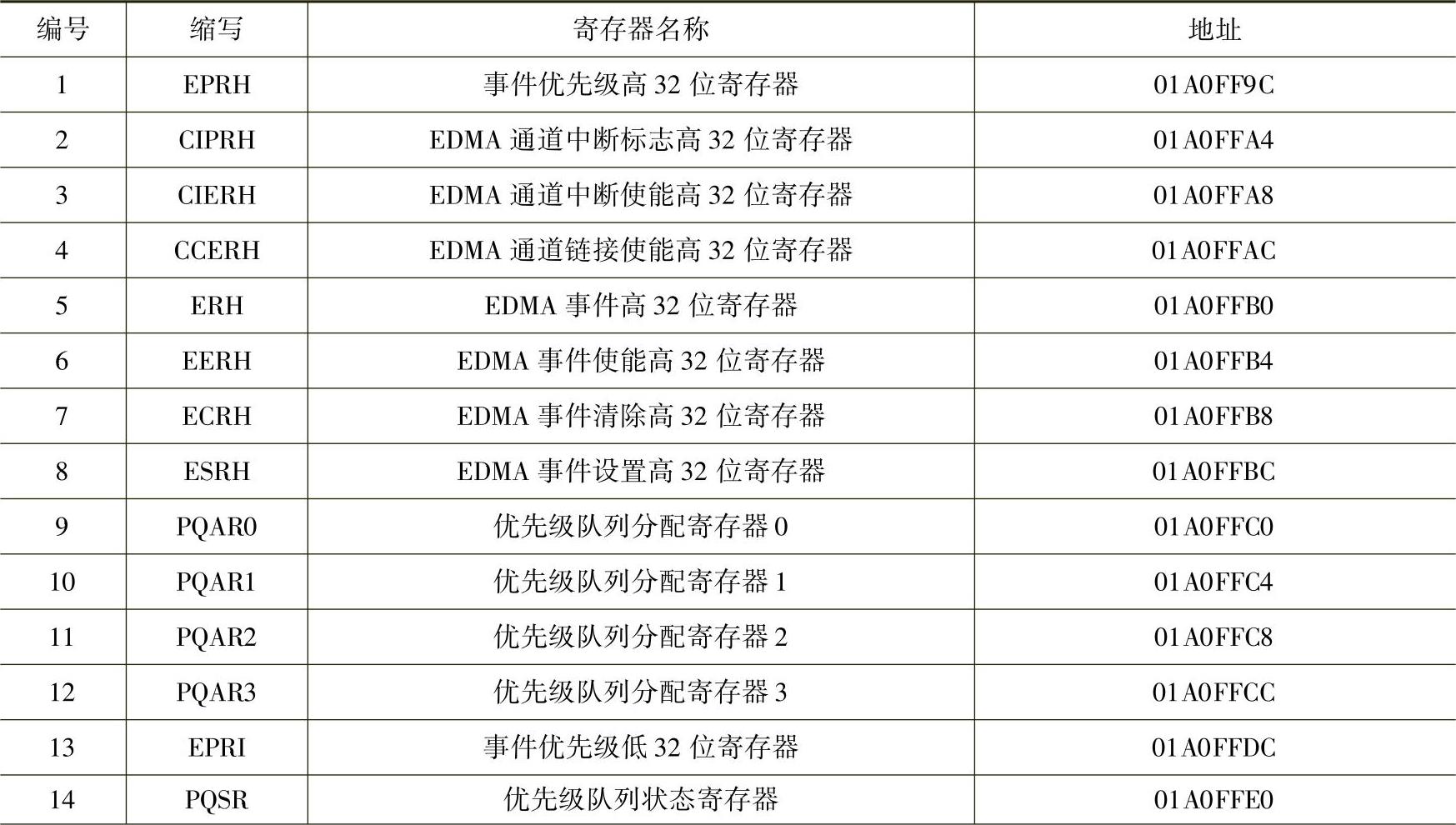

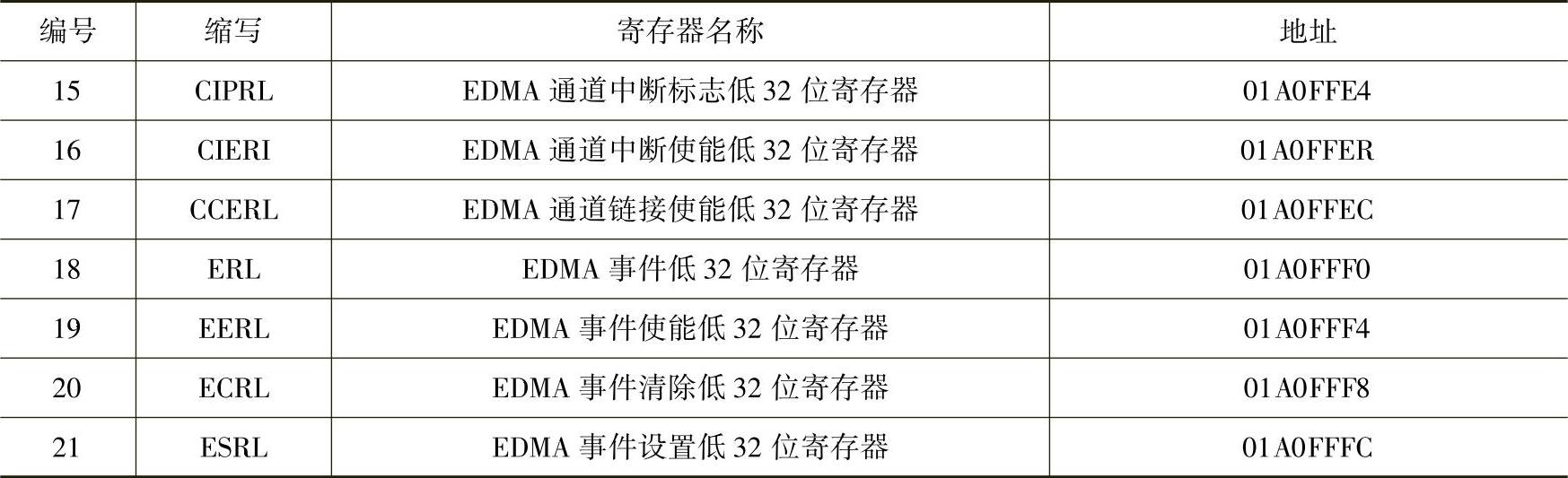

EDMA中64个通道都有与其相关的一个专门的同步事件。这些事件触发与该通道相关的数据传输。执行各种事件处理的控制寄存器见表3-26。关于这些寄存器的详细描述可参考TI的相关手册。

表3-26 执行各种事件处理的控制寄存器

(续)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。