近二十年来,国外厂商推出了多款性能优良的DDS芯片,尤其是美国Analog Devices公司(简称AD公司)推出的DDS芯片,品种多,应用广泛。其DDS系列芯片主要包括:AD983X系列低功耗低频率型芯片、AD985X系列高性能型芯片、针对AD985X高功耗特性改良的AD995X系列低功耗高性能型芯片以及近年来最新推出的具有更高时钟频率和更好性能的AD991X系列芯片。当前性能指标最高的是AD9914芯片,其内部时钟频率高达3.5 GHz,具有32位频率控制字、16位相位调谐控制字以及12位幅度控制字,能合成输出1.4 GHz频率捷变正弦波,芯片本身具有多种工作模式可选。本节主要介绍AD9951芯片的功能及应用。

1)AD9951芯片的内部组成

AD9951是美国AD公司于2002年推出的一款高性能低功耗的DDS芯片,它内部包含可编程DDS内核和DAC,能实现全数字程控的频率合成器和时钟发生器。

该芯片具有400 MHz的内部时钟,集成了14位的DAC,具有32位的频率控制字,可以产生最高频率为200 MHz的正弦波信号。芯片采用1.8 V单电源供电,在400 MHz工作时钟下,功耗为162 mW。其芯片内部组成如图2-12所示。

图2-12 AD995l的内部组成

时钟倍频器可对外部输入的差分时钟信号进行4倍到20倍的倍频。倍频器输出的时钟信号为整个芯片提供工作时钟,同时也经过四分频后输出SYNC-CLK信号,SYNCCLK信号可提供给其他芯片同步用。外部控制器通过I/O口与芯片相连,将相关的控制字写入控制寄存器,控制寄存器是一个暂存寄存器,在IO-UPDATE的上升沿期间,将其寄存的内容写入I/O寄存器中。在时序与控制逻辑单元的作用下,控制DDS内核输出相应频率、幅度的正弦信号。通过14位的DAC,输出差分的IOUT和IOUTB信号。DDS内核中包括相位累加器和正弦查找表ROM。对输入的32位频率控制字,截取其高19位送入正弦查找表中寻址。每次从ROM中读出的14位数据与幅度信息进行整合后,送入1.4位的DAC中,经外接低通滤波器,就可以得到频谱纯净的正弦波信号。

2)AD9951的程序控制

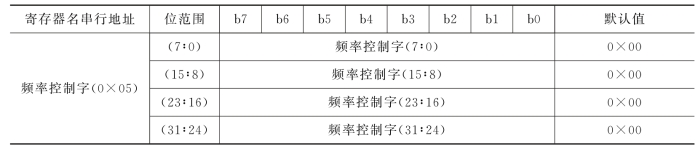

AD9951内部有6组寄存器,寄存器的地址为0x00—0x05,分别对应控制功能寄存器1、控制功能寄存器2、幅度比例因子寄存器、幅度斜率寄存器、频率控制字寄存器以及相位偏移寄存器。每个寄存器由32位、24位、16位或8位组成不等。通过对寄存器中的相关位进行设置,可实现相应的功能。受篇幅所限,这里仅介绍与输出频率相关的寄存器,包括控制功能寄存器2中的bit7~bit3以及32位的频率控制字寄存器。控制功能寄存器2中的bit7~bit3决定芯片内部时钟倍频器的倍数:若bit7~bit3这五位的值在0x00~0x03之间,则旁路倍频器,即工作时钟(采样时钟),与输入时钟频率相等;若这五位值介于0x04~0x14之间,则对输入时钟信号进行4倍~20倍的倍频。假设采用有源晶振作为系统的输入时钟,有源晶振的频率为20 MHz,若设置该五位为0x14(20倍的倍频),则S片工作在20 MHz×20=400 MHz的频率。频率控制字寄存器决定DDS芯片输出信号的频率,频率控制字格式如表2-2所示。

表2-2 频率控制字格式

频率控制字K可由输出目标频率f0、采样频率fc以及正弦查阅表的地址位数n计算出,K=f0×2n/fc。如果计算时出现小数,应进行相应的舍入,并将十进制值转换为二进制,即可得到要设置的32位频率控制字。

AD9951通过SPI串行接口对内部寄存器进行操作。在操作寄存器时,依照SPI时序,首先拉低片选信号CS,选通芯片,然后,在时钟(SCLK)的下降沿写入相应的每一位,先依次写入八位串行地址,再依次写入相应的数据,数据的长度由相应寄存器的位宽决定。完成操作后,将CS拉高,结束操作,相应寄存器内的信息即被设置。待每次需要修改的寄存器内容写入完毕后,按照时序要求拉高I/O-UPDATE引脚的信号,即可完成相应寄存器内容的更新。(https://www.xing528.com)

3)AD9951的应用

AD9951应用广泛,下面给出三个典型应用实例。

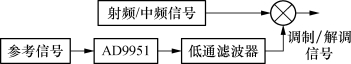

图2-13中,使用AD9951产生同步的本振信号对输入的射频或中频信号进行上混频或下混频,得到相应的调制/解调信号。

图2-13 同步本振用于上混频/下混频

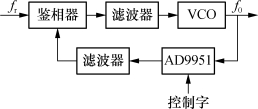

图2-14 AD9951取代了传统PLL

由于DDS有较高的频率分辨率,并且不受分频系数N必须为整数的限制,因此,可以在不降低fr的情况下获得较高的分辨率。图2-14为AD9951取代了传统PLL。

4)其他DDS芯片

目前市场上使用的DDS芯片种类众多,不同型号的DDS芯片在采样率、控制字位数、输出信号最高频率、寄存器设置、控制接口与控制时序以及附带的一些功能上有所差异。

不同型号的DDS芯片集成了一些不同的功能,供用户选择与使用。如AD9852、AD9854内部集成了正交调制器,芯片本身可以输出两路正交信号,同时具有调制输出模式,可以输出FSK、BPSK、PSK、CHIRP、AM等调制信号。AD9956中有相位调制功能。AD9910中集成有1024字32位的可编程波形RAM以及数字斜坡发生器(DRG)。在很多DDS芯片中,还集成有高速比较器,将整形后的正弦波进行比较放大,输出边沿抖动很小的脉冲信号,可用于其他数字系统的时钟信号。部分DDS芯片提供了与扫频控制相关的寄存器,可设置DDS工作在扫频输出模式,并可控制扫频的间隔与步进频率等。此外,Xilinx、Ahera等FPGA厂商也提供了可在其FPGA中直接调用的IP(知识产权)核,实现DDS功能。

除了专用的DDS芯片以外,还有一些芯片中也集成了DDS发生器,用于完成特定的功能。如AD5933、AD5934复阻抗测量芯片内部集成了DDS发生器作为激励信号,经过片上DSP进行DFT运算后,将每个频率值对应的实部与虚部数据存入寄存器中,用户通过I2C接口访问数据,实现对复阻抗的测量。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。