在通常情况下,ADC的逐次比较转换电路要达到最大精度时,需要50~200kHz之间的采样时钟。在要求转换精度低于10位的情况下,ADC的采样时钟可以高于200kHz,以获得更高的采样率。

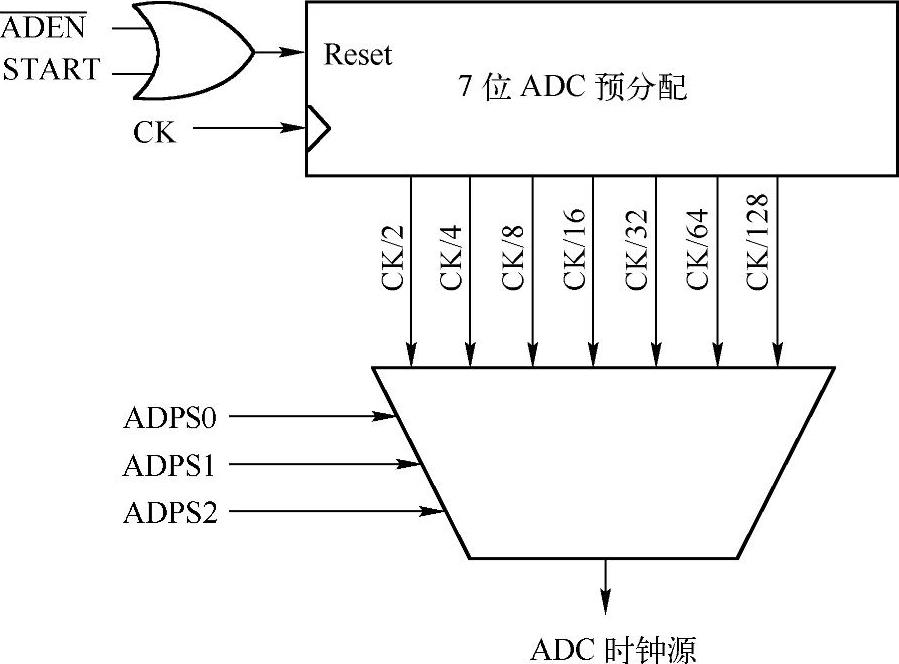

图9-3 带预分频器的ADC时钟源

ADC模块中包含一个预分频器的ADC时钟源,如图9-3所示。它可以对大于100kHz的系统时钟进行分频,以获得合适的ADC时钟提供给ADC使用。预分频器的分频系数由ADCSRA寄存器中的ADPS位设置。一旦寄存器ADCSRA中的ADEN位置“1”(ADC开始工作),预分频器就启动开始计数。ADEN位为“1”时,预分频器将一直工作;ADEN位为“0”时,预分频器一直处在复位状态。

AVR的ADC完成一次转换的时间如表9-7所示。从表中可以看出,完成一次ADC转换通常需要13~14个ADC时钟。而启动ADC开始第一次转换到完成的时间需要25个ADC时钟,这是因为要对ADC单元的模拟电路部分进行初始化。

表9-7 ADC转换和采样保持时间(https://www.xing528.com)

当ADCSRA寄存器中的ADSC位置位,启动ADC转换时,A/D转换将在随后ADC时钟的上升沿开始。一次正常的A/D转换开始时,需要1.5个ADC时钟周期的采样保持时间(ADC首次启动后需要13.5个ADC时钟周期的采样保持时间)。当一次A/D转换完成后,转换结果写入ADC数据寄存器,ADIF(ADC中断标志位)将被置位。在单次转换模式下,ADSC也同时被清零。用户程序可以再次置位ADSC位,新的一次转换将在下一个ADC时钟的上升沿开始。

当ADC设置为自动触发方式时,触发信号的上升沿将启动一次ADC转换。转换完成的结果将一直保持到下一次触发信号的上升沿出现,然后开始新的一次ADC转换。这就保证了使ADC每隔一定的时间间隔进行一次转换。在这种方式下,ADC需要2个ADC时钟周期的采样保持时间。

在自由连续转换模式下,一次转换完毕后马上开始一次新的转换,此时,ADSC位一直保持为“1”。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。