PS/2 通信协议是一种双向同步串行通信协议。通信的两端通过Clock(时钟脚)同步,并通过Data(数据脚)交换数据。任何一方如果想抑制另外一方通信时,只需要把Clock(时钟脚)拉到低电平。如果是PC 机和PS/2 键盘间的通信,则PC 机必须做主机,也就是说,PC 机可以抑制PS/2 键盘发送数据,而PS/2 键盘则不会抑制PC 机发送数据。一般两设备间传输数据的最大时钟频率是33 kHz,大多数PS/2 设备工作在10~20 kHz。推荐值在15 kHz 左右,也就是说,Clock(时钟脚)高、低电平的持续时间都为40 μs。每一数据帧包含11~12 个位,具体含义见表5.8。

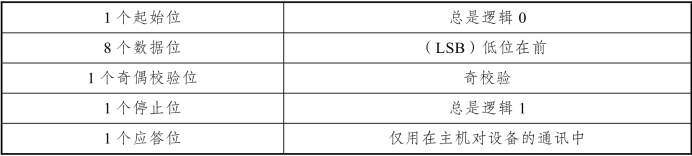

表5.8 数据帧格式

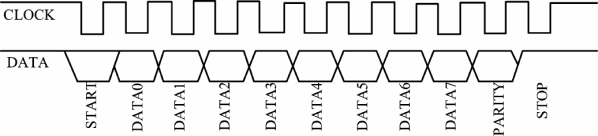

表5.8 中,如果数据位中1 的个数为偶数,校验位就为1;如果数据位中1 的个数为奇数,校验位就为0;总之,数据位中1 的个数加上校验位中1 的个数总为奇数,因此总进行奇校验。PS/2 设备到PC 机的通信时序如图5.21 所示。(https://www.xing528.com)

PS/2 设备的Clock(时钟脚)和Data 数据脚都是集电极开路的,平时都是高电平。当PS/2 设备等待发送数据时,它首先检查Clock(时钟脚)以确认其是否为高电平。如果是低电平,则认为是PC 机抑制了通信,此时它必须缓冲需要发送的数据直到重新获得总线的控制权(一般PS/2 键盘有16 个字节的缓冲区,而PS/2 鼠标只有一个缓冲区仅存储最后一个要发送的数据)。如果Clock(时钟脚)为高电平,PS/2 设备便开始将数据发送到PC 机。一般都是由PS/2 设备产生时钟信号。发送时一般都是按照数据帧格式顺序发送。其中数据位在Clock(时钟脚)为高电平时准备好,在Clock(时钟脚)的下降沿被PC 机读入。

图5.21 PS/2 设备到PC 机的通信时序

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。